SPI匯流排協議及SPI時序圖詳解

SPI,是英語Serial Peripheral Interface的縮寫,顧名思義就是序列外圍裝置介面。SPI,是一種高速的,全雙工,同步的通訊匯流排,並且在晶片的管腳上只佔用四根線,節約了晶片的管腳,同時為PCB的佈局上節省空間,提供方便,正是出於這種簡單易用的特性,現在越來越多的晶片集成了這種通訊協議。

SPI是一個環形匯流排結構,由ss(cs)、sck、sdi、sdo構成,其時序其實很簡單,主要是在sck的控制下,兩個雙向移位暫存器進行資料交換。

上升沿傳送、下降沿接收、高位先發送。

上升沿到來的時候,sdo上的電平將被髮送到從裝置的暫存器中。

下降沿到來的時候,sdi上的電平將被接收到主裝置的暫存器中。

假設主機和從機初始化就緒:並且主機的sbuff=0xaa (10101010),從機的sbuff=0x55 (01010101),下面將分步對spi的8個時鐘週期的資料情況演示一遍(假設上升沿傳送資料)。

---------------------------------------------------

這樣就完成了兩個暫存器8位的交換,上面的0--1表示上升沿、1--0表示下降沿,sdi、 sdo相對於主機而言的。根據以上分析,一個完整的傳送週期是16位,即兩個位元組,因為,首先主機要傳送命令過去,然後從機根據主機的名準備資料,主機在下一個8位時鐘週期才把資料讀回來。

SPI匯流排是Motorola公司推出的三線同步介面,同步序列3線方式進行通訊:一條時鐘線SCK,一條資料輸入線MOSI,一條資料輸出線MISO;用於 CPU與各種外圍器件進行全雙工、同步序列通訊。

SPI主要特點有:可以同時發出和接收序列資料;可以當作主機或從機工作;提供頻率可程式設計時鐘;傳送結束中斷標誌;寫衝突保護;匯流排競爭保護等。

SPI匯流排有四種工作方式(SP0, SP1, SP2, SP3),其中使用的最為廣泛的是SPI0和SPI3方式。

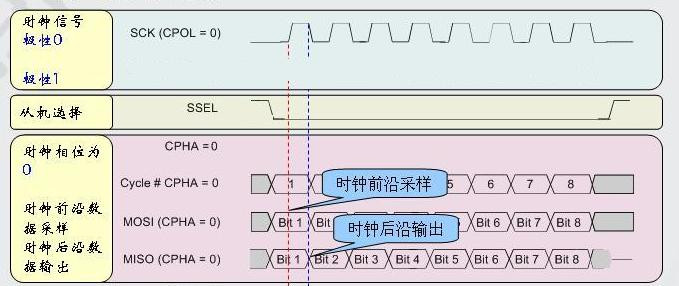

SPI模組為了和外設進行資料交換,根據外設工作要求,其輸出串行同步時鐘極性和相位可以進行配置,時鐘極性(CPOL)對傳輸協議沒有重大的影響。如果CPOL=0,串行同步時鐘的空閒狀態為低電平;如果CPOL=1,串行同步時鐘的空閒狀態為高電平。時鐘相位(CPHA)能夠配置用於選擇兩種不同的傳輸協議之一進行資料傳輸。如果 CPHA=0,在串行同步時鐘的第一個跳變沿(上升或下降)資料被取樣;如果CPHA=1,在串行同步時鐘的第二個跳變沿(上升或下降)資料被取樣。 SPI主模組和與之通訊的外設音時鐘相位和極性應該一致。

SPI時序圖詳解-SPI介面在模式0下輸出第一位資料的時刻

SPI介面在模式0下輸出第一位資料的時刻

SPI介面有四種不同的資料傳輸時序,取決於CPOL和CPHL這兩位的組合。圖1中表現了這四種時序,

時序與CPOL、CPHL的關係也可以從圖中看出。

圖1

CPOL是用來決定SCK時鐘訊號空閒時的電平,CPOL=0,空閒電平為低電平,CPOL=1時,

空閒電平為高電平。CPHA是用來決定取樣時刻的,CPHA=0,在每個週期的第一個時鐘沿取樣,

CPHA=1,在每個週期的第二個時鐘沿取樣。

由於我使用的器件工作在模式0這種時序(CPOL=0,CPHA=0),所以將圖1簡化為圖2,

只關注模式0的時序。

圖2

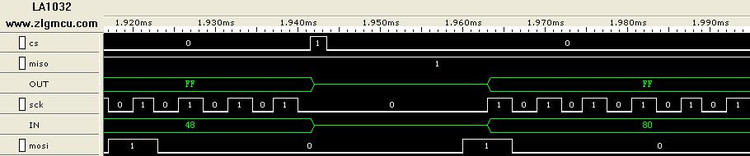

我們來關注SCK的第一個時鐘週期,在時鐘的前沿取樣資料(上升沿,第一個時鐘沿),

在時鐘的後沿輸出資料(下降沿,第二個時鐘沿)。首先來看主器件,主器件的輸出口(MOSI)輸出的資料bit1,

在時鐘的前沿被從器件取樣,那主器件是在何時刻輸出bit1的呢?bit1的輸出時刻實際上在SCK訊號有效以前,

比 SCK的上升沿還要早半個時鐘週期。bit1的輸出時刻與SSEL訊號沒有關係。再來看從器件,

主器件的輸入口MISO同樣是在時鐘的前沿取樣從器件輸出的bit1的,那從器件又是在何時刻輸出bit1的呢。

從器件是在SSEL訊號有效後,立即輸出bit1,儘管此時SCK訊號還沒有起效。關於上面的主器件

和從器件輸出bit1位的時刻,可以從圖3、4中得到驗證。

圖3

注意圖3中,CS訊號有效後(低電平有效,注意CS下降沿後發生的情況),故意用延時程式

延時了一段時間,之後再向資料暫存器寫入了要傳送的資料,來觀察主器件輸出bit1的情況(MOSI)。

可以看出,bit1(值為1)是在SCK訊號有效之前的半個時鐘週期的時刻開始輸出的(與CS訊號無關),

到了SCK的第一個時鐘週期的上升沿正好被從器件取樣。

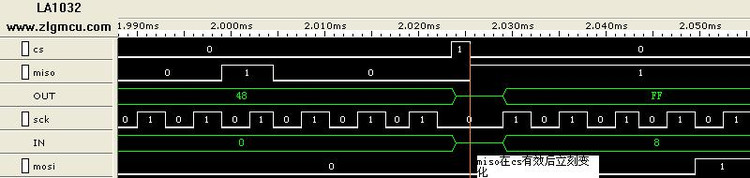

圖4

圖4中,注意看CS和MISO訊號。我們可以看出,CS訊號有效後,從器件立刻輸出了bit1(值為1)。

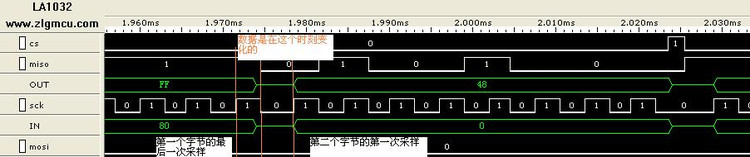

通常我們進行的spi操作都是16位的。圖5記錄了第一個位元組和第二個位元組間的相互銜接的過程。

第一個位元組的最後一位在SCK的上升沿被取樣,隨後的SCK下降沿,從器件就輸出了第二個位元組的第一位。

SPI匯流排協議介紹(介面定義,傳輸時序)

一、技術性能

SPI介面是Motorola 首先提出的全雙工三線同步序列外圍介面,採用主從模式(Master Slave)架構;支援多slave模式應用,一般僅支援單Master。

時鐘由Master控制,在時鐘移位脈衝下,資料按位傳輸,高位在前,低位在後(MSB first);SPI介面有2根單向資料線,為全雙工通訊,目前應用中的資料速率可達幾Mbps的水平。

-------------------------------------------------------

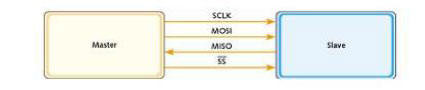

二、介面定義

SPI介面共有4根訊號線,分別是:裝置選擇線、時鐘線、序列輸出資料線、序列輸入資料線。

(1)MOSI:主器件資料輸出,從器件資料輸入

(2)MISO:主器件資料輸入,從器件資料輸出

(3)SCLK :時鐘訊號,由主器件產生

(4)/SS:從器件使能訊號,由主器件控制

-------------------------------------------------------

三、內部結構

四、傳輸時序SPI介面在內部硬體實際上是兩個簡單的移位暫存器,傳輸的資料為8位,在主器件產生的從器件使能訊號和移位脈衝下,按位傳輸,高位在前,低位在後。如下圖所示,在SCLK的下降沿上資料改變,上升沿一位資料被存入移位暫存器。

SPI介面沒有指定的流控制,沒有應答機制確認是否接收到資料。

相關推薦

SPI匯流排協議及SPI時序圖詳解

SPI,是英語Serial Peripheral Interface的縮寫,顧名思義就是序列外圍裝置介面。SPI,是一種高速的,全雙工,同步的通訊匯流排,並且在晶片的管腳上只佔用四根線,節約了晶片的管腳,同時為PCB的佈局上節省空間,提供方便,正是出於這種簡單易用的特性,現在

SPI時序圖詳解-SPI介面在模式0下輸出第一位資料的時刻

SPI介面在模式0下輸出第一位資料的時刻 SPI介面有四種不同的資料傳輸時序,取決於CPOL和CPHL這兩位的組合。圖1中表現了這四種時序, 時序與CPOL、CPHL的關係也可以從圖中看出。 圖1 CPOL是用來決定SCK時鐘訊號空閒時的電平,CPOL=0,空閒電平為低電平,CPOL=1時, 空閒電平

UML之時序圖詳解

原文連結:https://blog.csdn.net/fly_zxy/article/details/80911942 什麼是時序圖 時序圖(Sequence Diagram),又名序列圖、循序圖,是一種UML互動圖。它通過描述物件之間傳送訊息的時間順序顯示多個物件之間的動態協作。 讓我們來看一看vis

IP協議及IP資料包詳解

回憶一下網路層的主要功能:通過TCP或者UDP協議繪製網路地圖,資料包選取合適的路徑進行傳輸(網路層基本單位 : 資料包 Package) (1)編址(目標端的IP地址),資料傳輸的過程當中就必須表明

SPI匯流排協議概述

一.概述 SPI(serial peripheral interface)是一種同步序列通訊協議,由一個主裝置和一個或多個從裝置組成,主裝置啟動與從裝置的同步通訊,從而完成資料的交換。SPI是一種高速全雙工同步通訊匯流排,標準的

深度解析:IIC和SPI匯流排協議,有何不同?

[主從裝置]必須使用相同的工作引數——SCLK、CPOL 和 CPHA,才能正常工作。如果有多個[從裝置],並且它們使用了不同的工作引數,那麼[主裝置]必須在讀寫不同[從裝置]間重新配置這些引數。以上SPI匯流排協議的主要內容。SPI不規定最大傳輸速率,沒有地址方案;SPI也沒規定通訊應答機制,沒有規定流控制

關於I2C和SPI匯流排協議

關於I2C和SPI匯流排協議IICvs SPI 現今,在低端數字通訊應用領域,我們隨處可見IIC (Inter-Integrated Circuit) 和 SPI (Serial Peripheral Interface)的身影。原因是這兩種通訊協議非常適合近

SPI匯流排協議介紹

SPI介面時鐘配置心得:在主裝置這邊配置SPI介面時鐘的時候一定要弄清楚從裝置的時鐘要求,因為主裝置這邊的時鐘極性和相位都是以從裝置為基準的。因此在時鐘極性的配置上一定要搞清楚從裝置是在時鐘的上升沿還是下降沿接收資料,是在時鐘的下降沿還是上升沿輸出資料。

[轉]關於I2C和SPI匯流排協議的優缺點

關於I2C和SPI匯流排協議 IICvs SPI 現今,在低端數字通訊應用領域,我們隨處可見IIC (Inter-Integrated Circuit) 和 SPI (Serial Peripheral Interface)的身影。原

SPI匯流排協議學習筆記

最近正在學習SPI匯流排協議,看了很多網上的相關內容,覺得有必要整理一下,既可以鞏固自己的學習內容,也可以和大家分享,方便以後的學習。 先來對SPI有個大概的瞭解,如下: SPI是英語Serial Peripheral Interface的縮寫,也就是序列外圍裝置介面。S

IIC和SPI匯流排協議

IICvs SPI 現今,在低端數字通訊應用領域,我們隨處可見IIC (Inter-Integrated Circuit) 和 SPI (Serial Peripheral Interface)的身影。原因是這兩種通訊協議非常適合近距離低速晶片間通訊。Ph

TCP狀態轉換圖詳解 tcp協議講解

在前面,已經介紹了TCP協議的三路握手和四次揮手。如下圖所示,TCP通訊過程包括三個步驟:建立TCP連線通道(三次握手)、資料傳輸、斷開TCP連線通道(四次揮手)。 &n

軟體開發,標準化流水線式開發的實施構想 Internet 服務匯流排 嵌入式通用行業應用平臺的靈魂和搭建 快速原型開發模式在實際開發過程中的應用 公用物件請求代理(排程)程式體系結構(CORBA) UML軟體設計基礎(UML圖詳解) (篇01)企業如何軟體商業化? (篇02)企業如何軟體商業化? 在

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

SCSI匯流排和協議以及SAN儲存網路詳解

在講解SAN儲存網路之前,我想先在物理層面為大家講解一下乙太網網絡卡,FC-HBA卡(光纖網絡卡),iSCSi-HBA卡的區別。 乙太網卡:就是我們平常見到的電腦或伺服器上面的網絡卡,它傳輸的是IP協議,通過

TCP狀態轉換圖詳解 tcp協議講解

在前面,已經介紹了TCP協議的三路握手和四次揮手。如下圖所示,TCP通訊過程包括三個步驟:建立TCP連線通道(三次握手)、資料傳輸、斷開TCP連線通道(四次揮手)。

UML圖詳解(七)互動圖(時序圖與協作圖)

一、概念 互動圖描述物件之間的動態合作關係以及合作過程中的行為次序。 互動圖常常用來描述一個用例的行為,顯示該用例中所涉及的物件以及這些物件之間的訊息傳遞情況,即一個用例的實現過程。 互動圖有順序圖和協作圖兩種形式。 時序圖中描述物件按照時間順序的訊息交換。 協作圖著

STM32利用SPI讀寫SD卡的程式詳解

SD卡的讀寫驅動程式是運用FATFS的基礎,學了FATFS就可以在SD卡上建立資料夾及檔案了。我們先從main檔案瞭解一下程式的執行流程int main(void) { u16 i; USART1_Config(); for(i=0;i<1536;i++) send_data[

STM32值SPI的使用及SPI初始化注意事項

在STM32F10x系列晶片中,雖然所擁有的SPI同步串列埠數量不相同,但是初始化的方法都是一樣的。其中使用SPI時候我們回憶GPIO的使用,要注意6點,我們這裡主要講解一點。 根據系統對該不同功能的要求,初始化不同功能外設,初始化GPIO,初始化SPI同步串列埠裝置就會比

Android開發最強模擬器Genymotion的安裝及使用教程。附註釋圖詳解

前沿 呵呵,筆者第一次在公開的部落格網站寫心得,想讓自己的Android開發生涯留下點足跡,並且為自己做點筆記,如果該文章能幫到廣大的Android小白朋友最好了(其實我也是一小白,(●'◡'●)),好的,不扯了,進入主題 首先介紹一下Genymotion模擬器,筆者也是

ER圖詳解及例項解析

ER圖分為實體、屬性、關係三個核心部分。 實體是長方形,屬性是橢圓形,關係為菱形。 實體(entity): 即資料模型中的資料物件(即資料表),用長方體來表示,每個實體都有自己的實體成員(entity member)或者說實體物件(entity instance),例如