Verilog設計的原則和技巧和IP核的使用

FPGA設計原則

1、面積與速度折中(Area&speed tradeoff)

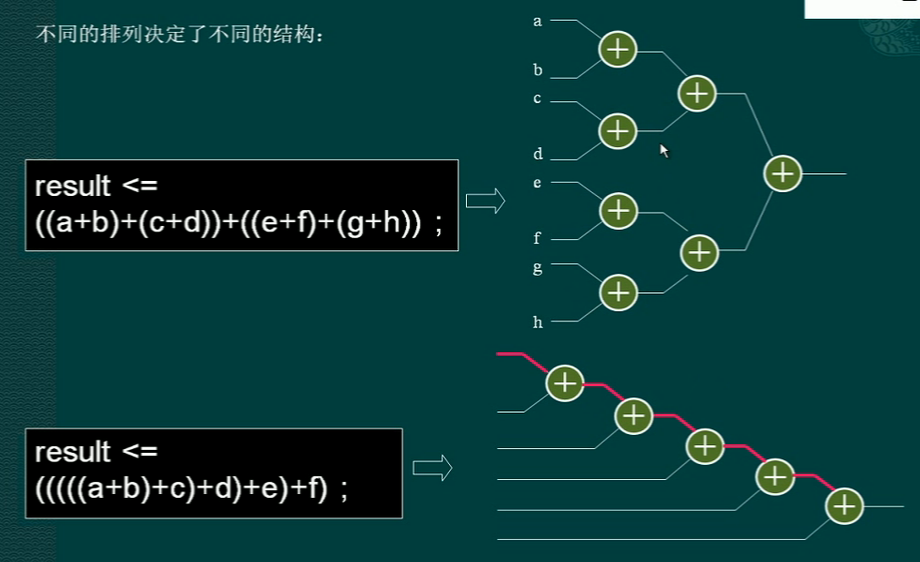

面積和速度是晶片設計中一對相互制約、影響成本和效能的指標,貫穿FPGA設計的始終。在FPGA內部邏輯資源的數量,可以用消耗的觸發器和查詢表的個數或者是等效邏輯閘數來衡量; 速度是指一個設計在FPGA上穩定執行時所能達到的最高頻率,由設計時序狀態決定。與設計滿足的時鐘週期、CLOCK SETUP TIME、CLOCK HOLD TIME 和CLOCK-TO-OUTPUT DELAY等眾多時序特徵量密切相關。(時序約束的違規很大程度上就取決於FPGA邏輯單元之間在傳送資料的時候暫存器之間的建立時間和保持時間) 關於面積和速度的折衷,應在滿足設計時序和工作頻率要求的前提下,佔用最小的芯片面積;或者在所規定的面積下,使得設計的時序餘量最大,能夠在更高的頻率上穩定執行。**通常,在資源足夠的情況下,更多是選擇速度的最優,這也是FPGA的的特點。**在具體設計中,應根據具體效能指標要求,在保證系統功能和效能的同時,降低資源消耗從而降低功耗和成本。

上邊的圖走了3個加法器(相當於3個tpt延遲),是速度的優先

下邊的圖走了5個加法器,是面積的優先。

高階FPGA設計技巧:

針對速度的優化;

針對資源的優化;

針對功耗的優化。

2、硬體可實現(feasibility)

首先,HDL不是C,是描述硬體系統的語言,並行性。 要注意FPGA的邏輯設計所採用的硬體描述語言VHDL或Verilog與軟體語言C和C++有本質區別,在使用硬體描述語言進行設計時,不應片面追求程式碼的簡潔。 其次,要採用正確的編碼方法。 要對所需實現的硬體電路的結構和相互連線有清晰的理解和構想,然後再用適當的VHDL語言表達出來。實際上綜合軟體對所寫的程式碼在進行推論的時候,得到的硬體結果會因編碼方式的不同,直接影響硬體的實現。

3、層次化設計(Hierarchical Design)

FPGA作為硬體系統設計,應該對設計全域性進行巨集觀上的合理安排,包括邏輯功能模組劃分、時鐘域訊號的產生和驅動、模組複用、時序或引腳約束、面積速度折衷等。這些系統上的考慮不僅關係到是否能夠最大程度的發揮專案成員的協同設計能力,而且直接決定著設計的綜合、實現效果和相關的操作時間。

模組化設計是系統原則的一個很好體現,它是自頂向下、模組劃分、分工協作設計思路的集中體現,是大型複雜系統的推薦設計方法。

層次化設計的好處

可讀性

易於理解設計的功能和資料流

易於除錯

設計中的部件可重用

增加易讀性的技巧

選擇具有如下結構的層次模組:

模組之間的邏輯資料流(資料流清晰)

儘量減少模組之間的路由

選擇具有描述性質的模組名和訊號名(訊號或者模組名的可讀性)

時鐘域分離

使不同時鐘之間清晰地互動關係(時鐘管理模組獨立)

控制檔案的長度

使得讀、綜合和除錯比較簡便(檔案不宜過長,建議每個檔案不超過一百行)

4、同步設計(Synchronization)

在設計電路時,可以有非同步電路和同步電路兩種實現方法。非同步電路使用組合邏輯電路實現,沒有統一的時鐘訊號,容易產生毛刺和冒險競爭;同步時序電路使用組合邏輯和觸發器實現電路功能,主要訊號和輸出訊號都由時鐘驅動觸發器產生,能夠避免毛刺,訊號穩定。(同步和高速掛鉤,沒有同步電路就沒有高速數位電路)

IP核的使用

1、什麼是IP?

IP即Intellectual Property(智慧財產權)

美國Dataquest公司於2001年將ASIC、ASSP、PLD(FPGA/CPLD)中預先設計好的功能模組稱為IP,該稱謂被業界接受。

一般是指在我們設計裡面的可重用的模組,有一定規模同時經過了嚴格測試,可重用的模組。

2、Altera的IP包括哪些內容?

Altera IP Core:免費的基本巨集功能Megafunctions(包括了一些基本的I/O輸入輸出的一些核、算數的一些核和儲存器的一些核);收費的通用模組MegaCore(第三方的廠商開發的一些核,例如HDMI,DDR控制器包含了很多技術含量的核)

什麼是LPM?

LPM即Library of Parameterized Modules(可定參模組庫)的縮寫

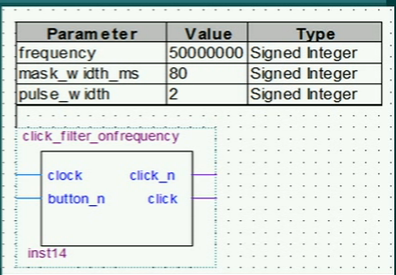

庫中的邏輯函式可以現場定製(通過修改引數Paramters)

從而實現庫函式的可擴充套件型

增加了庫函式的適應性(彈性需求)

3、IP分類

IP通常實現的過程分類:

IP type

軟核(IP soft core):

用HDL語言的形式描述功能塊的行為,不涉及電路與元件

固核(IP firm core):

(Gate Level的形式)完成了綜合的功能塊,有較大的設計深度,以網表的形式提供使用

硬核(IP hard core):

提供最終階段產品---掩膜(Mask),幾乎沒有光學的都是數字的。

不同核的比較:

軟核:設計週期短,投入少

固核:較大的設計深度,重用性好

硬核:(photo mask)後續工作少,但靈活性受限(ASIC:專門積體電路;ASSP:在特殊應用中使用而設計的積體電路)

相關推薦

Verilog設計的原則和技巧和IP核的使用

FPGA設計原則 1、面積與速度折中(Area&speed tradeoff) 面積和速度是晶片設計中一對相互制約、影響成本和效能的指標,貫穿FPGA設計的始終。在FPGA內

【CPU微架構設計】利用Verilog設計基於飽和計數器和BTB的分支預測器

在基於流水線(pipeline)的微處理器中,分支預測單元(Branch Predictor Unit)是一個重要的功能部件,它負責收集和分析分支/跳轉指令的引數和執行結果,當處理新的分支/跳轉指令時,BPU將根據已有的統計結果和當前分支跳轉指令的引數,預測其執行結果,為流水線取指提供決策依據,進而提高流

Vivado2017.4建立和封裝使用者IP核(使用Nexys4開發板)

vivado不同於ISE的設計模式,vivado提供了以IP為中心的設計流程,可以幫助設計者快速的將自己的設計和演算法轉換成可重用的IP。 IP設計流程: 一、建立用於建立IP的工程 按照這個連結建立即可,下一步對這個工程封裝成一個IP核,

面向對象的三個基本特征 和 五種設計原則

對象相等 存在 正是 提高 都是 並不是 ram 無法 pro 面向對象的三個基本特征 和 五種設計原則 來源: http://blog.csdn.net/cancan8538/article/details/8057095 一、三個基本特征 面向對象的三個基本

ZBrush生物設計方法和技巧

3D圖形繪制軟件 生物設計 Mirror and Weld 本教程我們主要來看看使用ZBrush®中的mirror and weld工具設計生物或藝術品究竟有多簡單。 ZBrush中文視頻教程:http://peixun.zbrushcn.com/ Mirro

Xilinx DDR3 IP核使用問題匯總(持續更新)和感悟

amp per uid gravity 流程 vhdl ade 官方 vhd 一度因為DDR3的IP核使用而發狂。 後來因為解決問題,得一感悟。後面此貼會完整講述ddr3 ip的使用。(XILINX K7) 感悟:對於有供應商支持的產品,遇到問題找官方的流程。按照官方的指導

Vivado使用技巧:封裝自己設計的IP核

開源 創建 pre 範圍 輸入 sign 分享圖片 出了 face 概述 ??Vivado在設計時可以感覺到一種趨勢,它鼓勵用IP核的方式進行設計。“IP Integrator”提供了原理圖設計的方式,只需要在其中調用設計好的IP核連線。IP核一部分來自於Xilinx官方I

PHP面向對象設計模式和設計原則

color col 阻止 結果 php面向對象 了解 基類 var_dump image 一、設計模式 1.單例模式 目的:讓一個類只能生成一個對象 步驟: ①將構造函數變成私有的 ②在類裏面做一個靜態成員函數造對象

三、類模型-應用設計原則和設計模式

信用卡 動態 衡量 跟著 定義 判斷 類關系 購物 png 精雕細琢,設計良好的類與類關系 【設計原則】 無論項目開發流程用哪種模式,瀑布、叠代、螺旋、敏捷等。只要是面向對象設計,都應該應用設計原則以提高設計質量 設計SOLID原則: 1.設計原則有什麽用? 設計

OOP 思想 和 設計原則 及24種設計模式

父類 分組 策略 結構 並且 實例 適配器模式 closed 不同的 oop思想:封裝、繼承、多態 把組件實現和接口分開,並且讓組件具有多態性 面向對象編程是一種解決軟件復用的設計和編程方法,這種方法把軟件中相近相似的操作邏輯和操作應用數據

MySQL-性能優化-優化設計和設計原則

文件系統 big log wid sta 過程 times 加載 對數 MySQL性能優化目的如何合理的設計數據庫?什麽樣的數據庫設計才能給後期DBA優化提供基石? 數據庫設計與程序設計的差異? 數據庫設計早期優化1. 關系明確(理清表之間的關系,可以通過冗余的方式提高效率

面向對象開發中的七大設計原則和23種設計模式

調停者模式 bili 叠代器模式 erp 策略模式 flyweight 理解 ati 轉換成 一、面向對象開發中的七大設計原則 軟件開發中最核心的思想就是“高內聚,低耦合”,主要的目的也是為了方便後期的維護和變更。下面的設計原則也是依靠這個核心思想衍生出來的。 1、

6大設計原則和23種設計模式

前言: 最近看了一下《Android原始碼設計模式解析與實戰》這本書,對設計原則和設計模式有了一定的瞭解,故在此記錄一下相關的簡單定義。 6大設計原則 (S-O-L-I-D)–>穩固 單一職責原則(SRP ):對於一個類而言,應該有且僅有

微服務的4大設計原則和19種解決方案

微服務架構現在是談到企業應用架構時必聊的話題,微服務之所以火熱也是因為相對之前的應用開發方式有很多優點,如更靈活、更能適應現在需求快速變更的大環境。 本文將介紹微服務架構的演進、優缺點和微服務應用的設計原則,然後著重介紹作為一個“微服務應用平臺”需要提供哪些能力、解決哪些問題才能更好的支撐企業應用架構。

Atitit 微服務的一些理論 目錄 1. 微服務的4個設計原則和19個解決方案 1 2. 微服務應用4個設計原則 1 2.1. AKF拆分原則 2 2.2. 前後端分離 2 2.3. 無狀態服務

Atitit 微服務的一些理論 目錄 1. 微服務的4個設計原則和19個解決方案 1 2. 微服務應用4個設計原則 1 2.1. AKF拆分原則 2 2.2. 前後端分離 2 2.3. 無狀態服務 2 2.4. Restful通訊風格 2 3. 微服

面向物件的四個基本特徵和七大設計原則

複習一哈~ 基本特徵抽象 將一些事物的共性抽離出來歸為一個類。 如對於動物,具有生命體徵、活動能力等區別於其它事物的共同特徵 封裝 有選擇地隱藏和暴露資料和方法 比如有U盤這個類,我希望隱藏內部組成和實現,只暴露USB介面以供使用 繼承 子類可以直接使用父類的部分資料和方法,可以

ISE中FIFO IP核的Standard FIFO和First-word-Fall-Through模式的模擬比較

ISE下的FIFO IP核有Standard FIFO和First-word-Fall-Through兩種模式,相對於標準模式FWFT(First-word-Fall-Through)可以不需要讀命令,自動的將最新資料放在dout上。 接下來分別對兩種模式下的FIFO進行模擬,testbench如

logo設計之顏色搭配的技巧和內涵

type 一半 能量 能夠 使用 技術分享 計算機 強人 其他 對於在設計logo的時候,很多人認為只要顏色搭配的好看就行,其實在設計中,顏色的搭配傳遞這不同的訊息,在色彩心理學中人們對色彩的感知還是非常主觀的,一些顏色有著特定的意義。 ××××××是一種炫目的顏色,通常用

做APP設計需要的PS技巧和一些快捷鍵

PS學習筆記 快捷鍵: 工具箱: (shift+) 預設前景色和背景色 【D】 切換前景色和背景色 【X】 臨時使用移動工具 【Ctrl】臨時使用吸色工具 【Alt】 檔案操作: 開啟已有的影象 【Ctrl

面向物件的三個基本特徵和五種設計原則

面向物件的三個基本特徵 抽象與封裝: 抽象是把系統中需要處理的資料和在這些資料上的操作結合在一起,根據功能、性質和用途等因素抽象成不同的抽象資料型別。每個抽象資料型別既包含了資料,又包含了針對這些資料的授權操作。在面向物件的程式設計中,抽象資料型別是用“類”