基於FPGA視訊影象處理系統設計

摘要

本報告給出一個基於FPGA+兩片DDR2組成的核心板、帶有4路視訊輸入和VGA介面的開發板進行的視訊影象採集和處理系統的設計。使用TW2867進行視訊輸入訊號的編碼,儲存到DDR2中,通過FPGA和ARM的聯合控制,通過I2C匯流排進行通訊,進行數字影象處理,實現了單通道視訊訊號輸入螢幕顯示、4通過視訊訊號輸入4分屏顯示、邊沿檢測演算法,將處理結果通過VGA介面連線到LCD顯示器上進行顯示。本報告從硬體設計和軟體設計兩個方面對該基於FPGA的視訊影象處理系統的工作過程做了詳盡描述。

關鍵詞:視訊影象處理、FPGA、邊沿檢測、4分屏顯示

1、設計目的

影象處理技術和機器視覺作為一門前沿的技術,為人們的生活和工作帶來了極大的便利和愉悅。由於視訊訊號的資料量大,訊號較為複雜,這就要求視訊訊號處理系統具有實時採集、大容量儲存和實時處理的特點。本報告提出基於現場可程式設計門陣列

2、設計任務與效能指標

本系統中主要是通過AV介面實現視訊影象採集,將採集到的4路模擬電視訊號進行格式編碼轉換成數字訊號,儲存在DDR2中作為快取,供FPGA處理器進行數字影象的處理,處理的結果再通過視訊編碼晶片轉換為模擬電視訊號通過VGA介面完成基於LCD顯示器的4分屏視訊影象顯示功能,在影象處理中完成邊緣檢測演算法的實現。

3、系統總體設計與工作原理

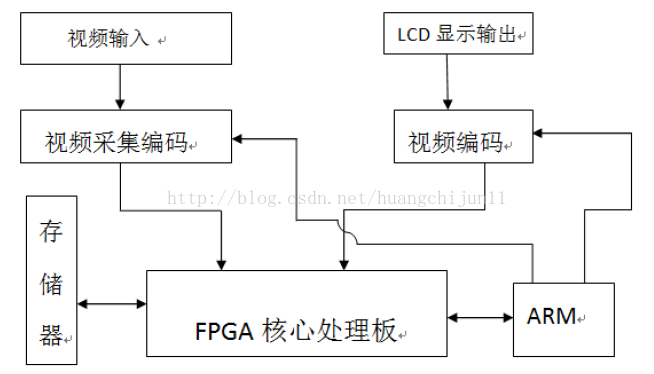

本系統由視訊影象採集模組、儲存模組、顯示模組以及相關配置電路模組組成。採集模組通過視訊通過解碼晶片

在原理框圖1中可以看到有4路視訊輸入訊號,選擇4路輸入訊號是因為要實現4分屏分割顯示4路攝像頭採集到的資訊,因為攝像頭硬體資源的欠缺,只使用了兩個攝像頭但是原理是完成實現了,只要安裝夠

圖1系統設計原理

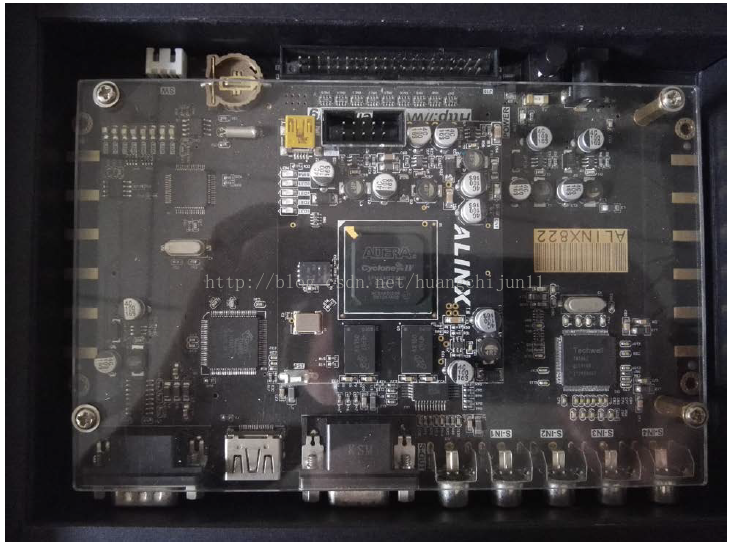

3.1系統硬體設計因為本系統設計是基於黑金動力社群的FPGA視訊處理開發平臺實驗板進行的,因此所使用的硬體電路也是該開發板上搭載的實驗器件,均是已經較為成熟的視訊影象採集與處理硬體裝置。實驗板型號為ALINX822 REV3.0,在該實驗板上整個開發板的結構繼承了一貫的核心板和擴充套件板的模式進行設計的。核心板主要由FPGA+兩片DDR2構成,承擔視訊影象處理的核心演算法,充分利用了FPGA並行處理的能力,加上兩片DDR2構成32bit匯流排,整個系統的頻寬高達10Gb/s,兩片DDR2容量高達2Gbit,滿足視訊處理過程中對高緩衝區的需求。該實驗板選用的FPGA為ALTERA公司CYCLONE IV系列中速度級別最高的C6級別,可以實現FPGA和DDR2之間的時鐘頻率達到200M,DDR2內部400M,充分滿足了四路1080P視訊處理的需求。

圖2開發板實物圖

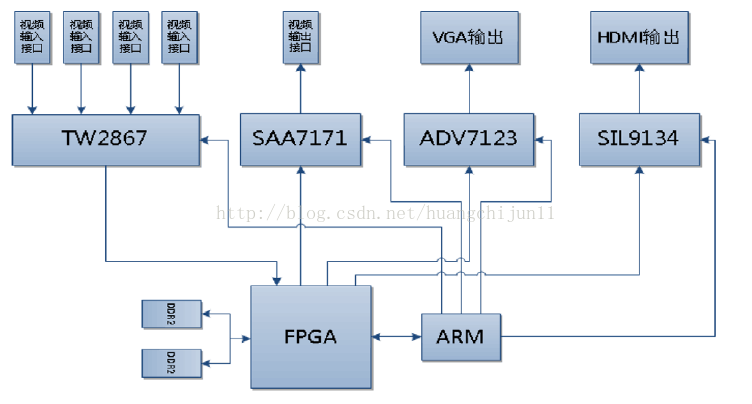

上圖2是使用的開發板的實物圖,從上面可以看到其實驗板的型號,搭載的器件的一些型號資訊,中間的即為核心板,核心板下面則是一塊更大面積的擴充套件板,擴充套件板上則分佈著VGA介面、HDMI介面、視訊輸出介面、視訊輸入介面、ARM控制器、擴充套件口、SD卡槽等器件。從下圖3中可以看到整個開發板的系統結構圖。

圖3開發板結構圖

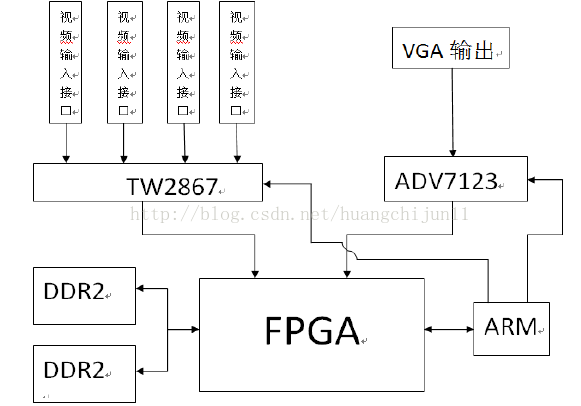

本系統所使用到的器件框架結構圖在圖4中可以清晰地看到,跟整個開發板結構圖相比,沒有使用到視訊輸出介面和HDMI介面,其他則都用到了。TW2867是為了將視訊輸入介面採集到的視訊訊號進行編碼成數字訊號,ADV7123是將經過處理後的數字訊號轉為模擬電視訊號,以供VGA介面連線顯示器進行LCD屏的顯示。

圖4硬體設計原理框圖

3.2單元電路設計

1,採集模組

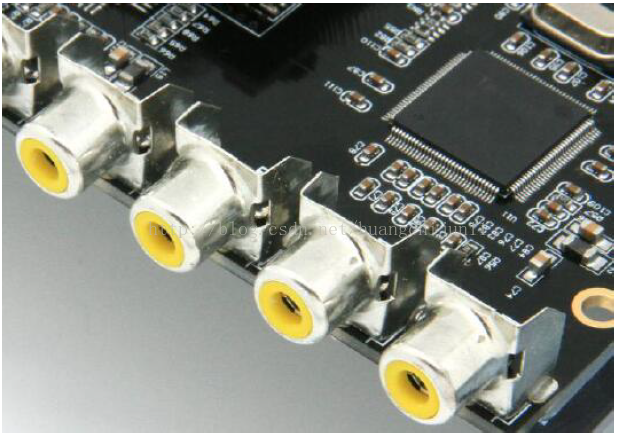

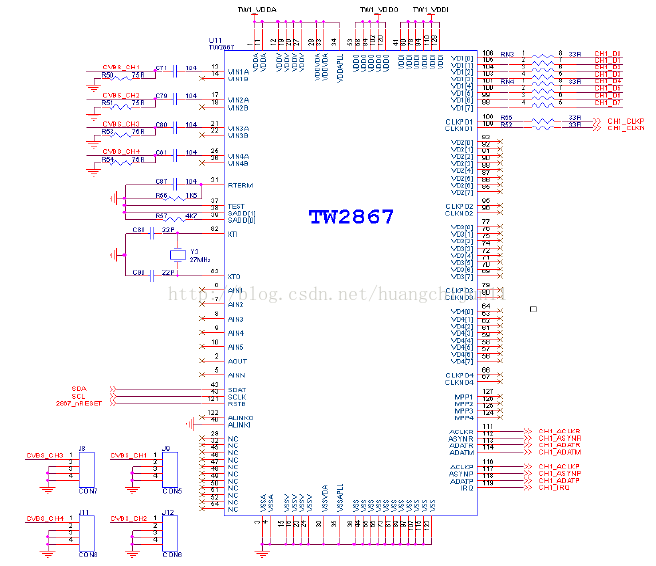

採集模組是選用了Techwell公司的TW2867,可以輸入4路符合視訊訊號,PAL/NTSC/SECAM自動識別,輸出BT656,可多路複用匯流排,FPGA端解複用,節省IO,其中TW2867的IIC介面和復位引腳與STM32F103相連,通過STM32F103來對TW2867進行初始化和控制操作,其他引腳與FPGA相連。在圖5中,可以看到4路視訊輸入介面跟TW2867相連線,實現4路視訊輸入。

與ARM對應引腳如下表1所示:

表1ARM引腳對應表

|

引腳名稱 |

ARM引腳 |

|

SDA |

39 |

|

SCL |

40 |

|

2867_NRESET |

41 |

圖5視訊輸入介面實物圖

與FPGA對應引腳如下表2所示:

表2 FPGA引腳對應表

|

引腳名稱 |

FPGA引腳 |

|

cvbs_in_cikp |

P20 |

|

cvbs_in_cikn |

N19 |

|

cvbs_in_data[0] |

M19 |

|

cvbs_in_data[1] |

N20 |

|

cvbs_in_data[2] |

M20 |

|

cvbs_in_data[3] |

T17 |

|

cvbs_in_data[4] |

P17 |

|

cvbs_in_data[5] |

R17 |

|

cvbs_in_data[6] |

N18 |

|

cvbs_in_data[7] |

N17 |

圖6電路設計連線圖

2,儲存模組

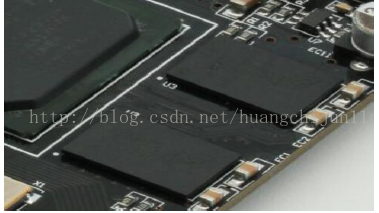

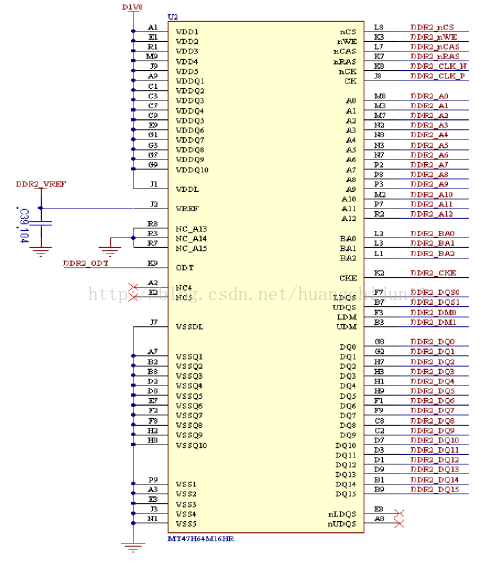

本部分完成影象資料在DDR2中的幀存,為後端影象進一步處理做好準備,影象資料採集後需要進行影象處理,在處理進行前和處理進行中,未得到處理的影象資料資訊需放置在幀快取中。儲存模組是使用了DDR2晶片,容量為1Gbit,兩片DDR2晶片構建32bit匯流排模式,2G容量,頻寬高達10Gb,可以滿足4路1080p視訊處理的需求。

圖7 DDR2實物圖

圖8DDR2電路圖

在下表3中可以看到DDR2引腳對應表:

表3 DDR2引腳對應表

|

引腳名稱 |

FPGA引腳 |

引腳名稱 |

FPGA引腳 |

|

mem_addr[0] |

U10 |

mem_addr[8] |

AA3 |

|

mem_addr[1] |

Y6 |

mem_addr[9] |

U13 |

|

mem_addr[2] |

T16 |

mem_addr[10] |

V6 |

|

mem_addr[3] |

R14 |

mem_addr[11] |

AB3 |

|

mem_addr[4] |

AA4 |

mem_addr[12] |

U14 |

|

mem_addr[5] |

T11 |

mem_ba[0] |

U7 |

|

mem_addr[6] |

AB5 |

mem_ba[1] |

AB10 |

|

mem_addr[7] |

T14 |

mem_ba[2] |

T9 |

|

mem_cas_n |

R15 |

mem_dq[15] |

W10 |

|

mem_cke[0] |

U8 |

mem_dq[16] |

AB15 |

|

mem_clk[0] |

AA17 |

mem_dq[17] |

W13 |

|

mem_clk_n[0] |

AB17 |

mem_dq[18] |

AB14 |

|

mem_cs_n[0] |

Y17 |

mem_dq[19] |

AA13 |

|

mem_dm[0] |

V5 |

mem_dq[20] |

AB13 |

|

mem_dm[1] |

相關推薦基於FPGA視訊影象處理系統設計摘要 本報告給出一個基於FPGA+兩片DDR2組成的核心板、帶有4路視訊輸入和VGA介面的開發板進行的視訊影象採集和處理系統的設計。使用TW2867進行視訊輸入訊號的編碼,儲存到DDR2中,通過FPGA和ARM的聯合控制,通過I2C匯流排進行通訊,進行數字影 課設 - 基於FPGA的電子警察系統設計(流程)本文以FPGA晶片為核心,來檢測運動車輛是否超速以及車輛是否闖紅燈。 通過攝像機採集到的影象以影象處理的方法進行處理,然後通過MATLAB軟體將採集到的圖片轉化成Verilog可識別的的數字程式碼,再加以幀間差分法、最小二乘法,對處理過後的影象進行進一步的 【FPGA筆記】基於FPGA的影象處理影象處理系統設計注意點:1.將演算法開發和FPGA實現分離用軟體的影象處理環境可以使用大批量的影象樣本進行測試及除錯演算法,再將演算法對映到硬體上,這樣大大節省了硬體調試周期。2.演算法的精度影象處理的演算法中,大部分需要採用浮點數運算,而浮點數運算再FPGA中是非常不划算的 基於FPGA的影象處理(三)--影象融合System Generator安裝之後可以在Simulink中呼叫相應的模組進行視覺演算法的搭建,我兩臺電腦上分別是ISE12.3+matlab2010a, ISE10.1+Matlab2010a。需要注意的是ISE和Matlab之間是有型號匹配的。 基於FPGA的影象處理(五)--狀態機使用FPGA實現各種演算法時,狀態機是很常用的方法,在SysGen中有兩種非常簡便的方法構建狀態機,一是使用Mcode,以switch-case語句輕鬆實現,二是使用SysGen自帶狀態機模組。 狀態機 假設我們要從01序列中檢測出1011序列,則 基於matlab的數字影象處理GUI設計簡單的介面實現的幾個簡單的功能,只支援JPG格式影象,還有很多需要改進的。 1、灰度化:提取jpg影象各個畫素點的R、G、B三個型別的值,再對其進行加權平均。最後得到一個通道紅綠藍三個型別的加權平均。 公式為:ima=0.299*ima_red+0.587*ima_green+0.114* 課設 - 基於微控制器的智慧小車系統設計本次設計的簡易智慧電動車,採用AT89S52微控制器作為小車的檢測和控制核心;採用金屬感應器TL-Q5MC來檢測路上感應到的鐵片,從而把反饋到的訊號送微控制器,使微控制器按照預定的工作模式控制小車在各區域按預定的速度行駛,並且微控制器選擇的工作模式不同也可控制小車順著S形鐵片行 課設 - 基於微控制器的溫控報警系統設計 (電路+程式)本設計所介紹的數字溫度計與傳統的溫度計相比,具有讀數方便,測溫範圍廣,測溫準確,其輸出溫度採用數字顯示,主要用於對測溫比較準確的場所,或科研實驗室使用,該設計控制器使用微控制器AT89S51,測溫感測器使用DS18B20,用3位共陽極LED數碼管以串列埠傳送資料,實現溫度顯示, 基於微控制器的條形碼掃描系統設計行動式商品條形碼識別器,上面提到主要由四大模組組成。鐳射掃描,微控制器,12864液晶顯示器,電源模組。其工作的大致原理為,鐳射掃描到條形碼並進行儲存。同時蜂鳴器開始鳴響,然後掃描器將資料資訊通過串列埠通訊傳輸給微控制器,微控制器收到資訊後會與事先設定好的程式進行對比,並將對比 [原始碼和文件分享]基於C++的庫存管理系統設計與實現一 需求分析 1.1 總體要求 運用面向物件程式設計知識,利用C++語言設計和實現一個“庫存管理系統設計”,主要完成對商品的銷售、統計和簡單管理。在實現過程中,需利用面向物件程式設計理論的基礎知識,充分體現出C++語言關於類、繼承和封裝等核心概念,每一個類應包含資料成員和成員函式。 1. [原始碼和文件分享]基於C++的學生生活系統設計與實現一 需求分析 需要設計並實現如下場景:在那山的那邊,湖的那邊,有一所學校,學校裡有一幢宿舍樓,宿舍樓有若干層,每一層有若干房間 ,一群學生快樂地生活在這裡。他們每天可做的事情有: 換宿舍,從一個房間搬到另一個房間 退學,亦即搬出宿舍樓 入學,亦即搬入宿舍樓 基於微控制器的數字鐘系統設計(電路+程式)上圖是Proteus模擬圖,其中反相器用74lHC14,排阻用10K的,晶振用12MHZ的,電阻R1-R8用200歐的即可。但在實際製作時數碼管可以用兩個四位一體共陽極的,這樣連線電路會更加方便。可以用三極體代替反相器,這樣可以節約成本,但代替後無法用Proteus模擬出來,下圖為代替後的圖 【資訊科技】【2015.05】【含原始碼】基於彩色色調影象處理的目標跟蹤本文為美國阿肯色大學(作者:ZacharyR. Sabey)的學士論文,共44頁。 如今,許多工業和商業應用開始使用無人系統來提高生產力,並降低生產和人力成本。這些應用中的大多數產品都是半無人化的,它們仍然需要人類來啟動或接收連續的指令。隨著影象處理技術、攝像機處理能力和更高效的車 基於FPGA的訊號發生器的設計基於FPGA的訊號發生器的設計 首先先要介紹的是本設計的主晶片是ALTERA的一款晶片,晶片名稱是EP2C5T144C8N。該晶片的LE單元有4608個,PLL鎖相環具有2個,IO口管腳具有142個,差分通道55個,嵌入式乘法器26個,RAM的儲存容量大小是119808bits.該FPGA晶片的功 【資訊科技】【2013.08】觀察蜜蜂活動的自動影象處理系統的實現本文為美國阿巴拉契亞州立大學(作者:AHMAD GHADIRI)的碩士論文,共100頁。 蜜蜂佔全世界授粉量的一半以上,因此它們在農業中具有非常重要的作用。近年來,由於蜂群崩潰綜合症(CCD是一個近代發現而至今不明的自然現象,導致大批蜂巢內的工蜂突然消失。CC 【181118】VC++簡單醫學影象處理系統原始碼原始碼下載簡介 VC++簡單醫學影象處理系統,可以調整影象色階、銳度、反色、灰底均衡,還可以對影象進行反轉、平移、旋轉等操作,類似Photoshop某些功能一樣,當然,和PS比,是差了點,只能作為一些 [原始碼和文件分享]基於QT的考試管理系統設計與實現一、專案概要 1.1 專案名稱 考試管理系統 1.2 專案目標 培養快速學習新的知識,解決問題的能力 規劃專案的整體功能以及相關需求分析,並設計出合理的資料庫,並熟悉整個試題系統的開發流程。 1.3 軟體概要 開發一個考試管理系統,考生可以進行練習, 基於RBAC模型的許可權系統設計(Github開源專案)計劃在Team的Github開源專案里加入許可權控制的業務功能。從而實現許可權控制。在很多管理系統裡都是有許可權管理這些通用模組的,當然在企業專案裡,許可權控制是很繁雜的。 Team的Github開源 FPGA實現影象處理中的直方圖統計利用FSM,狀態機編寫程式實現直方圖統計,大意為,對影象中各個灰度級的畫素個數進行計算並統計。我現在利用RAM,把影象的灰度級當做地址輸入,然後畫素數目當做ram的內容。統計同一灰度級的畫素數目就是在雙口RAM中在同一地址進行內容的累加。 狀態機如圖所示: 其中各個狀態為: 基於STM32的水質檢測系統設計 (電路+流程)本文設計了一個基於STM32F103RCT6微控制器的地下水檢測系統,該系統用於檢測地下水的水質狀況,可以體現水質狀況的主要引數有水溫,電導率,PH值還有濁度等。 對於水溫來說,一般情況是地下水的水溫越低,那麼意味著,地下水所處的位置越深,即水位資料比較大,可以根據 |