PLDFPGA 查詢表結構和乘積項結構

採用這種結構的PLD晶片我們也可以稱之為FPGA:如altera的ACEX,APEX系列,xilinx的Spartan,Virtex系列等。

查詢表(Look-Up-Table)簡稱為LUT,LUT本質上就是一個RAM。 目前FPGA中多使用4輸入的LUT,所以每一個LUT可以看成一個有4位地址線的16x1的RAM。 當用戶通過原理圖或HDL語言描述了一個邏輯電路以後,PLD/FPGA開發軟體會自動計算邏輯電路的所有可能的結果,並把結果事先寫入RAM,這樣,每輸入一個訊號進行邏輯運算就等於輸入一個地址進行查表,找出地址對應的內容,然後輸出即可。

下面是一個4輸入與門的例子,

實際邏輯電路 LUT的實現方式

a,b,c,d 輸入

邏輯輸出 地址 RAM中儲存的內容

0000

0 0000 0 0001 0 0001 0 .... 0 ... 0 1111 1 1111 1

二.PLDFPGA基於查詢表(LUT)的FPGA的結構

我們看一看xilinx Spartan-II的內部結構,如下圖:

xilinx Spartan-II 晶片內部結構 Slices結構

Spartan-II主要包括CLBs,I/O塊,RAM塊和可程式設計連線(未表示出)。在spartan-II中,一個CLB包括2個Slices,每個slices包括兩個LUT,兩個觸發器和相關邏輯。 Slices可以看成是SpartanII實現邏輯的最基本結構 (xilinx其他系列,如SpartanXL,Virtex的結構與此稍有不同,具體請參閱資料手冊)

altera的FLEX/ACEX等晶片的結構如下圖:

altera FLEX/ACEX 晶片的內部結構

邏輯單元(LE)內部結構

FLEX/ACEX的結構主要包括LAB,I/O塊,RAM塊(未表示出)和可程式設計行/列連線。在FLEX/ACEX中,一個LAB包括8個邏輯單元(LE),每個LE包括一個LUT,一個觸發器和相關的相關邏輯。LE是FLEX/ACEX晶片實現邏輯的最基本結構(altera其他系列,如APEX的結構與此基本相同,具體請參閱資料手冊)

二.PLDFPGA

查詢表結構的FPGA邏輯實現原理

我們還是以這個電路的為例:

A,B,C,D由FPGA晶片的管腳輸入後進入可程式設計連線,然後作為地址線連到到LUT,LUT中已經事先寫入了所有可能的邏輯結果,通過地址查詢到相應的資料然後輸出,這樣組合邏輯就實現了。 該電路中D觸發器是直接利用LUT後面D觸發器來實現。時鐘訊號CLK由I/O腳輸入後進入晶片內部的時鐘專用通道,直接連線到觸發器的時鐘端。觸發器的輸出與I/O腳相連,把結果輸出到晶片管腳。這樣PLD就完成了圖3所示電路的功能。(以上這些步驟都是由軟體自動完成的,不需要人為干預)

這個電路是一個很簡單的例子,只需要一個LUT加上一個觸發器就可以完成。對於一個LUT無法完成的的電路,就需要通過進位邏輯將多個單元相連,這樣FPGA就可以實現複雜的邏輯。

由於LUT主要適合SRAM工藝生產,所以目前大部分FPGA都是基於SRAM工藝的,而SRAM工藝的晶片在掉電後資訊就會丟失,一定需要外加一片專用配置晶片,在上電的時候,由這個專用配置晶片把資料載入到FPGA中,然後FPGA就可以正常工作,由於配置時間很短,不會影響系統正常工作。 也有少數FPGA採用反熔絲或Flash工藝,對這種FPGA,就不需要外加專用的配置晶片。

三.PLDFPGA

其他型別的FPGA和PLD

隨著技術的發展,在2004年以後,一些廠家推出了一些新的PLD和FPGA,這些產品模糊了PLD和FPGA的區別。例如Altera最新的MAXII系列PLD,這是一種基於FPGA(LUT)結構,整合配置晶片的PLD,在本質上它就是一種在內部集成了配置晶片的FPGA,但由於配置時間極短,上電就可以工作,所以對使用者來說,感覺不到配置過程,可以傳統的PLD一樣使用,加上容量和傳統PLD類似,所以altera把它歸作PLD。 還有像Lattice的XP系列FPGA,也是使用了同樣的原理,將外部配置晶片整合到內部,在使用方法上和PLD類似,但是因為容量大,效能和傳統FPGA相同,也是LUT架構,所以Lattice仍把它歸為FPGA。

四.PLDFPGA基於乘積項(Product-Term)結構CPLD

CPLD多是基於乘積項(Product-Term)的結構。採用這種結構的CPLD晶片有:Altera的MAX7000,MAX3000系列(EEPROM工藝),Xilinx的XC9500系列(Flash工藝)和Lattice,Cypress的大部分產品(EEPROM工藝)

我們先看一下這種CPLD的總體結構(以MAX7000為例,其他型號的結構與此都非常相似):

圖1 基於乘積項的CPLD內部結構

這種CPLD可分為三塊結構:巨集單元(Marocell),可程式設計連線(PIA)和I/O控制塊。 巨集單元是CPLD的基本結構,由它來實現基本的邏輯功能。圖1中蘭色部分是多個巨集單元的集合(因為巨集單元較多,沒有一一畫出)。可程式設計連線負責訊號傳遞,連線所有的巨集單元。I/O控制塊負責輸入輸出的電氣特性控制,比如可以設定集電極開路輸出,擺率控制,三態輸出等。圖1 左上的INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是全域性時鐘,清零和輸出使能訊號,這幾個訊號有專用連線與PLD中每個巨集單元相連,訊號到每個巨集單元的延時相同並且延時最短。

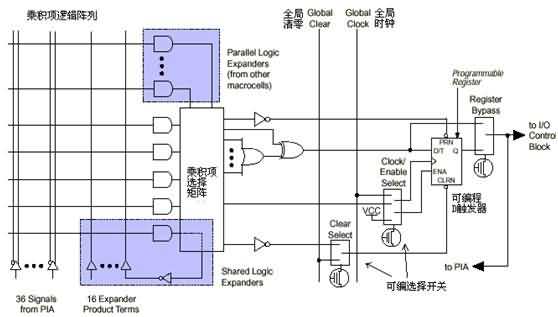

巨集單元的具體結構見下圖:

圖2 巨集單元結構

左側是乘積項陣列,實際就是一個與或陣列,每一個交叉點都是一個可程式設計熔絲,如果導通就是實現“與”邏輯。後面的乘積項選擇矩陣是一個“或”陣列。兩者一起完成組合邏輯。圖右側是一個可程式設計D觸發器,它的時鐘,清零輸入都可以程式設計選擇,可以使用專用的全域性清零和全域性時鐘,也可以使用內部邏輯(乘積項陣列)產生的時鐘和清零。如果不需要觸發器,也可以將此觸發器旁路,訊號直接輸給PIA或輸出到I/O腳。

本文來自: 高校自動化網(Www.zdh1909.com) 詳細出處參考(轉載請保留本連結):