亞穩態的產生機理、消除辦法

1. 應用背景

1.1 亞穩態發生原因

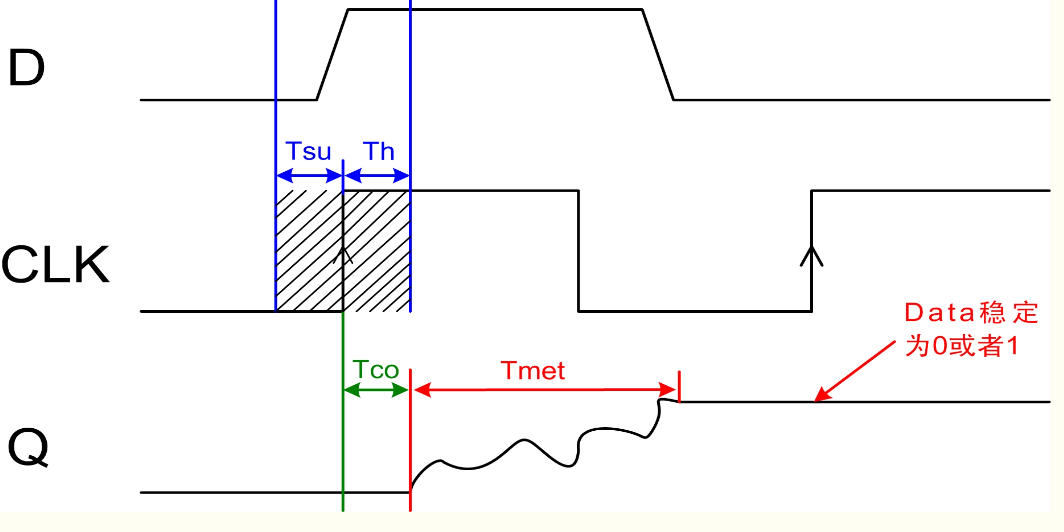

在FPGA系統中,如果資料傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位訊號的釋放相對於有效時鐘沿的恢復時間(recovery time)不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之後比較長的一段時間處於不確定的狀態,在這段時間裡Q端在0和1之間處於振盪狀態,而不是等於資料輸入端D的值。這段時間稱為決斷時間(resolution time)。經過resolution time之後Q端將穩定到0或1上,但是穩定到0或者1,是隨機的,與輸入沒有必然的關係。

1.2 亞穩態發生場合

只要系統中有非同步元件,亞穩態就是無法避免的,亞穩態主要發生在非同步訊號檢測、跨時鐘域訊號傳輸以及復位電路等常用設計中。

1.3 亞穩態危害

由於產生亞穩態後,暫存器Q端輸出在穩定下來之前可能是毛刺、振盪、固定的某一電壓值。在訊號傳輸中產生亞穩態就會導致與其相連其他數字部件將其作出不同的判斷,有的判斷到“1”有的判斷到“0”,有的也進入了亞穩態,數字部件就會邏輯混亂。在復位電路中產生亞穩態可能會導致復位失敗。怎麼降低亞穩態發生的概率成了FPGA設計需要重視的一個注意事項。

2. 理論分析

2.1 訊號傳輸中的亞穩態

在同步系統中,輸入訊號總是系統時鐘同步,能夠達到暫存器的時序要求,所以亞穩態不會發生。亞穩態問題通常發生在一些跨時鐘域訊號傳輸以及非同步訊號採集上。

它們發生的原因如下:

(1)在跨時鐘域訊號傳輸時,由於源暫存器時鐘和目的暫存器時鐘相移未知,所以源暫存器資料發出資料,資料可能在任何時間到達非同步時鐘域的目的暫存器,所以無法保證滿足目的暫存器Tsu和Th的要求;

(2)在非同步訊號採集中,由於非同步訊號可以在任意時間點到達目的暫存器,所以也無法保證滿足目的暫存器Tsu和Th的要求;

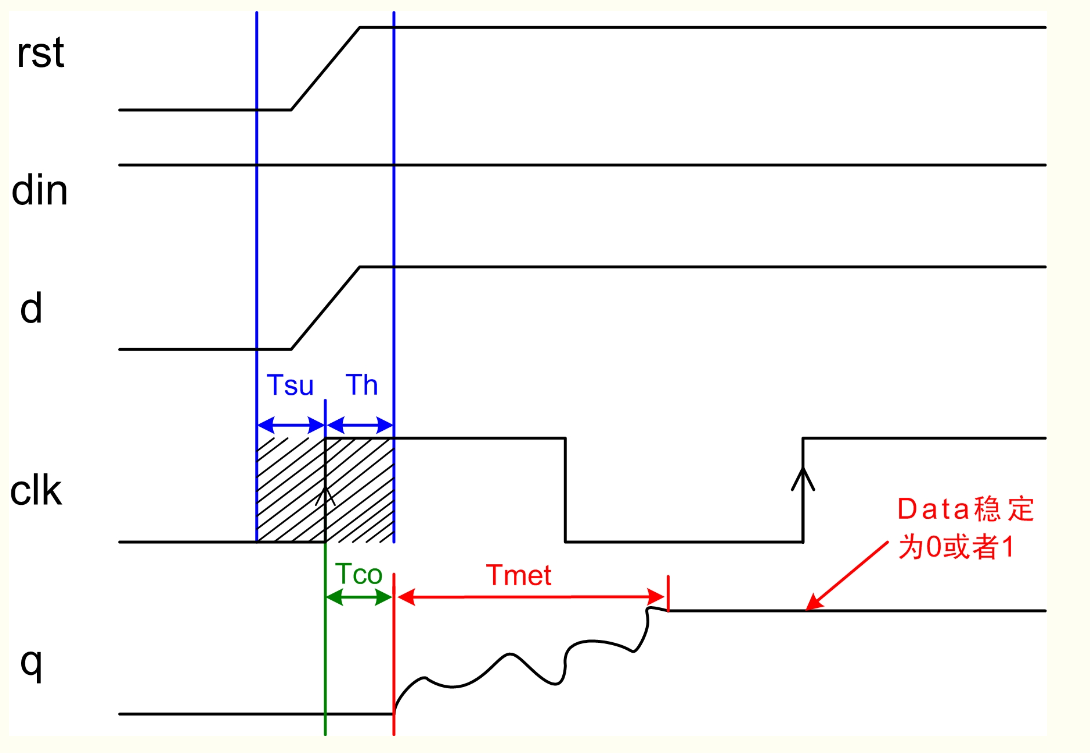

當資料在目的暫存器Tsu-Th時間視窗發生變化,也即當資料的建立時間或者保持時間不滿足時,就可能發生亞穩態現象。如圖2.1所示。 圖 2.1 亞穩態產生示意圖

圖 2.1 亞穩態產生示意圖2.2 復位電路的亞穩態

2.2.1 非同步復位電路

在復位電路設計中,復位訊號基本都是非同步的,常用非同步復位電路Verilog描述如下:

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) a <= 1’b0;

else a <= b;

end

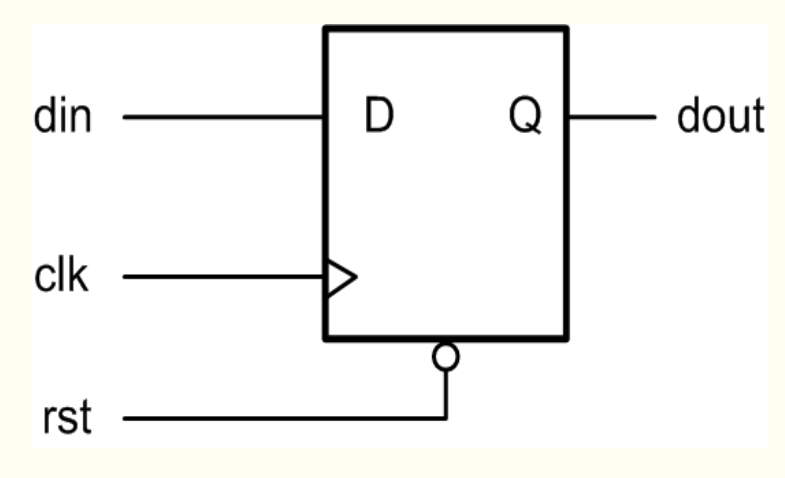

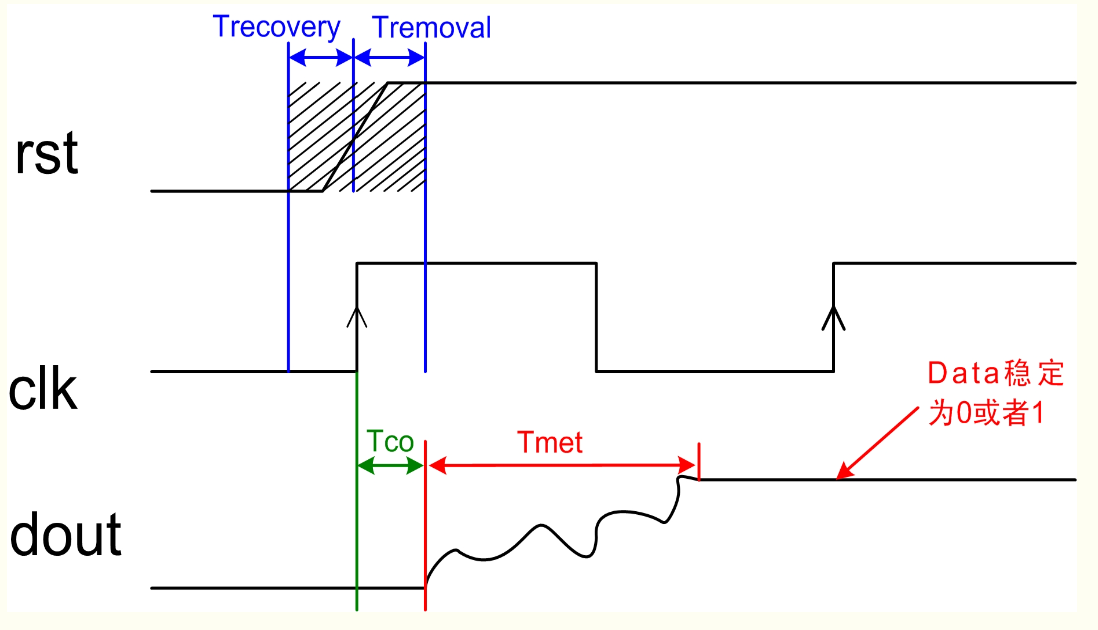

綜合出來復位電路模型如圖2.2所示: 圖 2.2 非同步復位電路模型如圖2.3所示,為復位電路復位時序圖。如果非同步復位訊號的撤銷時間在Trecovery(恢復時間)和Tremoval(移除時間)之內,那勢必造成亞穩態的產生,輸出在時鐘邊沿的Tco後會產生振盪,振盪時間為Tmet(決斷時間),最終穩定到“0”或者“1”,就會可能造成復位失敗。

圖 2.2 非同步復位電路模型如圖2.3所示,為復位電路復位時序圖。如果非同步復位訊號的撤銷時間在Trecovery(恢復時間)和Tremoval(移除時間)之內,那勢必造成亞穩態的產生,輸出在時鐘邊沿的Tco後會產生振盪,振盪時間為Tmet(決斷時間),最終穩定到“0”或者“1”,就會可能造成復位失敗。  圖2.3 非同步復位時序

圖2.3 非同步復位時序2.2.1.1 恢復和去除時間(Recovery and Removal Time)

恢復時間(Recovery Time)是指非同步控制訊號(如暫存器的非同步清除和置位控制訊號)在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,也就是說這個非同步控制訊號的解除與“下個時鐘沿”離得太近(但在這個時鐘沿之前),沒有給暫存器留有足夠時間來恢復至正常狀態,那麼就不能保證“下個時鐘沿”能正常作用,也就是說這個“時鐘沿”可能會失效。

去除時間(Removal)是指非同步控制訊號(如暫存器的非同步清除和置位控制訊號)在“有效時鐘沿”之後變無效的最小時間長度。這個時間的意義是,如果保證不了這個去除時間,也就是說這個非同步控制訊號的解除與“有效時鐘沿”離得太近(但在這個時鐘沿之後),那麼就不能保證有效地遮蔽這個“時鐘沿”,也就是說這個“時鐘沿”可能會起作用。

換句話來說,如果你想讓某個時鐘沿起作用,那麼你就應該在“恢復時間”之前是非同步控制訊號變無效,如果你想讓某個時鐘沿不起作用,那麼你就應該在“去除時間”過後使控制訊號變無效。如果你的控制訊號在這兩種情況之間,那麼就沒法確定時鐘沿是否起作用或不起作用了,也就是說可能會造成暫存器處於不確定的狀態。而這些情況是應該避免的。所以恢復時間和去除時間是應該遵守的。2.2.2 同步復位電路的亞穩態

在復位電路中,由於復位訊號是非同步的,因此,有些設計採用同步復位電路進行復位,並且絕大多數資料對於同步復位電路都認為不會發生亞穩態,其實不然,同步電路也會發生亞穩態,只是機率小於非同步復位電路。

如下面verilog程式碼對同步復位電路的描述。

always @(posedge clk)

begin

if(!rst_n) a <= 1’b0;

else a <= b;

end

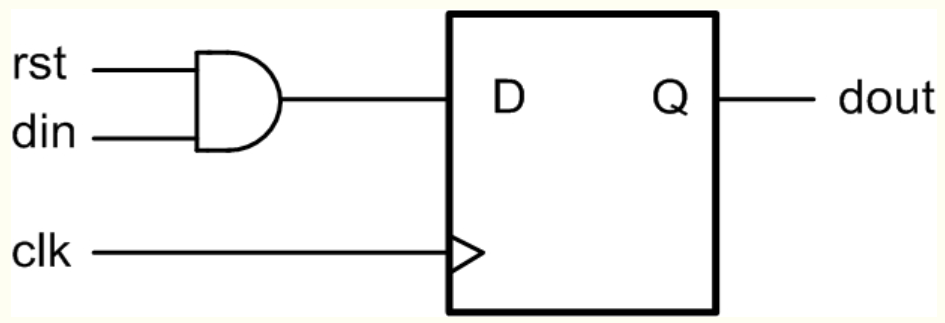

綜合出硬體電路如圖2.4所示。 圖2.4 同步復位電路

圖2.4 同步復位電路在此,我們不討論同步復位的消耗資源問題,只討論同步復位的亞穩態產生情況。

當輸入端Din為高電平,而且復位訊號的撤銷時間在clk的Tsu和Th內時候,亞穩態就隨之產生了。如圖3.5時序所示,當復位撤銷時間在clk的Tsu和Th內,輸入資料為“1”,通過和輸入資料相與後的資料也在clk的Tsu和Th內,因此,勢必會造成類似非同步訊號採集的亞穩態情況。 圖2.5 同步復位電路時序圖

圖2.5 同步復位電路時序圖2.3 亞穩態產生概率以及串擾概率

在實際的FPGA電路設計中,常常人們想的是怎麼減少亞穩態對系統的影響,很少有人考慮怎麼才能減少亞穩態發生機率,以及亞穩態串擾的概率問題。

2.3.1 亞穩態發生概率

由上面分析得知,系統亞穩態發生的都是由於clk的Tsu和Th不滿足,又或者是復位訊號的移除和恢復時間不滿足。常用FPGA器件的Tsu+Th約等於1ns,復位移除和恢復時間相加約等於1ns。

當非同步訊號不是一組資料,或者訊號量較少,那就需要對非同步訊號進行同步處理,例如對一個非同步脈衝訊號進行採集,只要脈衝訊號變化發生在時鐘Tsu和Th視窗內,那就很可能會產生亞穩態,亞穩態產生的概率大概為:

概率 = (建立時間 + 保持時間)/ 採集時鐘週期 (公式3-1)

由公式3-1可以看出,隨著clk頻率的增加,亞穩態發生的機率是增加的。

例如,為系統採用100M時鐘對一個外部訊號進行採集,採集時鐘週期為10ns,那採集產生亞穩態的概率為:1ns/10ns = 10%

同理採用300M時鐘對一個外部訊號進行採集,那產生亞穩態的概率為:1ns/3.3ns = 30%

如果採用三相相位差為120°的時鐘對一個外部訊號進行採集,那產生亞穩態的概率接近90%

所以在非同步訊號採集過程中,要想減少亞穩態發生的概率:

(1) 降低系統工作時鐘,增大系統週期,亞穩態概率就會減小;

(2) 採用工藝更好的FPGA,也就是Tsu和Th時間較小的FPGA器件;

2.3.2 亞穩態的串擾概率

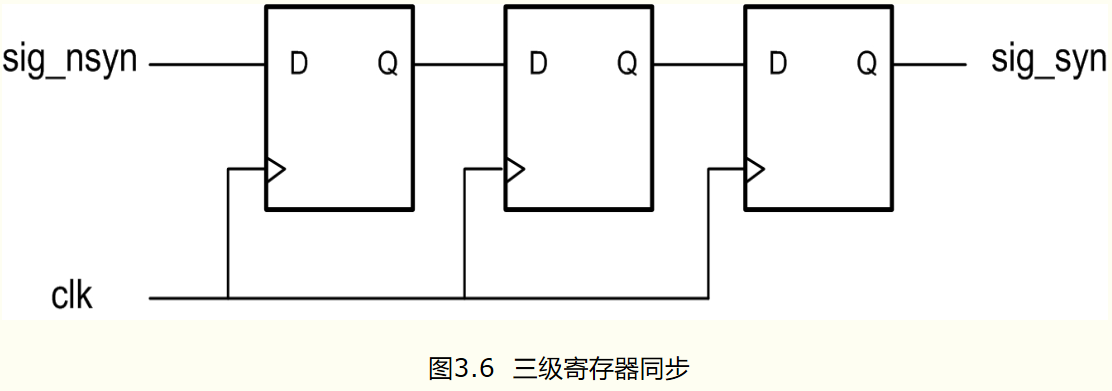

使用非同步訊號進行使用的時候,好的設計都會對非同步訊號進行同步處理,同步一般採用多級D觸發器級聯處理,如圖2.6所示,採用三級D觸發器對非同步訊號進行同步處理。

圖2.6 三級暫存器同步

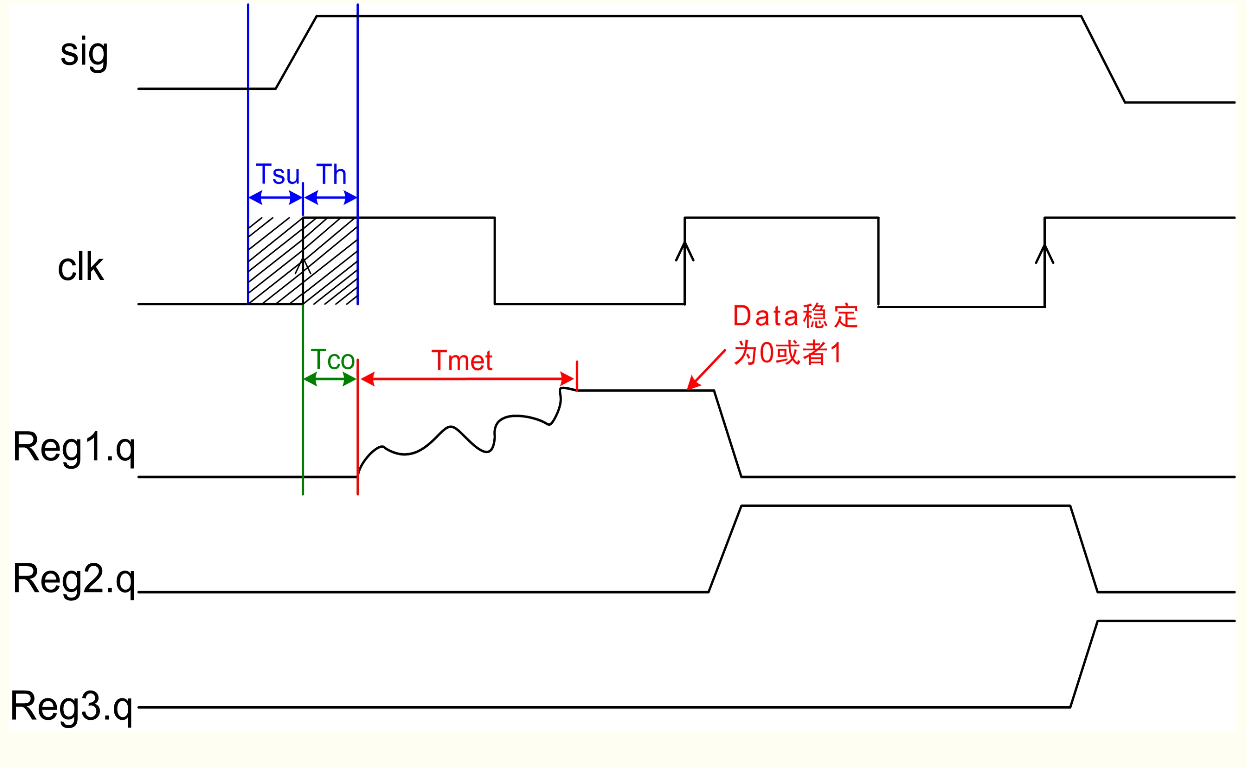

圖2.6 三級暫存器同步這種模型大部分資料都說的是第一級暫存器產生亞穩態後,第二級暫存器穩定輸出概率為90%,第三極暫存器穩定輸出的概率為99%,如果亞穩態跟隨電路一直傳遞下去,那就會另自我修護能力較弱的系統直接崩潰。接下來我們分析這種串擾的概率問題。

如圖2.7所示為一個正常第一級暫存器發生了亞穩態,第二級、第三極暫存器消除亞穩態時序模型。

圖2.7 三級暫存器消除亞穩態

圖2.7 三級暫存器消除亞穩態由上圖可以看出,當第一個暫存器發生亞穩態後,經過Tmet的振盪穩定後,第二級暫存器能採集到一個穩定的值。但是為什麼第二級暫存器還是可能會產生亞穩態呢?

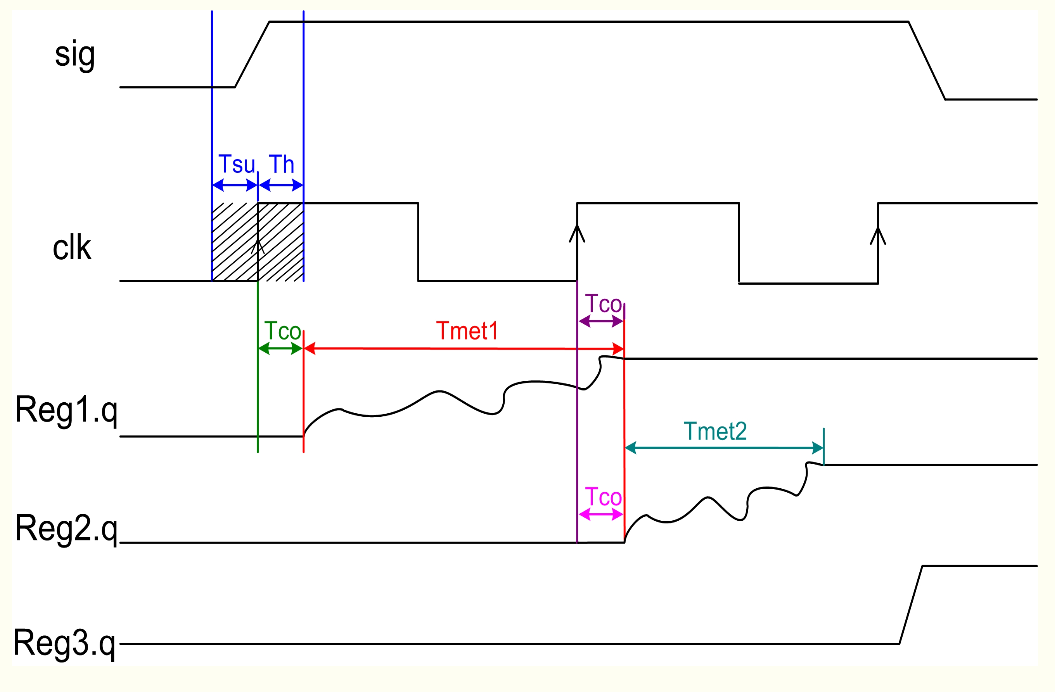

由於振盪時間Tmet是受到很多因素影響的,所以Tmet時間又長有短,所以當Tmet時間長到大於一個採集週期後,那第二級暫存器就會採集到亞穩態。如圖2.8所示。 圖2.8 二級暫存器亞穩態 由上圖可知,第二級也是一個亞穩態,所以在這種情況下,亞穩態產生了串擾,從第一級暫存器傳到了第二級暫存器,同樣也可能從第二級暫存器串擾到第三級暫存器。這樣會讓設計邏輯判斷出錯,產生亞穩態傳輸,可能導致系統宕機奔潰。

圖2.8 二級暫存器亞穩態 由上圖可知,第二級也是一個亞穩態,所以在這種情況下,亞穩態產生了串擾,從第一級暫存器傳到了第二級暫存器,同樣也可能從第二級暫存器串擾到第三級暫存器。這樣會讓設計邏輯判斷出錯,產生亞穩態傳輸,可能導致系統宕機奔潰。2.3.3 亞穩態振盪時間Tmet

亞穩態震盪時間Tmet關係到後級暫存器的採集穩定問題,Tmet影響因素包括:器件的生產工藝、溫度、環境以及暫存器採集到亞穩態離穩定態的時刻等。甚至某些特定條件,如干擾、輻射等都會造成Tmet增長。

3. 應用分析

有亞穩態產生,我們就要對亞穩態進行消除,常用對亞穩態消除有三種方式:

(1) 對非同步訊號進行同步處理;

(2) 採用FIFO對跨時鐘域資料通訊進行緩衝設計;

(3) 對復位電路採用非同步復位、同步釋放方式處理。

3.1.1 對非同步訊號進行同步提取邊沿

在非同步通訊或者跨時鐘域通訊過程中,最常用的就是對非同步訊號進行同步提取邊沿處理。對一個非同步訊號進行提取上升沿通常採用程式清單 4.1所示。

程式清單 4.1 雙極暫存器提取邊沿

input sig_nsyn;

wire sig_nsyn_p;

reg[1:0] sig_nsyn_r;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) sig_nsyn_r <= 2’d0;

else sig_nsyn_r <= { sig_nsyn_r [0], sig_nsyn };

end

assign sig_nsyn_p = sig_nsyn_r[0] & ~sig_nsyn_r[1];

這種邊沿提取方式對於一個穩定的系統是不合適的,例如:當第一級暫存器採集到亞穩態,那勢必造成sig_nsyn_p輸出亞穩態,這樣就會對採用sig_nsyn_p的訊號進行判斷的電路造成影響,甚至判斷出錯誤的值。

根據3.3.1小節的亞穩態產生概率,如果在100M時種下那第一級暫存器產生亞穩態的概率約為10%,隨著系統採集頻率升高,那產生亞穩態的概率也會隨之上升。因此,在進行非同步訊號跨頻提取邊沿時候,一般採用多進行一級暫存器消除亞穩態,可能在系統穩定性要求高的情況下,採用更多級暫存器來消除亞穩態,如程式清單 4.2所示,即為採用4級暫存器消除亞穩態,相應的邊沿訊號產生的時間就晚了兩個時鐘週期。

程式清單 4.2 多級暫存器提取邊沿訊號

input sig_nsyn;

wire sig_nsyn_p;

reg[3:0] sig_nsyn_r;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) sig_nsyn_r <= 2’d0;

else sig_nsyn_r <= { sig_nsyn_r [2::0], sig_nsyn };

end

assign sig_nsyn_p = sig_nsyn_r[2] & ~sig_nsyn_r[3];

3.1.2 FIFO進行非同步跨頻資料處理

當資料流從一個時鐘域到另一個時鐘域的時候,絕大多數情況下都採用FIFO來作為中間緩衝,採用雙時鐘對資料緩衝,就可以避免亞穩態的發生。

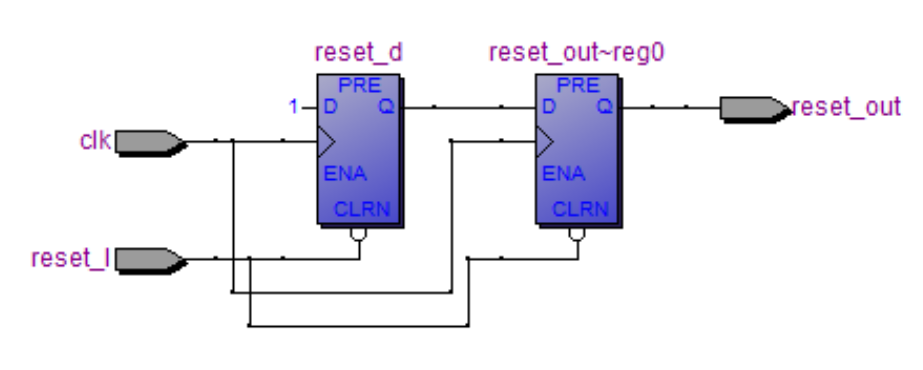

3.1.3 非同步復位,同步釋放

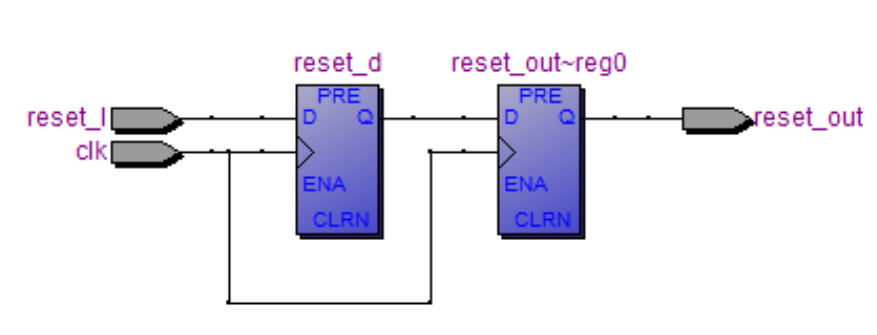

對於復位情況下的亞穩態,常常是由於恢復時間和移除時鐘不滿足造成的,因此,最常用的處理方式是採用非同步復位、同步釋放。常用電路模型如所示。採用第二級暫存器輸出作為全域性復位訊號輸出。

程式清單 4.3 非同步復位處理

wire sys_rst_n;

reg [1:0] rst_r;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) rst_r <= 2’d0;

else rst_r <= {rst_r[0], 1’b1};

end

assign sys_rst_n = rst_r[1];

通過上面三種方式處理非同步訊號、非同步資料、以及非同步復位可有效的提高系統的穩定性。減少亞穩態的產生. 通常我們使用復位訊號有這幾種方式:(1)非同步復位 [email protected](posedeg clk or negedge rst_n)(2)同步復位 module system_ctr (input clk ,

input reset_l ,

output reg reset_out

);

reg reset_d ;

always @ (posedge clk )

begin

reset_d <= reset_l ;

reset_out<= reset_d ;

end

endmodule

reset_out訊號是已經同步過的復位訊號,可以直接在其它模組使用。需要注意的是,這個復位訊號會延遲幾個時鐘週期。並且,復位訊號必須要大於時鐘週期,才能被系統檢測到。(3)非同步復位同步釋放

reset_out訊號是已經同步過的復位訊號,可以直接在其它模組使用。需要注意的是,這個復位訊號會延遲幾個時鐘週期。並且,復位訊號必須要大於時鐘週期,才能被系統檢測到。(3)非同步復位同步釋放reset_out訊號是已經同步過的復位訊號,可以直接在其它模組使用。需要注意的是,這個復位訊號會延遲幾個時鐘週期。並且,復位訊號必須要大於時鐘週期,才能被系統檢測到。

module test(

input reset_l ,

output reg reset_out

);

reg reset_d ;

always @ (posedge clk or negedge reset_l)

begin

if(!reset_l)begin

reset_out <= 1'b0 ;

reset_d <= 1'b0 ;

end

else begin

reset_d <= 1'b1 ;

reset_out <= reset_d ;

end

end

endmodule

這個電路圖就是理解非同步復位、同步釋放的關鍵了。這裡的復位訊號直接接到D觸發器的非同步清零端,也就不存在同步復位中復位訊號必須要大於時鐘週期才能被檢測到的侷限。這就是非同步復位的意思。同時,reset_out變為高電平是受時鐘控制的,也就是所說的同步釋放。同步釋放避免了非同步復位可能產生的不滿足復位恢復時間的情況。綜上所述,非同步復位同步釋放機制解決了非同步復位和同步復位固有的缺陷,因此將這種方法作為系統復位是極好的選擇。

這個電路圖就是理解非同步復位、同步釋放的關鍵了。這裡的復位訊號直接接到D觸發器的非同步清零端,也就不存在同步復位中復位訊號必須要大於時鐘週期才能被檢測到的侷限。這就是非同步復位的意思。同時,reset_out變為高電平是受時鐘控制的,也就是所說的同步釋放。同步釋放避免了非同步復位可能產生的不滿足復位恢復時間的情況。綜上所述,非同步復位同步釋放機制解決了非同步復位和同步復位固有的缺陷,因此將這種方法作為系統復位是極好的選擇。

相關推薦

亞穩態的產生機理、消除辦法

本文是由網上的資料整合而成1. 應用背景1.1 亞穩態發生原因 在FPGA系統中,如果資料傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位訊號的釋放相對於有效時鐘沿的恢復時間(recovery time)不滿足,就可能產生亞穩態,此時觸發器

數字系統中的亞穩態及其解決辦法

本文轉自https://www.cnblogs.com/xiaoxie2014/p/4149565.html1. 應用背景1.1 亞穩態發生原因 在FPGA系統中,如果資料傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位訊號的釋放相對於有效

非同步FIFO跨時鐘域亞穩態如何解決?

跨時鐘域的問題:前一篇已經提到要通過比較讀寫指標來判斷產生讀空和寫滿訊號,但是讀指標是屬於讀時鐘域的,寫指標是屬於寫時鐘域的,而非同步FIFO的讀寫時鐘域不同,是非同步的,要是將讀時鐘域的讀指標與寫時鐘域的寫指標不做任何處理直接比較肯定是錯誤的,因此我們需要進行同步處理以

關於亞穩態的總結

1. 什麼是亞穩態? 亞穩態是違背了觸發器的建立和保持時間而產生的。設計中任何觸發器都有特定的建立和保持時間,在時鐘上升沿前後的這段時間視窗內,資料輸入訊號必須保持穩定。如果訊號在這段時間發生了變化,那麼輸出將是未知的或者稱為“亞穩的”。這種有害的傳播就叫做亞穩態。 當觸

減少亞穩態導致錯誤,提高系統的MTBF

1.亞穩態與設計可靠性 設計數位電路時大家都知道同步是非常重要的,特別當要輸入一個訊號到一個同步電路中,但是該訊號由另一個時鐘驅動時,這是要在介面處採取一些措施,使輸入的非同步訊號同步化,否則電路將無法正常工作,因為輸入端很可能出現亞穩態(Metastability),導致

FPGA基礎知識13(二級D觸發器應用於同步器,減少亞穩態)

需求說明:IC設計基礎 內容 :第一部分 關於兩級D觸發器減小亞穩態的原因 第二部分 關於亞穩態的討論 來自 :時間的詩 第一部分 關於同步器為什麼需要二級D觸發器的疑問 上週,在做VGA介面顯

android ANR產生情況、發生原因及解決辦法

ANR (Application Not Responding) ANR定義:在Android上,如果你的應用程式有一段時間響應不夠靈敏,系統會向用戶顯示一個對話方塊,這個對話方塊稱作應用程式無響應(ANR:Application Not Respondi

JDBC中向數據庫錄入漢字產生亂碼的解決辦法

方法 char jdb host 解決 sql 不能 enc color 在近期的課程設計中遇到在eclipse中向數據庫中錄入數據,產生的漢字亂碼現象,在這裏提供一條解決的方法: 只需連接地址URL中數據庫名後面添加“?characterEncoding=utf-8”即可

FPGA中亞穩態相關問題及跨時鐘域處理

設計 時鐘 比特 產生 solution 至少 nbsp 觸發器 路徑規劃 前言 觸發器輸入端口的數據在時間窗口內發生變化,會導致時序違例。觸發器的輸出在一段時間內徘徊在一個中間電平,既不是0也不是1。這段時間稱為決斷時間(resolution time)。經過resolu

css基礎 BFC 不與浮動元素產生交集、自適應

order src 效果 css基礎 border htm log 學習 w3c 禮悟: 公恒學思合行悟,尊師重道存感恩。葉見尋根三返一,江河湖海同一體。 虛懷若谷良心主,願行無悔給最苦。讀書鍛煉養身心,誠勸且行且珍惜。

多態(upcast)減少分支判斷 以及 多態繼承設計、具體類型判斷。

ret ada ati 改變 over post () 子類 cto Influenced by 《java 八榮八恥》,翻了下《java編程思想》 印象中多態產生的條件:1.子類繼承父類 2.父類【指針】指向子類 3.父類引用調用重寫(@Override)方法 *

【轉載】FPGA中亞穩態——讓你無處可逃

時鐘 mage verilog recover always 電路 edge 也會 inpu 1. 應用背景 1.1 亞穩態發生原因 在FPGA系統中,如果數據傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位信號的釋放相對於有效時鐘沿的

在Python3解釋器的交互界面下使用方向鍵產生亂碼的解決辦法

python readline python3 方向鍵 現象: 在python3的解釋器交互界面使用方向鍵會產生類似: [d^[C之類的亂碼.原因: 未使能readline功能解決辦法:yum install -y readline-devel //安裝C的readline相關文件make

解析雙穩態肖特基二極體的設計

肖特基二極體是將P型半導體或者N型半導體與金屬表面襯體互動作用,並最終形成穩定結構,可分為物理吸附型別與化學吸附型別。肖特基二極體由於其獨特的微觀結構而具有整流效應,被廣泛應用於感測器、分子開關、積體電路等諸多電子器件中。現如今,如何降低肖特基高度而且同時又能保持分子的完整性,成為設計高效

解析雙穩態肖特基二極管的設計

因此 nbsp 圖片 專利 als 較差 tle urn 傳感器 肖特基二極管是將P型半導體或者N型半導體與金屬表面襯體交互作用,並最終形成穩定結構,可分為物理吸附類型與化學吸附類型。肖特基二極管由於其獨特的微觀結構而具有整流效應,被廣泛應用於傳感器、分子開關、集成

Numpy攻略:確定穩態

馬爾可夫鏈:被用來描述至少有兩個狀態的系統,指數學中具有馬爾可夫性質的離散事件隨機過程。該過程中,在給定當前知識或資訊的情況下,過去(即當前以前的歷史狀態)對於預測將來(即當前以後的未來狀態)是無關的。此類系統t時刻的狀態僅取決於t-1時刻的狀態。 穩態:在未來某個時刻之後或者從

FPGA中亞穩態——讓你無處可逃

1. 應用背景 1.1 亞穩態發生原因 在FPGA系統中,如果資料傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位訊號的

Luogu3239 HNOI2015 亞瑟王 概率期望、DP

傳送門 由於期望的線性性,我們可以知道:我們所求的期望實際上就是$\sum\limits_i p'_i \times d_i$,其中$p'_i$為$r$輪中打出過第$i$張卡的概率。 如果沒有“一張卡造成傷害後直接結束這一輪”的限制,我們可以很輕鬆的得到$p'_i = 1 - (1-p_i)^r$,但

java去除字符串中重復、不重復、消除重復後字符

rar pre har mov dal imp stat pub move java去除字符串中重復、不重復、消除重復後字符 import java.util.HashSet;import java.util.Set; public class Main { public

VMGSim v10.0 build128 1CD穩態流程模擬+VMGThermo v10.0.180409 1CD熱力學物

DATAKIT CrossManager 2018.4 Win64 1CD CAD檔案格式轉換工具 DATAKIT CrossManager是一款非常好用且功能強大的CAD檔案格式轉換工具,軟體無需安裝CAD或者其它第三方軟體 就可以載入轉換,可以輕鬆將dwf、dxf等格式的