verilog設計交通訊號燈

東西南北四個方向,兩組交通燈輪流交替變換,其中,紅燈時間為30個時間單位,綠燈時間為25個時間單位,黃燈時間為5個時間單位。

原始碼:

1.狀態機

module signal_light(clk,rst,count,light1,light2);

input clk,rst;

input [5:0]count;

output light1,light2;

reg[2:0] light1,light2;

reg[2:0]state;

parameter Idle=3'b000,

S1=3'b001,

S2=3'b010,

S3=3'b011,

S4=3'b100;

begin

if(!rst)

begin

state<=Idle;

light1<=3'b010;

light2<=3'b010;

end

else

case(state)

Idle: if(rst)

begin

state<=S1;

light1<=3'b100;

light2<=3'b001;

end

S1: if(count=='d25)

begin

state<=S2;

light1<=3'b100;

light2<=3'b010;

end

S2: if(count=='d30)

begin

state<=S3;

light1<=3'b001;

light2<=3'b100;

end

S3: if(count=='d55)

begin

state<=S4;

light1<=3'b010;

light2<=3'b100;

end

S4: if(count=='d60)

begin

state<=S1;

light1<=3'b100;

light2<=3'b001;

end

default: state<=Idle;

endcase

end

endmodule

2.計數器

module counter(clk,rst,count);

output count;

input clk,rst;

reg[5:0] count;

[email protected](posedge clk or negedge rst)

begin

if(!rst)

count<='d0;

else if(count<'d60)

count<=count+1;

else

count<='d1;

end

endmodule

3.頂層

module signal_light_top(count,clk,rst,light1,light2);

input clk,rst;

output[2:0] light1,light2;

output[5:0]count;wire[5:0] count;

counter u2(clk,rst,count);

signal_light u1(clk,rst,count,light1,light2);

endmodule

測試:

module traffic_lights_tb;

reg clk,rst;

wire[2:0] light1,light2;

wire[5:0]count;

signal_light_top u3(count,clk,rst,light1,light2);

always

#5 clk=~clk;

initial

begin

clk<=1;

rst<=0;

#5 rst<=1;

end

endmodule

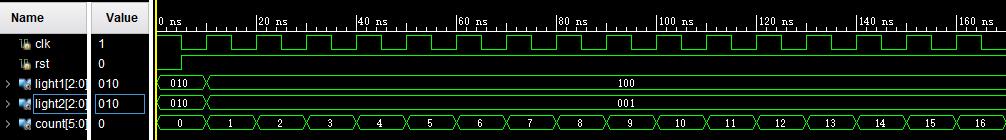

模擬:

相關推薦

verilog設計交通訊號燈

東西南北四個方向,兩組交通燈輪流交替變換,其中,紅燈時間為30個時間單位,綠燈時間為25個時間單位,黃燈時間為5個時間單位。原始碼:1.狀態機module signal_light(clk,rst,count,light1,light2); input clk,r

【CPU微架構設計】利用Verilog設計基於飽和計數器和BTB的分支預測器

在基於流水線(pipeline)的微處理器中,分支預測單元(Branch Predictor Unit)是一個重要的功能部件,它負責收集和分析分支/跳轉指令的引數和執行結果,當處理新的分支/跳轉指令時,BPU將根據已有的統計結果和當前分支跳轉指令的引數,預測其執行結果,為流水線取指提供決策依據,進而提高流

序列FIR濾波器---Verilog設計

數字濾波器 數字濾波器從實現結構上劃分,有FIR和IIR兩種。FIR的特點是:線性相位、消耗資源多;IIR的特點是:非線性相位、消耗資源少。由於FIR系統的線性相位特點,設計中絕大多數情況都採用FIR濾波器。 線性相位系統的意義,這裡的線性相位指的是在設計者關心的通帶範圍內,LTI系

交通訊號燈CE認證怎麼做

手機IP防水等級怎麼劃分,怎麼認證 摘要:交通訊號燈CE認證要求,EN 12368: 2015標準解讀 交通訊號燈產品申請CE證書需要符合的歐盟法規: Construction products (CPR) Regulation (EU) No 305/2011 交

FPGA數字訊號處理(三)序列FIR濾波器Verilog設計

該篇是FPGA數字訊號處理的第三篇,選題為DSP系統中極其常用的FIR濾波器。本文將在上一篇“FPGA數字訊號處理(二)並行FIR濾波器Verilog設計” https://blog.csdn.net/fpgadesigner/article/details/8

Verilog設計的原則和技巧和IP核的使用

FPGA設計原則 1、面積與速度折中(Area&speed tradeoff) 面積和速度是晶片設計中一對相互制約、影響成本和效能的指標,貫穿FPGA設計的始終。在FPGA內

【51微控制器學習筆記】基於STC89C52製作的交通訊號燈

一、簡介 近來學(玩)了下已經好久沒碰的51,心血來潮自己DIY了一個交通訊號燈模型。沒有什麼創新之處,就是復(dao)習(gu)復(dao)習(gu)了下51的定時器中斷、外部中斷以及最小系統電路,熟悉了下74HC595的用法和數碼管。因為好久沒碰51了導致數

用VHDL設計交通燈

一. 程式程式碼 1. 分頻模組 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY fen_pin IS PORT( CLK : IN STD_LOGIC;

用verilog設計一數字鐘系統

二.設計一數字鐘系統,要求如下: 1. 有基礎的實時數字鐘功能,即時,分,秒的正常顯示模式。(24小時制) 2. 可對系統用手動方式校準,設計兩個按鍵,按動校時鍵,時計數器加一,按動校分鍵,則電路處於校分狀態。 3. 整點報時,要求在59分50秒,52秒,54秒,56秒和5

十字路口交通訊號燈問題之程式碼實現

在上一篇部落格<<十字路口交通訊號燈問題之需求解析>>中介紹了程式的需求,這篇部落格將給大家介紹程式碼如何實現,實現中沒有實現GUI,只是對十字路口交通訊號燈的邏輯進行了簡單的

模擬交通訊號燈(Java)

題目描述: 編寫一個窗體應用程式模擬交通訊號燈。 在視窗北邊建立一個下拉列表,該下拉列表有“紅燈”,“黃燈”,“綠燈”三個選項,在視窗的中心建立一塊畫布,當用戶在下拉列表中選擇某項時,畫布上顯示對應

交通訊號燈識別公開資料集 Traffic Lights Recognition (TLR) public benchmarks

In order to publish your performance on this webpage, please send us the result of your algorithm on the above described sequences. The “recognition resu

Verilog HDL程序設計——基本要素

blog 邏輯 轉義字符 移位 關鍵字 加法 取余 邏輯或 html Verilog基本上熟悉了,繼續整理一下Verilog的學習筆記吧。前面記載了Verilog的結構,寫Verilog的結構有了,但是該怎麽寫呢?在寫之前就得了解一下Verilog的一些基本要素了,也就

華東交通大學2017年ACM“雙基”程序設計競賽 1002

roo 解法 out 偶數 男女 不知道 大學 交通 spa Problem Description 一天YZW參加了學校組織交際舞活動,活動的開始活動方分別給男生和女生從1-n進行編號,按照從小到大順時針的方式進行男女搭檔分配,相同編號的男女組合成一對,例如一號男生與一

華東交通大學2017年ACM“雙基”程序設計競賽 1001

put inner 輸入 ret inpu script style input ros Problem Description 最近流行吃雞,那就直接輸出一行"Winner winner ,chicken dinner!"(沒有雙引號)模板代碼:#include <

華東交通大學2017年ACM“雙基”程序設計競賽 1005

esc define names 矩陣 ros matrix 末尾 pan output Problem Description 假設你有一個矩陣,有這樣的運算A^(n+1) = A^(n)*A (*代表矩陣乘法)現在已知一個n*n矩陣A,S = A+A^2+A^3+..

華東交通大學2017年ACM“雙基”程序設計競賽 1008

col pan 數據 problem 表示 proc leo turn mem Problem Description 長度為 n 的序列,把它劃分成兩段非空的子序列,定義權值為:兩段子序列的最大值的差的絕對值。求可能的最大的權值。數據範圍:2 <= n <=

華東交通大學2017年ACM“雙基”程序設計競賽 1003

size 小球 problem cout output () add 兩個 ace Problem Description 有兩個球在長度為L的直線跑道上運動,兩端為墻。0時刻小球a以1m/s的速度從起點向終點運動,t時刻小球b以相同的速度從終點向起點運動。問T時刻兩球的

華東交通大學2017年ACM雙基程序設計大賽題解

top his int back i+1 mem 跳舞 n-k 中一 簡單題 Time Limit : 3000/1000ms (Java/Other) Memory Limit : 65535/32768K (Java/Other) Total Submission(

邊沿檢測電路設計verilog

reg hold住 同時 mage double 取反 比較 檢測 https Abstract 邊沿檢測電路(edge detection circuit)是個常用的基本電路。 Introduction 所謂邊沿檢測就是對前一個clock狀態和目前clock狀態的比較,如