FPGA在AD採集中的應用

AD轉換,也叫模數轉換,是將模擬訊號轉換為數字訊號。目前包括電腦CPU,ARM,FPGA,處理的訊號都只能是數字訊號,所以資料訊號在進入處理晶片前必須要進行AD轉換。

在高速的AD轉換中,FPGA以其高速的處理能力,並行的執行結構,豐富的IO資源,往往承擔者不可替代的作用。

下面給出一個實際的設計方案。

AD晶片的時鐘為25M,FPGA內部系統時鐘頻率為100M,FPGA內部處理AD資料的處理模組需要8個時鐘週期才能處理完一個數據。

根據上述給出的條件,我們可以知道。按正常思路設計方案,肯定會造成AD資料的丟失,為什麼會丟失資料,試想一下,FPGA處理一個數據需要8個時鐘週期,才能採集下一個資料,這樣算下來AD需要的時鐘是12.5M,而給定的AD時鐘是25M,所以肯定會漏掉資料。

根據分析,可以採用乒乓操作通過快取降低資料取樣率。

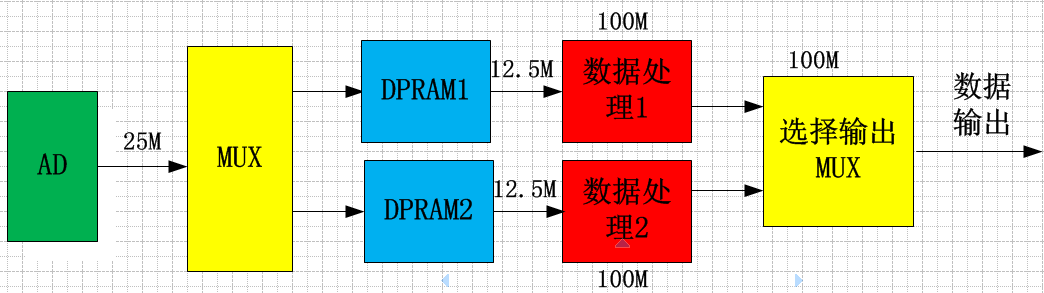

乒乓操作如下圖:

具體乒乓操作為什麼能夠降低資料速率,這裡將不做詳細介紹。

以上方案可以滿足上述處理AD資料的需求。

緊接著繼續增加需求條件,要求資料處理需要連續,不能打亂順序,前面資料的處理會影響後續資料處理。這樣乒乓操作將不適合,具體原因,讀者可以自己想一下(乒乓操作會以資料塊打亂資料順序)。

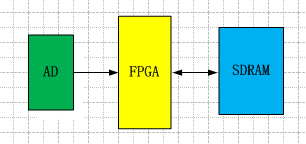

根據上述條件,設計方案需要修改。可以外加儲存器,FPGA片上儲存器資源有限。

新增SDRAM提高儲存速度和儲存量。

繼續新增需求,如果AD資料連續不斷,那麼勢必是造成SDRAM溢位。那麼上述設計方案也不可採取了。

最後根據條件,資料需要連續處理,後面資料的處理要根據前面資料的處理狀態決定,而且資料連續不斷。

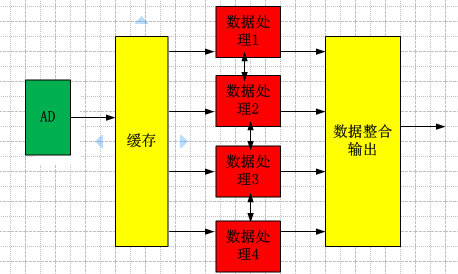

為了滿足時序要求,並且不能遺漏資料,重新對方案進行設計。

將資料處理模組分成幾個小的處理模組。不僅降低資料處理速率,同時個處理模組之間相互聯絡,後續資料處理能夠知道前面資料處理的狀態。最終將處理後的資料順序輸出即可。

文章來源:卿萃科技FPGA極客空間 微信公眾號

版權所有權歸卿萃科技,轉載請註明出處。