給串列埠模組加入FIFO

阿新 • • 發佈:2019-01-28

根據Dvm-gli的部落格(彬哥的論壇),彬哥的串列埠傳送程式在使用者需要連續進行資料傳送時,使用起來不方便,因為每傳送一個數據,都要給出一個相應的傳送脈衝。這時可以在使用者和uart_transfer之間加入一個fifo模組,使用者只需要把要傳送的資料寫入fifo,自動由uart_transfer模組進行傳送,這樣使用上方便一些。

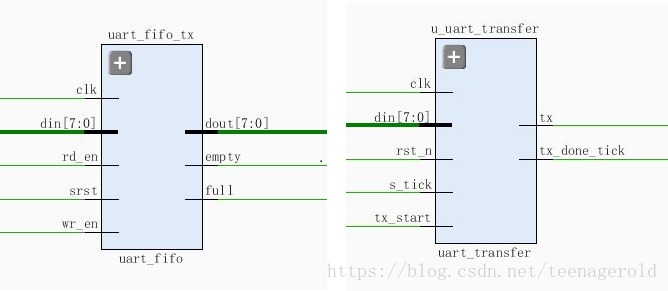

主要埠如下,

需要注意的訊號有兩個,一個是uart_transfer在什麼時候去讀取fifo_tx,另外一個是什麼時候給uart_fifo傳送tx_start(傳送使能)訊號。

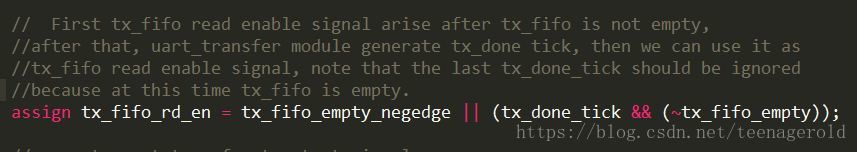

對於fifo_tx的讀取使能rd_en,我們這樣處理:(1)在fifo_tx不為空的時候,empty會有一個從高電平到低電平的跳變,我們使用下降沿檢測電路作為首個rx_en的使能訊號。(2)接下來,資料從fifo_tx的dout引腳輸出,接入uart_transfer的din引腳,給出傳送使能訊號tx_start,傳送完成後產生tx_done_tick傳送完成脈衝訊號,以後我們就使用tx_done_tick作為fifo_tx的讀取使能訊號rd_en。需要注意的是在最後一個數據從fifo_tx輸出後,empty拉高,fifo_tx此時已空,那麼最後一個tx_done_tick產生時fifo_tx早已空,故最後一個tx_done_tick不能使用。綜上,我們可以得出fifo_tx的讀取使能訊號rd_en的產生形式如下:

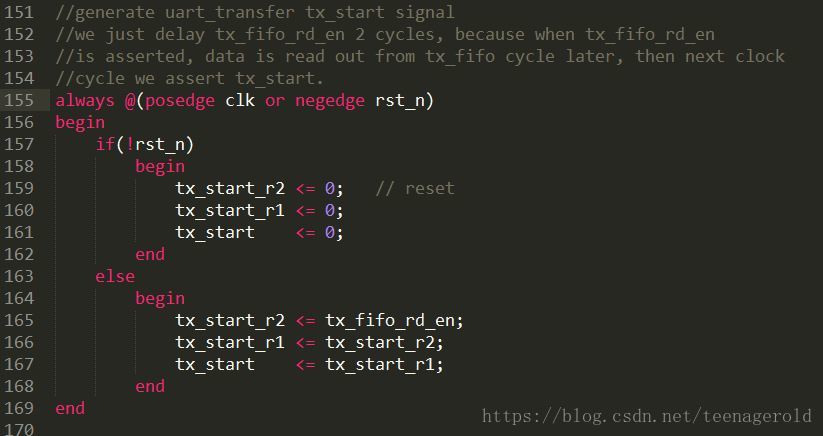

對於串列埠傳送模組的傳送使能訊號tx_start,根據Xilinx的FIFO IP核文件的描述,在rd_en訊號為高的的下一個時鐘週期,資料從dout輸出。為了使資料在tx_start使能訊號有效前穩定下來,我們將rd_en訊號打慢兩拍,作為tx_start訊號。