建立時間和保持時間(1)

Setup 和Hold (建立時間和保持時間)解析(1)

本文是第一篇,有空會繼續更新。(轉載請註明出處!!!)

STA分析是基於同步電路設計模型的,在資料輸入端,假設外部也是同時鐘的暫存器的輸出並且經過若干組合邏輯進入本級,而輸出也被認為是驅動後一級的同時鐘的暫存器。在不設定約束的情況下,純組合邏輯的輸入->輸出不得超過一個T,否則也會被認為是Timing violation.

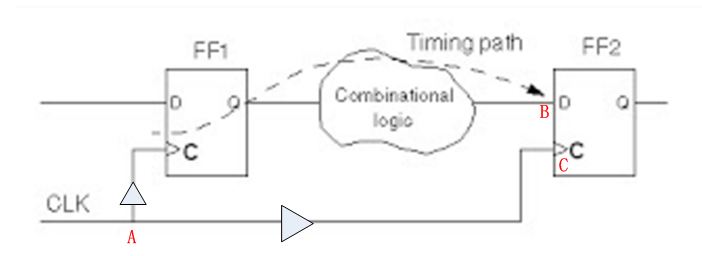

1. Timing path

Timing path就是時間線。Timing就是從起始位置的時間點到終點位置的時間點之間的時間長度。Path是指跟位置相關,即時間起始或終點的位置。Timing path就是某位置的某一時間點到另一位置的某個時間點。對於DFF來說,上升沿類似於一瞬間的脈衝,只有在這短短的一瞬間,資料才允許通過。對於DFF來說,有兩個輸入點:資料D和時鐘CK,有一個輸出點:資料Q。由於是時間比較,所以對於

Data path: A->clk_tree_buf1->FF1-C -> FF1-Q -> Comb_logic -> B

而對於FF2來說只要滿足下個週期的上升沿能夠取樣即可,所以時鐘到達FF2-C的路徑是:

Clk path: A -> clk_tree_buf2-> C.

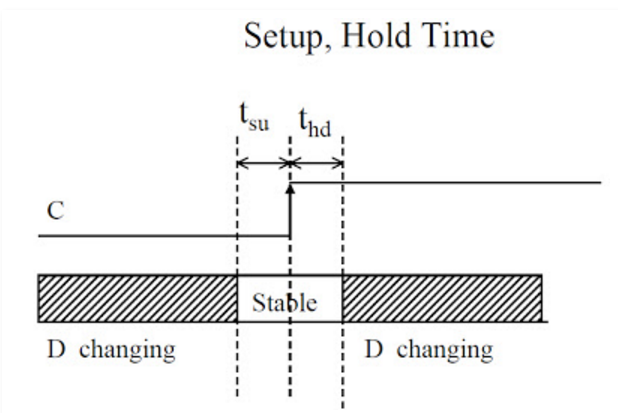

2. 什麼是建立時間和保持時間?

對於某個DFF來說,建立時間和保持時間可以認為是此器件固有的屬性。有關DFF的內部結構及setup和hold時間對應的邏輯閘會在其他文章中進行細緻描述。

在理想情況下,只要在時鐘沿來臨時,有效資料也來臨(時鐘沿之前或同時),則能夠正確採集到資料;而在時鐘沿之後(或同時),即使資料發生變化,也不會影響DFF的輸出了。然而在實際中,上升沿開啟開關需要時間,邏輯閘的狀態改變(電容充放電等)都需要時間,因此資料的採集是需要一定時間的,在這個時間內資料不能發生變化。上升沿時候開關關閉也需要時間,如果在這個時間段內資料有變化的話,那麼新資料就有可能被傳遞到下一級,進而發生錯誤,所以資料必須保持一定時間不變。

總而言之在DFF的輸入埠上看,

- 在clk上升沿來之前,資料必須提前一個最小時間量“預先準備好”,這個最小時間量就是建立時間;

- 在clk上升沿來之後,資料必須保持一個最小時間量“不能變化”,這個最小時間量就是保持時間。

3. 建立和保持時間要求、及其公式

滿足建立和保持時間要求,電路狀態改變就是正確的,電路功能就不會發生錯誤;如果不滿足,電容就沒有足夠的時間充放電,造輸出點的電平可能既非0也非1,造成“亞穩態“輸出。如果前級驅動夠強勁,電路就能按照趨勢變化下去,一定時間後該點的值就會變化為“正確值”,如果驅動不夠強勁,電路就會恢復之前的值,最終得到何值是不可控的,所以我們要避免亞穩態。在使用DFF時,必須滿足其建立時間和保持時間的要求。

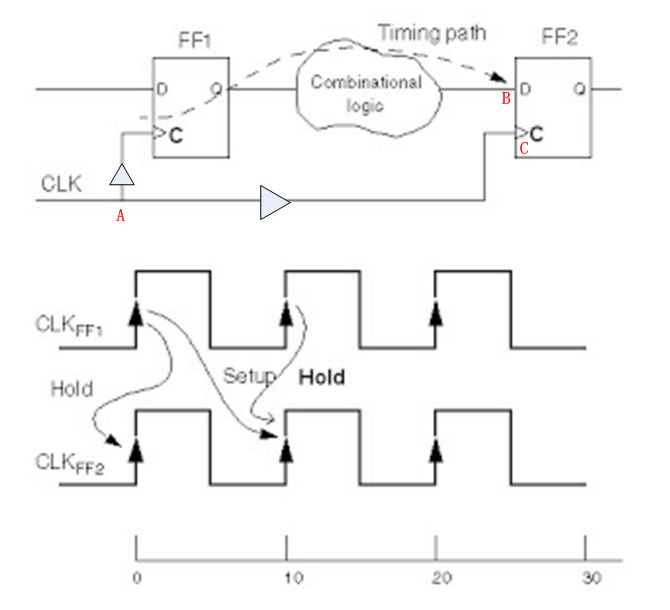

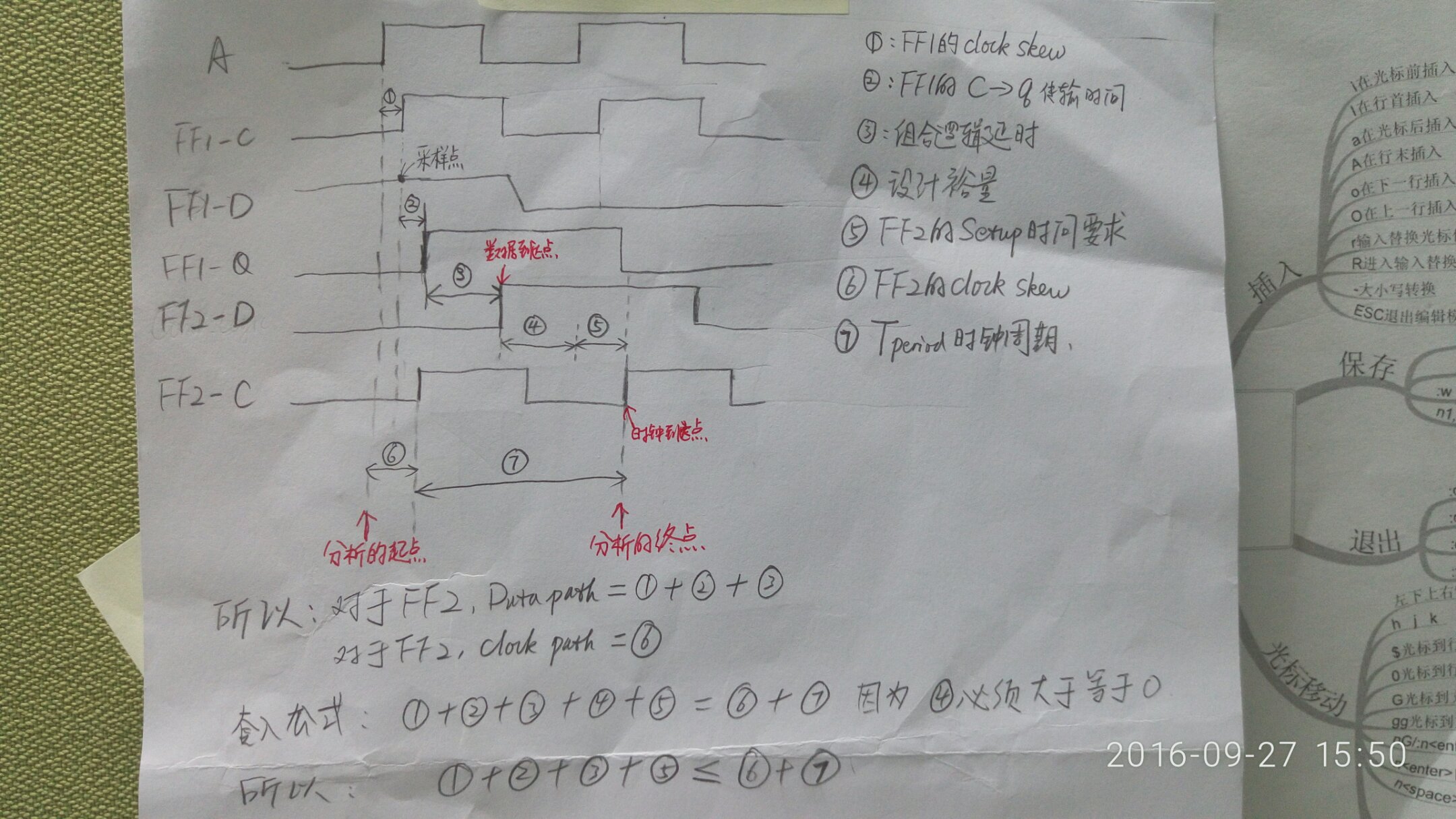

現在在回頭分析data path和clk path,假設t0時刻FF1採集到資料並傳遞給FF2,那麼FF2只要在t10上升沿採到資料即可,所以資料有一整個Tperiod的時間來傳遞到FF2-D端。因為要滿足建立時間要求,所以對於FF2來說,資料要比時鐘“走得快”:

Tdata_path+ Tsetup <= Tclk_path+ Tperiod

所以

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic+ Tsetup <= Tclk_delay_FF2 +Tperiod

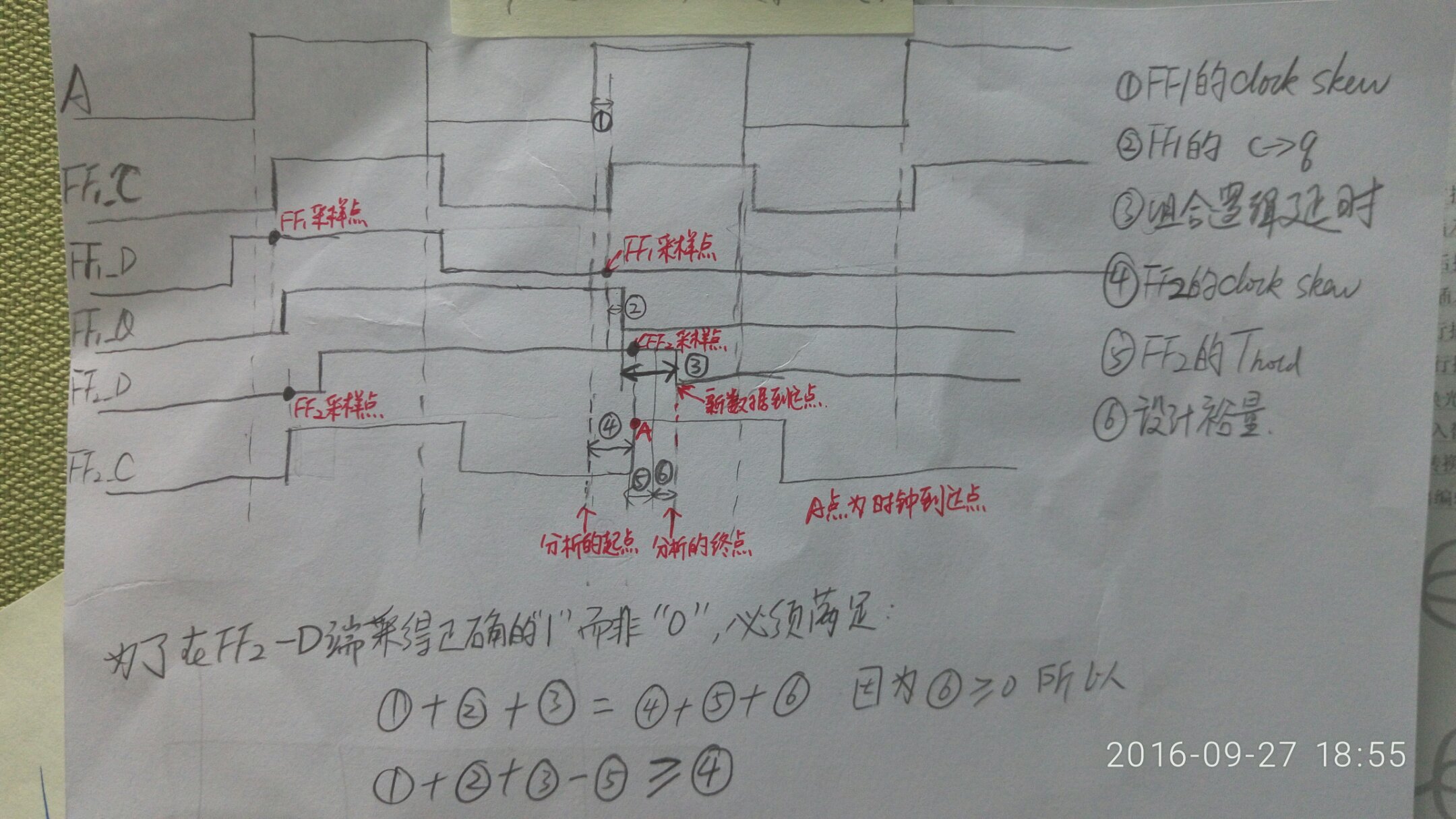

在分析STA時,不滿足此公式的即為setup violation。對應時序圖的分析,見下圖:

保持時間比較難理解,其實質是當前時鐘沿的FF1輸出不能太快在當前沿到達FF2。以上圖為例,即在t10時刻,為防止FF1採到的新資料太快到達FF2而“沖掉”原來的正確資料,資料必須要在一定時間之後才允許到達,所以保持時間分析,分析的是FF1和FF2的同一個時鐘沿。因為datapath和clk_path要滿足保持時間要求,所以

Tdata_path– Thold >= Tclk_path

所以:

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic– Thold >= Tclk_delay_FF2

在STA分析時,不滿足此公式的即為Holdviolation。

其中Tclk_skew =Tclk_delay_FF2– Tclk_delay_FF1. 這條公式在分析Tskew時用得上。

對應於時序圖,見如下圖的分析:

4. 實際電路的Setup和Hold公式及violation分析

因為在不同的情形下,例如不同的溫度,電壓,loading等等,每一段電路的delay是不同的,所以對於同一段電路,其delay可以在如下範圍中:

Min_delay<= Delay <= max_delay

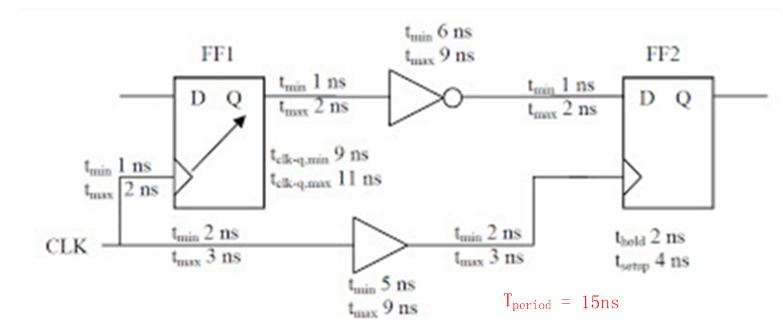

如下圖:

建立時間

公式為: Tclk_delay_FF1 + Tc->q_FF1+Tcomb_logic + Tsetup <= Tclk_delay_FF2 + Tperiod

應該滿足MAX_data_path_delay + Tsetup <= MIN_clk_path_delay + Tperiod,才能保證電路是可靠的。所以在實際電路中:

Tdata_path_max+ Tsetup <= Tclk_path_min+ Tperiod

對應上圖,該公式應該是:

2ns+ 11ns + 2ns + 9ns + 2ns + 4ns <= 2ns + 5ns + 2ns + Tperiod

所以: 30 <= 9 + 15.因為違反了該公式,所以該電路出現了setup violation。

保持時間

公式為: Tclk_delay_FF1 + Tc->q_FF1 + Tcomb_logic –Thold>= Tclk_delay_FF2

應該滿足MIN_data_path_delay – Thold>= MAX_clk_path_delay.才能保證電路是可靠的。所以在實際電路中:

Tdata_path_min- Thold >= Tclk_path_max

對應上圖,該公式應該是:

1ns +9ns + 1ns + 6ns + 1ns – 2ns >= 3ns + 9ns + 3ns

所以: 16ns >= 15ns,滿足公司要求,所以該電路無holdviolation。

在某些電路中,可以認為clk tree上面沒有延遲,可以認為wire沒有延遲,那麼setup和hold公式就得到簡化。