FPGA開發基本流程

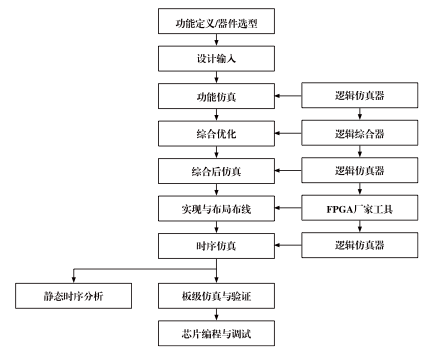

FPGA的設計流程就是利用EDA開發軟體和程式設計工具對FPGA晶片進行開發的過程。典型FPGA的開發流程一般如圖1所示,包括功能定義/器件選型、設計輸入、功能模擬、綜合優化、綜合後模擬、實現、佈線後模擬、板級模擬以及晶片程式設計與除錯等主要步驟。

圖1 FPGA典型設計流程

1、功能定義/器件選型

在FPGA設計專案開始之前,必須有系統功能的定義和模組的劃分,另外就是要根據任務要求,如系統的功能和複雜度,對工作速度和器件本身的資源、成本、以及連線的可布性等方面進行權衡,選擇合適的設計方案和合適的器件型別。 一般都採用自頂向下的設計方法,把系統分成若干個基本單元,然後再把每個基本單元劃分為下一層次的基本單元,一直這樣做下去,直到可以直接使用EDA元件庫為止。

2、 設計輸入

設計輸入是將所設計的系統或電路以開發軟體要求的某種形式表示出來,並輸入給EDA工具的過程。常用的方法有硬體描述語言(HDL)和原理圖輸入方法等。原理圖輸入方式是一種最直接的描述方式,在可程式設計晶片發展的早期應用比較廣泛,它將所需的器件從元件庫中調出來,畫出原理圖。這種方法雖然直觀並易於模擬,但效率很低,且不易維護,不利於模組構造和重用。更主要的缺點是可移植性差,當晶片升級後,所有的原理圖都需要作一定的改動。目前,在實際開發中應用最廣的就是HDL語言輸入法,利用文字描述設計,可以分為普通HDL和行為HDL。普通HDL有ABEL、CUR等,支援邏輯方程、真值表和狀態機等表達方式,主要用於簡單的小型設計。而在中大型工程中,主要使用行為HDL,其主流語言是Verilog HDL和VHDL。這兩種語言都是美國電氣與電子工程師協會(IEEE)的標準,其共同的突出特點有:語言與晶片工藝無關,利於自頂向下設計,便於模組的劃分與移植,可移植性好,具有很強的邏輯描述和模擬功能,而且輸入效率很高。 除了這IEEE標準語言外,還有廠商自己的語言。也可以用HDL為主,原理圖為輔的混合設計方式,以發揮兩者的各自特色。

3、 功能模擬

功能模擬也稱為前模擬是在編譯之前對使用者所設計的電路進行邏輯功能驗證,此時的模擬沒有延遲資訊,僅對初步的功能進行檢測。模擬前,要先利用波形編輯器和HDL等建立波形檔案和測試向量(即將所關心的輸入訊號組合成序列),模擬結果將會生成報告檔案和輸出訊號波形,從中便可以觀察各個節點訊號的變化。如果發現錯誤,則返回設計修改邏輯設計。常用的工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS和Cadence公司的NC-Verilog以及NC-VHDL等軟體。

4、 綜合優化

所謂綜合就是將較高階抽象層次的描述轉化成較低層次的描述。綜合優化根據目標與要求優化所生成的邏輯連線,使層次設計平面化,供FPGA佈局佈線軟體進行實現。就目前的層次來看,綜合優化(Synthesis)是指將設計輸入編譯成由與門、或門、非門、RAM、觸發器等基本邏輯單元組成的邏輯連線網表,而並非真實的門級電路。真實具體的門級電路需要利用FPGA製造商的佈局佈線功能,根據綜合後生成的標準門級結構網表來產生。為了能轉換成標準的門級結構網表,HDL程式的編寫必須符合特定綜合器所要求的風格。由於門級結構、RTL級的HDL程式的綜合是很成熟的技術,所有的綜合器都可以支援到這一級別的綜合。常用的綜合工具有Synplicity公司的Synplify/Synplify Pro軟體以及各個FPGA廠家自己推出的綜合開發工具。

5、 綜合後模擬

綜合後模擬檢查綜合結果是否和原設計一致。在模擬時,把綜合生成的標準延時檔案反標註到綜合模擬模型中去,可估計門延時帶來的影響。但這一步驟不能估計線延時,因此和佈線後的實際情況還有一定的差距,並不十分準確。目前的綜合工具較為成熟,對於一般的設計可以省略這一步,但如果在佈局佈線後發現電路結構和設計意圖不符,則需要回溯到綜合後模擬來確認問題之所在。在功能模擬中介紹的軟體工具一般都支援綜合後模擬。

6、 實現與佈局佈線

佈局佈線可理解為利用實現工具把邏輯對映到目標器件結構的資源中,決定邏輯的最佳佈局,選擇邏輯與輸入輸出功能連結的佈線通道進行連線,併產生相應檔案(如配置檔案與相關報告),實現是將綜合生成的邏輯網表配置到具體的FPGA晶片上,佈局佈線是其中最重要的過程。佈局將邏輯網表中的硬體原語和底層單元合理地配置到晶片內部的固有硬體結構上,並且往往需要在速度最優和麵積最優之間作出選擇。佈線根據佈局的拓撲結構,利用晶片內部的各種連線資源,合理正確地連線各個元件。目前,FPGA的結構非常複雜,特別是在有時序約束條件時,需要利用時序驅動的引擎進行佈局佈線。佈線結束後,軟體工具會自動生成報告,提供有關設計中各部分資源的使用情況。由於只有FPGA晶片生產商對晶片結構最為了解,所以佈局佈線必須選擇晶片開發商提供的工具。

7、 時序模擬

時序模擬,也稱為後模擬,是指將佈局佈線的延時資訊反標註到設計網表中來檢測有無時序違規(即不滿足時序約束條件或器件固有的時序規則,如建立時間、保持時間等)現象。時序模擬包含的延遲資訊最全,也最精確,能較好地反映晶片的實際工作情況。由於不同晶片的內部延時不一樣,不同的佈局佈線方案也給延時帶來不同的影響。因此在佈局佈線後,通過對系統和各個模組進行時序模擬,分析其時序關係,估計系統性能,以及檢查和消除競爭冒險是非常有必要的。在功能模擬中介紹的軟體工具一般都支援綜合後模擬。

8、 板級模擬與驗證

板級模擬主要應用於高速電路設計中,對高速系統的訊號完整性、電磁干擾等特徵進行分析,一般都以第三方工具進行模擬和驗證。

9、 晶片程式設計與除錯

設計的最後一步就是晶片程式設計與除錯。晶片程式設計是指產生使用的資料檔案(位資料流檔案,Bitstream Generation),然後將程式設計資料下載到FPGA晶片中。其中,晶片程式設計需要滿足一定的條件,如程式設計電壓、程式設計時序和程式設計演算法等方面。邏輯分析儀(Logic Analyzer,LA)是FPGA設計的主要除錯工具,但需要引出大量的測試管腳,且LA價格昂貴。目前,主流的FPGA晶片生產商都提供了內嵌的線上邏輯分析儀(如Xilinx ISE中的ChipScope、Altera QuartusII中的SignalTapII以及SignalProb)來解決上述矛盾,它們只需要佔用晶片少量的邏輯資源,具有很高的實用價值。

補充:基於FPGA的SOC設計方法

目前,由於FPGA效能提升價格下降,同時嵌入越來越多核心,很自然地,很多IC設計公司將FPGA用於ASIC原型驗證,把FPGA可程式設計的優點帶到了SOC領域,其系統由嵌入式處理器核心、DSP單元、大容量處理器、吉位元收發器、混合邏輯、IP 以及原有的設計部分組成。

SOC 平臺的核心部分是內嵌的處理核心,其硬體是固定的,軟體則是可程式設計的;外圍電路則由FPGA的邏輯資源組成,大都以IP 的形式提供,例如儲存器介面、USB介面以及乙太網MAC層介面等,使用者根據自己需要在核心總線上新增,並能自己訂製相應的介面IP 和外圍裝置。