51微控制器匯流排時序

一、匯流排概述

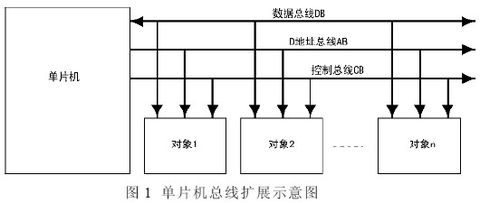

計算機系統是以微處理器為核心的,各器件要與微處理器相連,且必須協調工作,所以在微處理機中引入了匯流排的概念,各器件共同享用匯流排,任何時候只能有一個器件傳送資料(可以有多個器件同時接收資料) 。

計算機的匯流排分為控制匯流排、地址匯流排和資料匯流排等三種。而資料匯流排用於傳送資料,控制匯流排用於傳送控制訊號, 地址匯流排則用於選擇儲存單元或外設。

二、微控制器的三匯流排結構

51系列微控制器具有完善的匯流排介面時序,可以擴充套件控制物件,其直接定址能力達到64k( 2的16次方) 。在匯流排模式下,不同的物件共享匯流排,獨立編址、分時複用匯流排,CPU 通過地址選擇訪問的物件,完成與各物件之間的資訊傳遞。

微控制器三匯流排擴充套件示意如圖1 所示。

1、資料匯流排

51 微控制器的資料匯流排為P0 口,P0 口為雙向資料通道,CPU 從P0 口送出和讀回資料。

2、地址匯流排

51 系列微控制器的地址匯流排為16 位。

為了節約晶片引腳,採用P0 口複用方式,除了作為資料匯流排外,在ALE 訊號時序匹配下,通過外接的資料鎖存器,在匯流排訪問前半週期從P0口送出低8位地址,後半週期從P0 口送出8 位資料。

高8位地址則通過P2 口送出。

3、控制匯流排

51 系列微控制器的控制匯流排包括讀控制訊號P3.7 和寫控制訊號P3.6 等,二者分別作為匯流排模式下資料讀和資料寫的使能訊號。

三、微控制器匯流排時序分析

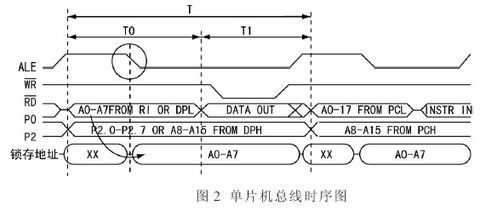

51 微控制器匯流排時序如圖2 所示。

從圖2 中可以看出,完成一次匯流排( 讀寫) 操作週期為T,P0 口分時複用,在T0 期間,P0 口送出低8 位地址,在ALE 的下降沿完成資料鎖存,送出低8位地址訊號。在T1 期間,P0 口作為資料匯流排使用,送出或讀入資料,資料的讀寫操作在讀、寫控制訊號的低電平期間完成。

需要注意的是,在控制訊號( 讀、寫訊號) 有效期間,P2 口送出高8位地址,配合資料鎖存器輸出的低8 位地址,實現16 位地址匯流排,即64kB 範圍的內的定址。

由於CPU不可能同時執行讀和寫操作,所以讀、寫訊號不可能同時有效。

四、常見微控制器編址電路

1、簡單地址擴充套件

51 微控制器的P2 口可以直接作為高8位地址匯流排使用,在一些簡單系統電路中,常使用P2口直接編址驅動。

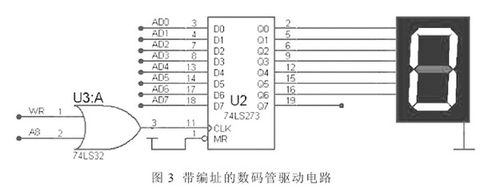

下面以使用資料緩衝器74LS273 驅動數碼顯示為例,分析P2 口編址驅動的靜態數碼顯示電路的設計。

一位LED 數碼顯示單元電路如圖3 所示。

WR 與A8( P2.0) 相或提供74LS273的時鐘訊號,當執行“MOVX @DPTR,A”指令時,地址資訊由DPTR 暫存器確定,會出現有效的寫訊號WR,只有當地址A8 為滿足“0”時,寫訊號才可以作為74LS273 的時鐘訊號輸入,完成資料鎖存。

P2 口為A8~A15 的8 位地址線,很容易擴充套件到8 只LED 數碼管,WR 訊號分別與A8~A15 按或關係連線,每位地址線均為低電平有效,即可實現8 個有效地址。

該方案電路簡單,但有效地址數太少,不適用於複雜系統設計。

2、低8 位地址鎖存

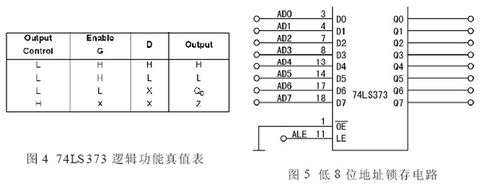

通常的設計電路是使用8D 鎖存器74LS373 實現地址鎖存,74HC573 與之邏輯功能相同,只是引腳佈局不一樣,使用74HC573 佈線更容易。

74LS373 真值表如圖4所示。

在輸出允許OE 為L、控制使能LE 為H 時,輸出為跟隨狀態;

OE 為L、LE 為L 時,輸出為保持狀態。

地址鎖存電路如圖5 所示。OE 接地,LE 接微控制器的ALE腳將產生滿足時序的低8 位地址訊號。

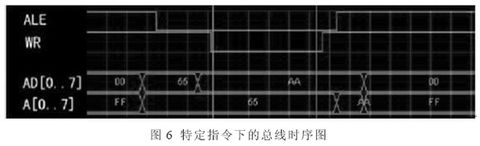

執行以下三條指令會得到如圖6所示的時序圖。

MOV DPTR,# 0FF55H; 低8 位地址為55H

MOV A,# 0AAH; 待發送資料0AAH→A( 55H 取反)

MOVX,@DPTR,A; A 中的0AAH送地址為0FF55H 的物件中會。

從圖6 中可以看出,P0 口先送55H,在ALE 下降沿實現地址鎖存,隨後送出資料0AAH,在WR 有效( 低電平) 期間鎖存器輸出低8 位地址55H,P0 口送出資料0AAH。

3、帶譯碼器的複雜地址介面電路

理論上高8 位地址線可以產生256 個有效地址,如何實現地址“擴充套件”呢? 地址擴充套件準確描述是地址譯碼,例如3 根地址線可以譯碼成8 個地址,4根譯碼成16 個有效地址。這裡選擇3-8 譯碼器實現地址譯碼,電路圖以及對應的編址如表1 所示。

五、微控制器匯流排編址電路例項

帶匯流排擴充套件介面的微控制器系統,包括外部32k RAM 擴充套件、LCD1602 介面、輸入輸出口。

帶編址擴充套件的微控制器最小系統電路如圖7 所示。

使用74HC573 鎖存低8 位地址;74138 實現8 個地址擴充套件,74138 的A、B、C 接A8 ~A10,E1 接A15, E2、E3 接地常有效,得到0F8FFH 到0FFFFH8 個地址( 無關位用1 表示) 或者8000H 到8700H( 無關位用0 表示) 。

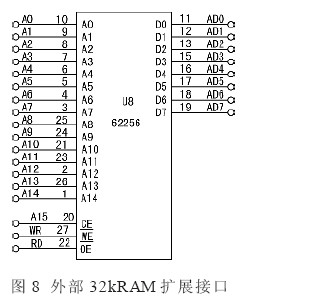

32k RAM 介面如圖8 所示。

D0~D7 接資料匯流排P0 口,地址線A0~A14接微控制器地址匯流排低15 位,微控制器地址線A15 接RAM 片選訊號,低電平有效,這樣RAM 地址分配從0000H 到7FFFH,與74138 譯碼地址不衝突。

LCD1602 介面電路如圖9 所示。

RS、RW 分別接A12、A13,使能訊號編址為Y7,這樣LCD 的四個驅動地址( 資料讀寫和命令讀寫) 為0CFFFH 到0FFFFH ( 無關位為1) 或者8700H 到0B700H( 無關位為0)。

有些時候微控制器引腳不夠用,還要進行擴充套件,輸入口擴充套件電路如圖10 所示。

利用74HC573( 74LS373) 的高阻態功能,將其輸出Q0~Q7 接P0 口,在滿足匯流排地址讀操作中,可以把輸入InPORT的資料讀入微控制器的累加器,地址為0F8FFH 或8000H。

輸出口擴充套件電路如圖11 所示。

利用74LS273 資料鎖存功能,在滿足匯流排地址寫操作中,可以把微控制器累加器裡的資料寫入273 鎖存輸出,地址為0F8FFH 或8000H。由於所用控制匯流排不同,可以和輸入共用地址。

六、結束語

匯流排擴充套件是設計微控制器控制電路必須掌握的技術,大量的特殊功能IC都支援匯流排介面, 如ADC0809,TLC7528,DDS 器件AD9851 等。

匯流排介面的要點就是在嚴格的控制時序下,匯流排被分時複用,以實現複雜系統設計。