STM32的時鐘樹解析

阿新 • • 發佈:2019-02-02

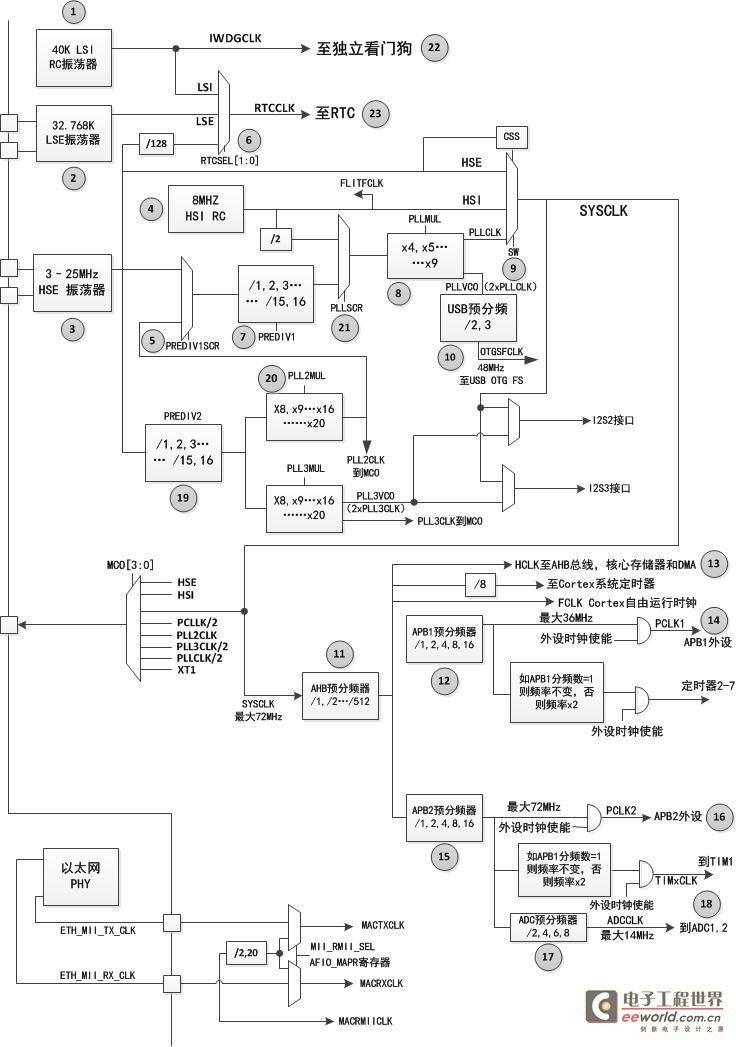

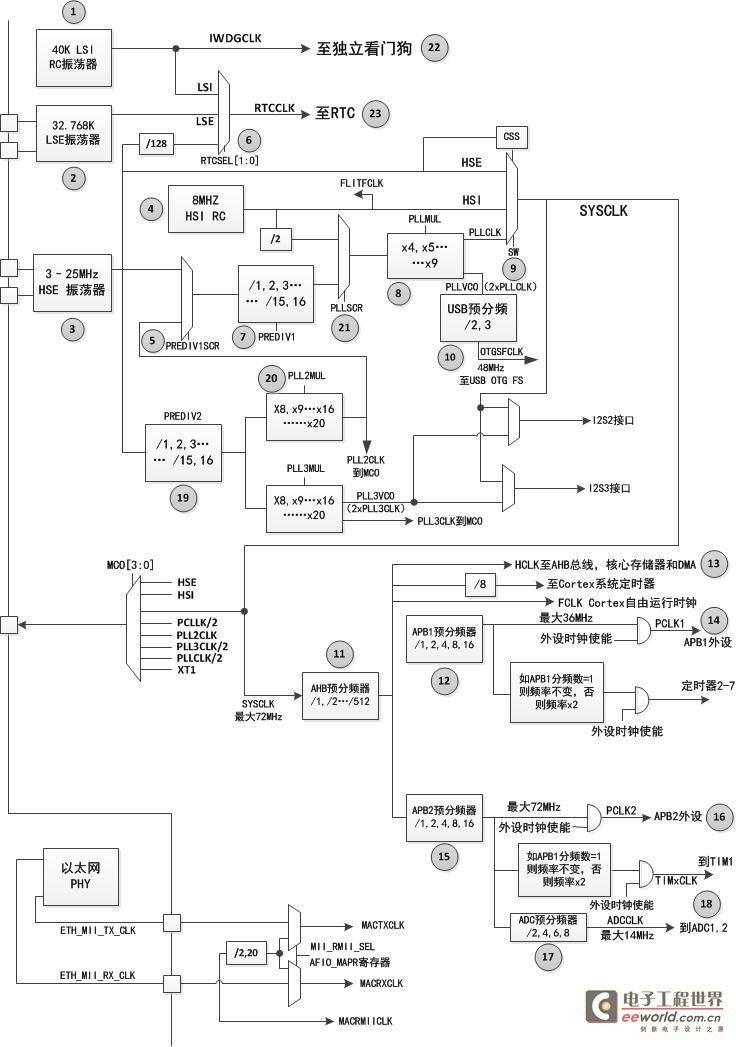

STM32的時鐘樹 對於廣大初次接觸STM32的讀者朋友(甚至是初次接觸ARM器件的讀者朋友)來說,在熟悉了開發環境的使用之後,往往“栽倒”在同一個問題上。這問題有個關鍵字叫:時鐘樹。 眾所周知,微控制器(處理器)的執行必須要依賴週期性的時鐘脈衝來驅動——往往由一個外部晶體振盪器提供時鐘輸入為始,最終轉換為多個外部裝置的週期性運作為末,這種時鐘“能量”擴散流動的路徑,猶如大樹的養分通過主幹流向各個分支,因此常稱之為“時鐘樹”。在一些傳統的低端8位微控制器諸如51,AVR,PIC等微控制器,其也具備自身的一個時鐘樹系統,但其中的絕大部分是不受使用者控制的,亦即在微控制器上電後,時鐘樹就固定在某種不可更改的狀態(假設微控制器處於正常工作的狀態)。比如  圖1 STM32的時鐘樹 在認識這顆時鐘樹之前,首先要明確“主幹”和最終的“分支”。假設使用外部8MHz晶振作為STM32的時鐘輸入源(這也是最常見的一種做法),則這個8MHz便是“主幹”,而“分支”很顯然是最終的外部裝置比如通用輸入輸出裝置(GPIO)。這樣可以輕易找出第一條時鐘的“脈絡”:3——5——7——21——8——9——11——13對此條時鐘路徑做如下解析:對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5,通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於13,時鐘到達AHB匯流排;在上一章節中所介紹的GPIO外設屬於APB2裝置,即GPIO的時鐘來源於APB2匯流排,同樣在圖1中也可以尋獲GPIO外設的時鐘軌跡:3——5——7——21——8——9——11——15——16對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5, 通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於15,設定APB2匯流排分頻數(假設1分頻);對於16,時鐘到達APB2匯流排;現在來計算一下GPIO裝置的最大驅動時鐘速率(各個條件已在上述要點中假設):1) 由3所知晶振輸入為8MHz,由5——21知PLL的時鐘源為經過分頻後的外部晶振時鐘,並且此分頻數為1分頻,因此首先得出PLL的時鐘源為:8MHz / 1 = 8MHz。2) 由8、9知PLL倍頻數為9,且將PLL倍頻後的時鐘輸出選擇為系統時鐘,則得出系統時鐘為 8MHz * 9 = 72MHz。3) 時鐘到達AHB預

圖1 STM32的時鐘樹 在認識這顆時鐘樹之前,首先要明確“主幹”和最終的“分支”。假設使用外部8MHz晶振作為STM32的時鐘輸入源(這也是最常見的一種做法),則這個8MHz便是“主幹”,而“分支”很顯然是最終的外部裝置比如通用輸入輸出裝置(GPIO)。這樣可以輕易找出第一條時鐘的“脈絡”:3——5——7——21——8——9——11——13對此條時鐘路徑做如下解析:對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5,通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於13,時鐘到達AHB匯流排;在上一章節中所介紹的GPIO外設屬於APB2裝置,即GPIO的時鐘來源於APB2匯流排,同樣在圖1中也可以尋獲GPIO外設的時鐘軌跡:3——5——7——21——8——9——11——15——16對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5, 通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於15,設定APB2匯流排分頻數(假設1分頻);對於16,時鐘到達APB2匯流排;現在來計算一下GPIO裝置的最大驅動時鐘速率(各個條件已在上述要點中假設):1) 由3所知晶振輸入為8MHz,由5——21知PLL的時鐘源為經過分頻後的外部晶振時鐘,並且此分頻數為1分頻,因此首先得出PLL的時鐘源為:8MHz / 1 = 8MHz。2) 由8、9知PLL倍頻數為9,且將PLL倍頻後的時鐘輸出選擇為系統時鐘,則得出系統時鐘為 8MHz * 9 = 72MHz。3) 時鐘到達AHB預

圖1 STM32的時鐘樹 在認識這顆時鐘樹之前,首先要明確“主幹”和最終的“分支”。假設使用外部8MHz晶振作為STM32的時鐘輸入源(這也是最常見的一種做法),則這個8MHz便是“主幹”,而“分支”很顯然是最終的外部裝置比如通用輸入輸出裝置(GPIO)。這樣可以輕易找出第一條時鐘的“脈絡”:3——5——7——21——8——9——11——13對此條時鐘路徑做如下解析:對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5,通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於13,時鐘到達AHB匯流排;在上一章節中所介紹的GPIO外設屬於APB2裝置,即GPIO的時鐘來源於APB2匯流排,同樣在圖1中也可以尋獲GPIO外設的時鐘軌跡:3——5——7——21——8——9——11——15——16對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5, 通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於15,設定APB2匯流排分頻數(假設1分頻);對於16,時鐘到達APB2匯流排;現在來計算一下GPIO裝置的最大驅動時鐘速率(各個條件已在上述要點中假設):1) 由3所知晶振輸入為8MHz,由5——21知PLL的時鐘源為經過分頻後的外部晶振時鐘,並且此分頻數為1分頻,因此首先得出PLL的時鐘源為:8MHz / 1 = 8MHz。2) 由8、9知PLL倍頻數為9,且將PLL倍頻後的時鐘輸出選擇為系統時鐘,則得出系統時鐘為 8MHz * 9 = 72MHz。3) 時鐘到達AHB預

圖1 STM32的時鐘樹 在認識這顆時鐘樹之前,首先要明確“主幹”和最終的“分支”。假設使用外部8MHz晶振作為STM32的時鐘輸入源(這也是最常見的一種做法),則這個8MHz便是“主幹”,而“分支”很顯然是最終的外部裝置比如通用輸入輸出裝置(GPIO)。這樣可以輕易找出第一條時鐘的“脈絡”:3——5——7——21——8——9——11——13對此條時鐘路徑做如下解析:對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5,通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於13,時鐘到達AHB匯流排;在上一章節中所介紹的GPIO外設屬於APB2裝置,即GPIO的時鐘來源於APB2匯流排,同樣在圖1中也可以尋獲GPIO外設的時鐘軌跡:3——5——7——21——8——9——11——15——16對於3,首先是外部的3-25MHz(前文已假設為8MHz)輸入;對於5, 通過PLL選擇位預先選擇後續PLL分支的輸入時鐘(假設選擇外部晶振);對於7,設定外部晶振的分頻數(假設1分頻);對於21,選擇PLL倍頻的時鐘源(假設選擇經過分頻後的外部晶振時鐘);對於8,設定PLL倍頻數(假設9倍頻);對於9,選擇系統時鐘源(假設選擇經過PLL倍頻所輸出的時鐘);對於11,設定AHB匯流排分頻數(假設1分頻);對於15,設定APB2匯流排分頻數(假設1分頻);對於16,時鐘到達APB2匯流排;現在來計算一下GPIO裝置的最大驅動時鐘速率(各個條件已在上述要點中假設):1) 由3所知晶振輸入為8MHz,由5——21知PLL的時鐘源為經過分頻後的外部晶振時鐘,並且此分頻數為1分頻,因此首先得出PLL的時鐘源為:8MHz / 1 = 8MHz。2) 由8、9知PLL倍頻數為9,且將PLL倍頻後的時鐘輸出選擇為系統時鐘,則得出系統時鐘為 8MHz * 9 = 72MHz。3) 時鐘到達AHB預