單指令週期CPU---算術操作指令(1)---簡單算術操作指令的實現

程式碼放在github上

在之前實現的基礎上繼續增加了15條簡單算術操作指令(add、addi、addiu、addu、sub、subu、clo、clz、slt、slti、sltiu、sltu、mul、mult、multu)

之前操作的傳送門:

單指令週期ori指令的實現

單指令週期CPU—–邏輯、移位操作和空指令

單指令週期CPU——移動操作指令的實現

指令介紹

MIPS32指令集架構定義的所有算術操作指令,共有21條

共有三類,分別是:

- 簡單算術指令

- 乘累加、乘累減指令

- 除法指令

簡單算術操作指令介紹

一共有15條指令分別是:add、addi、addiu、addu、sub、subu、clo、clz、slt、slti、sltiu、sltu、mul、mult、multu

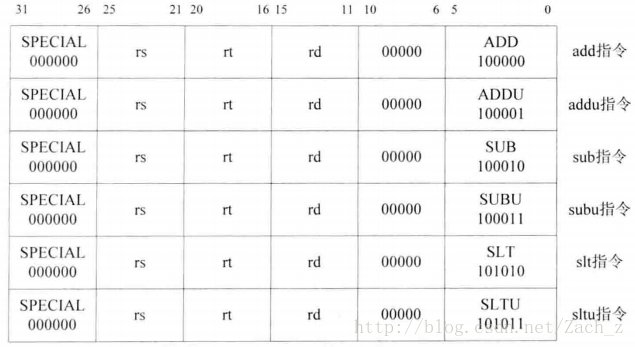

1. add、addu、sub、subu、slt、sltu指令

add、addu、sub、subu、slt、sltu指令格式為:

由指令格式可以看出這六條指令指令碼都是6’b000000即SPECIAL類,而且指令的第6\~10bit都是0,根據指令的功能碼(0\~5bit)來判斷是那一條指令

- ADD(功能碼是6’b100000):加法運算,用法:add rd,rs,rt;作用:rd <- rs+rt,將地址為rs的通用暫存器的值與地址為rt的通用暫存器的值進行加法運算,結果儲存到地址為rd的通用暫存器中。如果加法運算溢位,那麼會產生溢位異常,同時不儲存結果。

- ADDU(功能碼是6’b100001)

- SUB(功能碼是6’b100010):減法運算,用法:sub rd,rs,rt; 作用:rd <- rs-rt,將地址為rs的通用暫存器的值與地址為rt的通用暫存器的值進行減法運算,結果儲存到地址為rd的通用暫存器中。如果減法運算溢位,那麼產生溢位異常,同時不儲存結果。

- SUBU(功能碼是6’b100011):減法運算,用法:subu rd,rs,rt; 作用:rd <- rs-rt將地址為rs的通用暫存器的值與地址為rt的通用暫存器的值進行減法運算,結果儲存到地址為rd的通用暫存器中。不進行溢位檢查,總是將結果儲存到目的暫存器。

- SLT(功能碼是6’b101010):比較運算,用法:slt rd,rs,rt; 作用:rd <- (rs

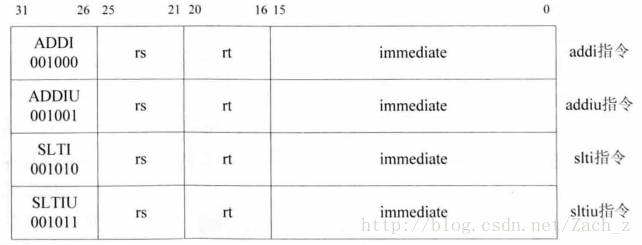

2. addi、addiu、slti、sltiu指令

addi、addiu、slti、sltiu指令格式為:

由指令格式可以看出,依據指令碼(26\~31bit)判斷是哪一種指令

- ADDI(指令碼是6’b001000):加法運算,用法:addi rt,rs,immediate; 作用:rt <- rs+(sign_extended)immediate,將指令中16位立即數進行符號擴充套件,與地址為rs的通用暫存器進行加法運算,結果儲存到地址為rt的通用暫存器。如果加法運算溢位,則產生溢位異常,同時不儲存結果。

- ADDIU(指令碼是6’b001001):加法運算,用法:addiu rt,rs,immediate; 作用:rt <- rs+(sign_extended)immediate,將指令中16位立即數進行符號擴充套件,與地址為rs的通用暫存器進行加法運算,結果儲存到地址為rt的通用暫存器。不進行溢位檢查,總是將結果儲存到目的暫存器。

- SLTI(功能碼是6’b001010):比較運算,用法:slti rt,rs,immediate; 作用:rt <- (rs<(sign_extended)immediate)將指令中的16位立即數進行符號擴充套件,與地址為rs的通用暫存器的值按照有符號數進行比較,若前者小於後者,那麼將1儲存到地址為rt的通用暫存器,若前者大於後者,則將0儲存到地址為rt的通用暫存器中

- SLTIU(功能碼是6’b001011):比較運算,用法:sltiu rt,rs,immediate; 作用:rt <- (rs<(sign_extended)immediate)將指令中的16位立即數進行符號擴充套件,與地址為rs的通用暫存器的值按照無符號數進行比較,若前者小於後者,那麼將1儲存到地址為rt的通用暫存器,若前者大於後者,則將0儲存到地址為rt的通用暫存器中

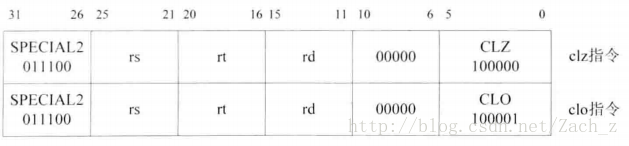

3. clo、clz指令

clo、clz的指令格式:

由指令格式可以看出,這兩條指令的指令碼(26\~31bit)都是6’b011100,即是SPECIAL2類;而且第6\~10bit都為0,根據指令中的功能碼(0\~5bit)判斷是哪一條指令

- CLZ(功能碼是6’b100000):計數運算,用法:clz rd,rs; 作用:rd <- coun_leading_zeros rs,對地址為rs的通用暫存器的值,從最高位開始向最低位方向檢查,直到遇到值為“1”的位,將該為之前“0”的個數儲存到地址為rd的通用暫存器中,如果地址為rs的通用暫存器的所有位都為0(即0x00000000),那麼將32儲存到地址為rd的通用暫存器中

- CLO(功能碼是6’b100001):計數運算,用法:clo,rd,rs; 作用:rd <- coun_leading_zeros rs對地址為rs的通用暫存器的值,從最高位開始向最低位方向檢查,直到遇到值為“0”的位,將該為之前“1”的個數儲存到地址為rd的通用暫存器中,如果地址為rs的通用暫存器的所有位都為1(即0xFFFFFFFF),那麼將32儲存到地址為rd的通用暫存器中

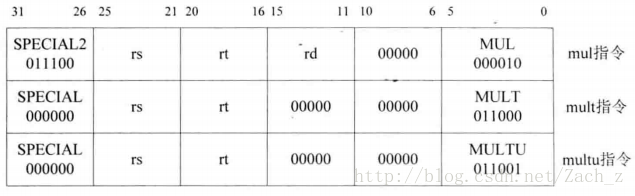

4. multu、mult、mul指令

multu、mult、mul的指令格式:

由指令格式可以看出,mul指令的指令碼(26\~31bit)都是6’b011100,即是SPECIAL2類,mult和multu這兩條指令的指令碼(26\~31bit)都是6’b000000,即是SPECIAL類;有著不同的功能碼(0\~5bit)

- mul(指令碼是SPECIAL2,功能碼是6’b000010):乘法運算,用法:mul,rd,rs,st; 作用:rd <- rs * rt,將地址為rs的通用暫存器的值與地址為rt的通用暫存器的值作為有符號數相乘,乘法結果低32bit儲存到地址為rd的通用暫存器中

- mult(指令碼是SPECIAL,功能碼是6’b011000):乘法運算,用法:mult,rs,st; 作用:{hi,lo} <- rs * rt,將地址為rs的通用暫存器的值與地址為rt的通用暫存器的值作為有符號數相乘,乘法結果低32bit儲存到LO暫存器中,高32bit儲存到HI暫存器中

- multu(指令碼是SPECIAL,功能碼是6’b011001):乘法運算,用法:mult,rs,st; 作用:{hi,lo} <- rs * rt,將地址為rs的通用暫存器的值與地址為rt的通用暫存器的值作為無符號數相乘,乘法結果低32bit儲存到LO暫存器中,高32bit儲存到HI暫存器中

新增相關巨集定義

`define EXE_SLT 6'b101010 //指令SLT的功能碼

`define EXE_SLTU 6'b101011 //指令SLTU的功能碼

`define EXE_SLTI 6'b001010 //指令SLTI的指令碼

`define EXE_SLTIU 6'b001011 //指令SLTIU的指令碼

`define EXE_ADD 6'b100000 //指令ADD的功能碼

`define EXE_ADDU 6'b100001 //指令ADDU的功能碼

`define EXE_SUB 6'b100010 //指令SUB的功能碼

`define EXE_SUBU 6'b100011 //指令SUBU的功能碼

`define EXE_ADDI 6'b001000 //指令ADDI的指令碼

`define EXE_ADDIU 6'b001001 //指令ADDIU的指令碼

`define EXE_CLZ 6'b100000 //指令CLZ的功能碼

`define EXE_CLO 6'b100001 //指令CLO的功能碼

`define EXE_MULT 6'b011000 //指令MULT的功能碼

`define EXE_MULTU 6'b011001 //指令MULTU的功能碼

`define EXE_MUL 6'b000010 //指令MUL的功能碼

`define EXE_SPECIAL2_INST 6'b011100 //special2類的指令碼

//AluOp

`define EXE_SLT_OP 8'b00101010

`define EXE_SLTU_OP 8'b00101011

`define EXE_SLTI_OP 8'b01010111

`define EXE_SLTIU_OP 8'b01011000

`define EXE_ADD_OP 8'b00100000

`define EXE_ADDU_OP 8'b00100001

`define EXE_SUB_OP 8'b00100010

`define EXE_SUBU_OP 8'b00100011

`define EXE_ADDI_OP 8'b01010101

`define EXE_ADDIU_OP 8'b01010110

`define EXE_CLZ_OP 8'b10110000

`define EXE_CLO_OP 8'b10110001

`define EXE_MULT_OP 8'b00011000

`define EXE_MULTU_OP 8'b00011001

`define EXE_MUL_OP 8'b10101001

//AluSel

`define EXE_RES_ARITHMETIC 3'b100

`define EXE_RES_MUL 3'b101修改譯碼階段ID模組

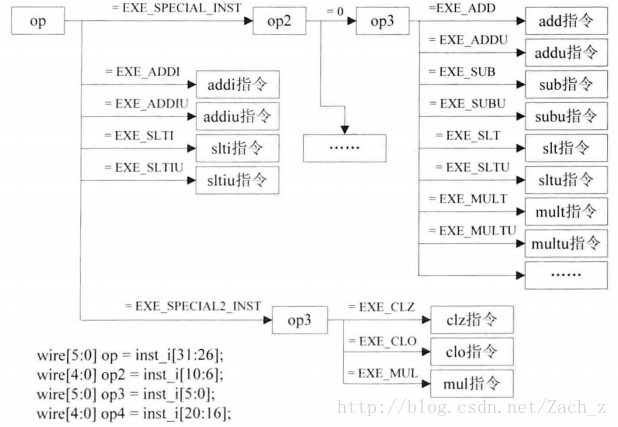

根據指令的指令碼,和功能碼確定是哪一條指令,再由具體的指令給出譯碼結果

case(op)

`EXE_SPECIAL_INST: begin //SPECIAL

case(op2)

5'b00000: begin

case(op3)

...

`EXE_SLT: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLT_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SLTU: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLTU_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_ADD: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADD_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_ADDU: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADDU_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SUB: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SUB_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SUBU: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SUBU_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MULT: begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_MULT_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MULTU: begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_MULTU_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

default: begin

end

endcase //op3

end

default: begin

end

endcase //op2

end //SPECIAL

`EXE_SLTI: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLT_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {{16{inst_i[15]}}, inst_i[15:0]}; wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_SLTIU: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLTU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {{16{inst_i[15]}}, inst_i[15:0]}; wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_ADDI: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADDI_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {{16{inst_i[15]}}, inst_i[15:0]}; wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_ADDIU: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADDIU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {{16{inst_i[15]}}, inst_i[15:0]}; wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_SPECIAL2_INST: begin

case ( op3 )

`EXE_CLZ: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_CLZ_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_CLO: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_CLO_OP;

alusel_o <=`EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_MUL: begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MUL_OP;

alusel_o <= `EXE_RES_MUL;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

default:begin

end

endcase //SPECIAL2 OP3

end//SPECIAL2

...這些簡單算術操作指令的指令操作型別都是EXE_RES_ARITHMETIC

- add、addu、sub、subu、slt、sltu:需要兩個暫存器的值分別作為兩個運算元,所以設定reg1_read_o和reg2_read_o都為1,運算完後結果需要寫入目的暫存器,所以設定wreg_o為WriteEnable,寫入目的暫存器地址wd_o是指令中16\~20bit的值

- addi、addiu、subi、subiu:只需要讀取一個暫存器的值作為第一個運算元,即設定reg1_read_o為1,reg2_read_o為0,第二個運算元為立即數進行符號擴充套件後的值,運算完後結果需要寫入目的暫存器,所以設定wreg_o為WriteEnable,寫入目的暫存器地址wd_o是指令中16\~20bit的值

- mult、multu:需要兩個暫存器的值分別作為兩個運算元,所以設定reg1_read_o和reg2_read_o都為1,運算完後結果需要不需要寫入通用暫存器,而是寫入HI、LO暫存器所以設定wreg_o為WriteDisable

- mul:需要兩個暫存器的值分別作為兩個運算元,所以設定reg1_read_o和reg2_read_o都為1,aluop_o為EXE_MUL_OP運算完後結果需要寫入目的暫存器,所以設定wreg_o為WriteEnable,寫入目的暫存器地址wd_o是指令中11\~15bit的值

- clo、clz:只需要讀取一個暫存器的值作為第一個運算元,即設定reg1_read_o為1,reg2_read_o為0,運算完後結果需要寫入目的暫存器,所以設定wreg_o為WriteEnable,寫入目的暫存器地址wd_o是指令中11\~15bit的值

修改執行階段EX模組

根據譯碼階段的結果,來進行相關的執行操作

1. 新增一些新的變數

reg[`RegBus] arithmeticres; //儲存算術運算結果

wire ov_sum; //儲存溢位情況

wire reg1_eq_reg2; //第一個運算元是否等於第二個運算元

wire reg1_lt_reg2; //第一個運算元是否小於第二個運算元

wire[`RegBus] reg2_i_mux; //儲存輸入的第二個操作reg2_i的補碼

wire[`RegBus] reg1_i_not; //儲存輸入的第一個運算元reg1_i取反後的值

wire[`RegBus] result_sum; //儲存加法結果

wire[`RegBus] opdata1_mult; //乘法操作中的被乘數

wire[`RegBus] opdata2_mult; //乘法操作中的乘數

wire[`DoubleRegBus] hilo_temp; //臨時儲存乘法結果,寬度為64位

reg[`DoubleRegBus] mulres; //儲存乘法結果,寬度為64位2. 計算五個變數的值

2.1 reg2_i_mux

如果是減法或者有符號比較運算,那麼reg2_i_mux等於第二個運算元reg2_i的補碼,否則reg2_i_mux等於第二個運算元reg2_i

assign reg2_i_mux = ((aluop_i == `EXE_SUB_OP) || (aluop_i == `EXE_SUBU_OP) ||

(aluop_i == `EXE_SLT_OP)) ? (~reg2_i)+1 : reg2_i;

2.2 result_sum

- 如果是加法運算,此時reg2_i_mux就是第二個運算元reg2_i,所以result_sum就是加法運算的結果

- 如果是減法運算,此時reg2_i_mux是第二個運算元reg2_i的補碼,所以result_sum就是減法運算的結果

- 如果是有符號比較運算,此時reg2_i_mux也是第二個運算元reg2_i的補碼,所以result_sum也是減法運算的結果,可以通過判斷減法結果是否小於零,進而判斷第一個運算元reg1_i是否小於第二個運算元reg2_i

assign result_sum = reg1_i + reg2_i_mux;2.3 ov_sum

計算是否溢位,加法指令(add和addi)、減法指令(sub)執行的時候,需要判斷是否溢位,滿足一下兩種情況時,有溢位:

- reg1_i為正數,reg2_i_mux為正數,但是兩者之和為負數

- reg1_i為負數,reg2_i_mux為負數,但是兩者之和為正數

assign ov_sum = ((!reg1_i[31] && !reg2_i_mux[31]) && result_sum[31]) ||

((reg1_i[31] && reg2_i_mux[31]) && (!result_sum[31]));2.4 reg1_lt_reg2

計算運算元1是否小於運算元2,分兩種情況

- aluop_i為EXE_SLT_OP表示有符號比較運算:

reg1_i為負數、reg2_i為正數,顯然reg1_i小於reg2_i

reg1_i為正數、reg2_i為正數,並且reg1_i減去reg2_i的值小於0(即result_sum為負),此時也有reg1_i小於reg2_i

reg1_i為負數、reg2_i為負數,並且並且reg1_i減去reg2_i的值小於0(即result_sum為負),此時也有reg1_i小於reg2_i

- 無符號數比較的時候u,直接使用比較運算子比較reg1_i與reg2_i

assign reg1_lt_reg2 = ((aluop_i == `EXE_SLT_OP)) ? ((reg1_i[31] && !reg2_i[31])

|| (!reg1_i[31] && !reg2_i[31] && result_sum[31])

|| (reg1_i[31] && reg2_i[31] && result_sum[31])) : (reg1_i < reg2_i);2.5 reg1_i_not

對運算元1逐位取反,賦給reg1_i_not

assign reg1_i_not = ~reg1_i;3. 依據不同的算術運算型別,給arithmeticres變數賦值

always @ (*) begin

if(rst == `RstEnable)begin

arithmeticres <= `ZeroWord;

end else begin

case(aluop_i)

`EXE_SLT_OP,`EXE_SLTU_OP:begin //比較運算

arithmeticres <= reg1_lt_reg2;

end

`EXE_ADD_OP,`EXE_ADDU_OP,`EXE_ADDI_OP,`EXE_ADDIU_OP:begin //加法運算

arithmeticres <= result_sum;

end

`EXE_SUB_OP,`EXE_SUBU_OP:begin //減法運算

arithmeticres <= result_sum;

end

`EXE_CLZ_OP:begin //計數運算clz

arithmeticres <= reg1_i[31] ? 0 : reg1_i[30] ? 1 : reg1_i[29] ? 2 :

reg1_i[28] ? 3 : reg1_i[27] ? 4 : reg1_i[26] ? 5 :

reg1_i[25] ? 6 : reg1_i[24] ? 7 : reg1_i[23] ? 8 :

reg1_i[22] ? 9 : reg1_i[21] ? 10 : reg1_i[20] ? 11 :

reg1_i[19] ? 12 : reg1_i[18] ? 13 : reg1_i[17] ? 14 :

reg1_i[16] ? 15 : reg1_i[15] ? 16 : reg1_i[14] ? 17 :

reg1_i[13] ? 18 : reg1_i[12] ? 19 : reg1_i[11] ? 20 :

reg1_i[10] ? 21 : reg1_i[9] ? 22 : reg1_i[8] ? 23 :

reg1_i[7] ? 24 : reg1_i[6] ? 25 : reg1_i[5] ? 26 :

reg1_i[4] ? 27 : reg1_i[3] ? 28 : reg1_i[2] ? 29 :

reg1_i[1] ? 30 : reg1_i[0] ? 31 : 32 ;

end

`EXE_CLO_OP:begin //計數運算clo

arithmeticres <= (reg1_i_not[31] ? 0 : reg1_i_not[30] ? 1 : reg1_i_not[29] ? 2 :

reg1_i_not[28] ? 3 : reg1_i_not[27] ? 4 : reg1_i_not[26] ? 5 :

reg1_i_not[25] ? 6 : reg1_i_not[24] ? 7 : reg1_i_not[23] ? 8 :

reg1_i_not[22] ? 9 : reg1_i_not[21] ? 10 : reg1_i_not[20] ? 11 :

reg1_i_not[19] ? 12 : reg1_i_not[18] ? 13 : reg1_i_not[17] ? 14 :

reg1_i_not[16] ? 15 : reg1_i_not[15] ? 16 : reg1_i_not[14] ? 17 :

reg1_i_not[13] ? 18 : reg1_i_not[12] ? 19 : reg1_i_not[11] ? 20 :

reg1_i_not[10] ? 21 : reg1_i_not[9] ? 22 : reg1_i_not[8] ? 23 :

reg1_i_not[7] ? 24 : reg1_i_not[6] ? 25 : reg1_i_not[5] ? 26 :

reg1_i_not[4] ? 27 : reg1_i_not[3] ? 28 : reg1_i_not[2] ? 29 :

reg1_i_not[1] ? 30 : reg1_i_not[0] ? 31 : 32) ;

end

default:begin

arithmeticres <= `ZeroWord;

end

endcase

end

end4. 進行乘法運算

4.1計算opdata1_mult

取得乘法運算的被除數,如果是有符號乘法且被乘數是負數,則取補碼

assign opdata1_mult=(((aluop_i == `EXE_MUL_OP) || (aluop_i == `EXE_MULT_OP))

&& (reg1_i[31] == 1'b1)) ? (~reg1_i + 1) : reg1_i;

4.2 取得乘法運算的除數,如果是有符號乘法且被乘數是負數,則取補碼

assign opdata2_mult=(((aluop_i == `EXE_MUL_OP) || (aluop_i == `EXE_MULT_OP))

&& (reg2_i[31] ==1'b1)) ? (~reg2_i+1) : reg2_i;

4.3 得到臨時乘法結果,儲存變數hilo_temp中

assign hilo_temp = opdata1_mult*opdata2_mult;4.4 對臨時乘法結果進行修正,最終結果儲存在變數mulres中

如果是有符號乘法指令mul、mult:

如果被乘數與乘數一正一負,那麼需要對hilo_temp求補碼,作為最終乘法結果

如果被乘數與乘數同號,那麼hilo_temp的值為最終結果

- 如果是無符號乘法指令,則hilo_temp的值作為最終結果

//對乘法結果修正(A*B)補=A補 * B補

always @ (*) begin

if(rst == `RstEnable) begin

mulres <= {`ZeroWord,`ZeroWord};

end else if ((aluop_i == `EXE_MULT_OP) || (aluop_i == `EXE_MUL_OP))begin

if(reg1_i[31] ^ reg2_i[31] == 1'b1) begin

mulres <= ~hilo_temp + 1;

end else begin

mulres <= hilo_temp;

end

end else begin

mulres <= hilo_temp;

end

end4.5 確定要寫入目的暫存器的資料

always @ (*) begin

wd_o <= wd_i; //要寫的目的暫存器地址

//如果是add、addi、sub、subi、指令,且發生溢位,那麼設定wreg_o為WriteDisable,即不寫暫存器

if(((aluop_i == `EXE_ADD_OP) || (aluop_i == `EXE_ADDI_OP) || (aluop_i == `EXE_SUB_OP)) && (ov_sum == 1'b1)) begin

wreg_o <= `WriteDisable;

end else begin

wreg_o <= wreg_i;

end

case(alusel_i)

`EXE_RES_LOGIC:begin //邏輯運算

wdata_o <= logicout;

end

`EXE_RES_SHIFT:begin //移位運算

wdata_o <= shiftres;

end

`EXE_RES_MOVE: begin //移動運算

wdata_o <= moveres;

end

`EXE_RES_ARITHMETIC:begin //除乘法外簡單算術操作指令

wdata_o <= arithmeticres;

end

`EXE_RES_MUL:begin //乘法指令mul

wdata_o <= mulres[31:0];

end

default:begin

wdata_o<=`ZeroWord;

end

endcase

end4.6 確定對HI、LO暫存器的操作資訊

always @ (*) begin

if(rst == `RstEnable) begin

whilo_o <= `WriteDisable;

hi_o <= `ZeroWord;

lo_o <= `ZeroWord;

end else if((aluop_i == `EXE_MULT_OP) || (aluop_i ==`EXE_MULTU_OP))begin //mult、multu指令

whilo_o <= `WriteEnable;

hi_o <= mulres[63:32];

lo_o <= mulres[31:0];

end else if(aluop_i == `EXE_MTHI_OP) begin

whilo_o <= `WriteEnable;

hi_o <= reg1_i;

lo_o <= LO;

end else if(aluop_i == `EXE_MTLO_OP) begin

whilo_o <= `WriteEnable;

hi_o <= HI;

lo_o <= reg1_i;

end else begin

whilo_o <= `WriteDisable;

hi_o <= `ZeroWord;

lo_o <= `ZeroWord;

end

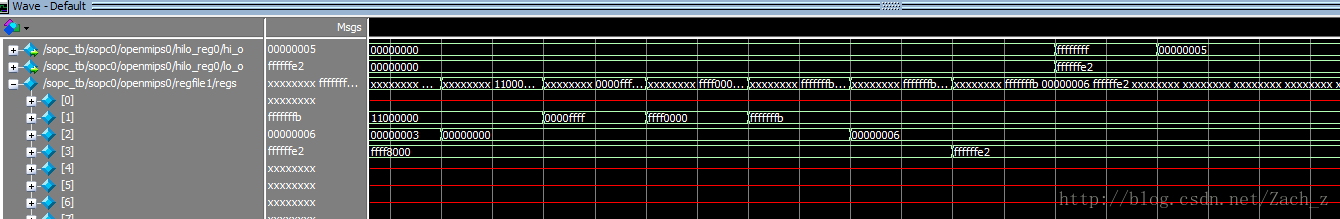

end 測試

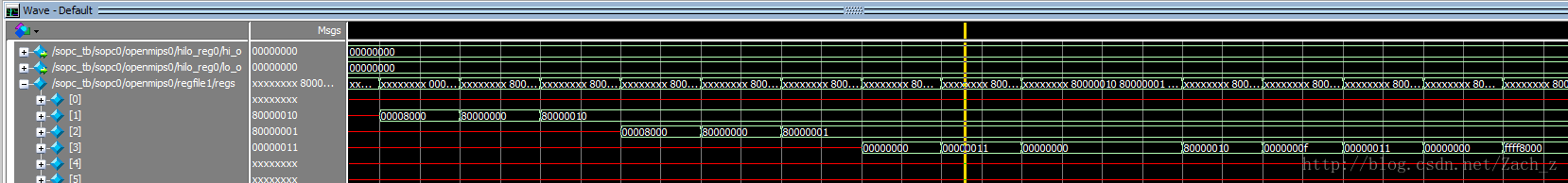

1. 測試add、addi、addiu、addu、sub、subu指令

ori $1,$0,0x8000 # $1 = 0x8000

sll $1,$1,16 # $1 = 0x80000000

ori $1,$1,0x0010 # $1 = 0x80000010 給$1賦值

ori $2,$0,0x8000 # $2 = 0x8000

sll $2,$2,16 # $2 = 0x80000000

ori $2,$2,0x0001 # $2 = 0x80000001 給$2賦值

ori $3,$0,0x0000 # $3 = 0x00000000

addu $3,$2,$1 # $3 = 0x00000011 $1加$2,無符號加法

ori $3,$0,0x0000 # $3 = 0x00000000

add $3,$2,$1 # $2 加 $1,有符號加法,結果溢位,$3保持不變

sub $3,$1,$3 # $3 = 0x80000010 $1減去$3,有符號減法

subu $3,$3,$2 # $3 = 0xF $3減去$2,無符號減法

addi $3,$3,2 # $3 = 0x11 $3 加2,有符號加法

ori $3,$0,0x0000 # $3 = 0x00000000

addiu $3,$3,0x8000 # $3 = 0xffff8000 $3加0xffff8000 無符號加法測試結果:

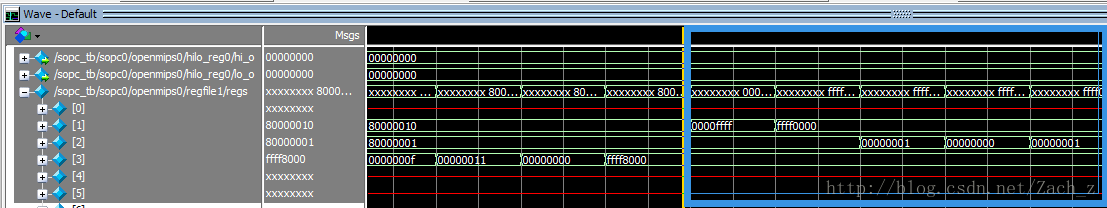

2. 測試slt、sltu、slti、sltiu

or $1,$0,0xffff # $1 = 0xffff

sll $1,$1,16 # $1 = 0xffff0000 給$1賦值

slt $2,$1,$0 # $2 = 1 比較$1與0x0,有符號比較

sltu $2,$1,$0 # $2 = 0 比較$1與0x0,無符號比較

slti $2,$1,0x8000 # $2 = 1 比較$1與0xffff8000,有符號比較

sltiu $2,$1,0x8000 # $2 = 1 比較$1與0xffff8000,無符號比較測試結果:

3. 測試clo和clz指令

lui $1,0x0000 # $1 = 0x00000000 給$1賦值

clo $2,$1 # $2 = 0x00000000 統計$1中“1”之前“0”的個數

clz $2,$1 # $2 = 0x00000020 統計$1中“0”之前“1”的個數

lui $1,0xffff # $1 = 0xffff0000

ori $1,$1,0xffff # $1 = 0xffffffff 給$1賦值

clz $2,$1 # $2 = 0x00000000 統計$1中“1”之前“0”的個數

clo $2,$1 # $2 = 0x00000020 統計$1中“0”之前“1”的個數

lui $1,0xa100 # $1 = 0xa1000000 給$1賦值

clz $2,$1 # $2 = 0x00000000 統計$1中“1”之前“0”的個數

clo $2,$1 # $2 = 0x00000001 統計$1中“0”之前“1”的個數

lui $1,0x1100 # $1 = 0x11000000 給$1賦值

clz $2,$1 # $2 = 0x00000003 統計$1中“1”之前“0”的個數

clo $2,$1 # $2 = 0x00000000 統計$1中“0”之前“1”的個數測試結果:

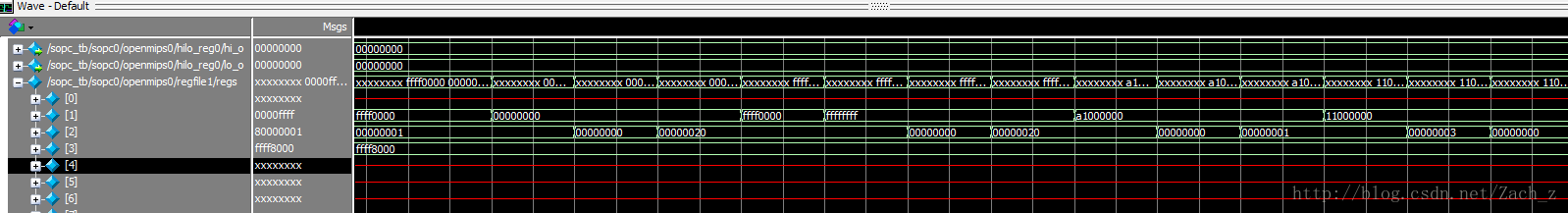

4. 測試mul、mult、multu指令

ori $1,$0,0xffff

sll $1,$1,16

ori $1,$1,0xfffb # $1 = -5 給$1賦值

ori $2,$0,6 # $2 = 6 給$2賦值

mul $3,$1,$2 # $3 = -30 = 0xffffffe2 $1 乘以$2,有符號乘法,結果低32位儲存到$3

mult $1,$2 # hi = 0xffffffff

# lo = 0xffffffe2

# $1 乘以$2,有符號乘法,結果低32位儲存到HI LO

multu $1,$2 # hi = 0x5

# lo = 0xffffffe2

# $1 乘以$2,無符號乘法,結果低32位儲存到HI LO

nop

nop測試結果: