linux記憶體管理-段式和頁式管理

該博文參考國嵌視訊和http://www.cnblogs.com/image-eye/archive/2011/07/13/2105765.html,在此感謝作者。

一、地址型別

實體地址:CPU通過地址匯流排的定址,找到真實的實體記憶體對應地址。

邏輯地址:程式程式碼經過編譯後出現在 彙編程式中地址。

線性地址(虛擬地址):在32位CPU架構下,可以表示4G的地址空間,用16進製表示就是0x00000000---0Xffff ffff

他們之間關係?

二、段式管理、頁式管理

2.1段式管理

2.2.1段式管理(16位CPU)

16位CPU內部擁有20位的地址線,它的定址範圍2^20即1M的記憶體空間,但是16位CPU用於存放地址的暫存器(IP,sp)只有16位,即只能訪問64K記憶體空間。

如何使用16地址暫存器訪問1M記憶體空間??

為了能夠訪問1M的記憶體空間,CPU採用記憶體分段的管理模式,並在CPU內部加入了段暫存器。16位CPU將1M記憶體空間分為若干邏輯段,每個邏輯段的要求如下:

1、 邏輯段的起始地址(段地址)必須是16倍數,即最後4個二進位制必須全部為0

2、 邏輯段的最大容量為64K(why?因為16位CPU存放地址暫存器只有16位)

實體地址的形成方式:

由於段地址必須是16倍數,所以值一般形式為XXXX0H,即前16位二進位制是變化的,後四位是固定的0,鑑於段地址的這種特性,可以只儲存前16位二進位制位來儲存整個段基地址,所以每次使用時要段暫存器乘以16得到實際段地址。

邏輯地址=段基地址:偏移地址

其中:段基地址儲存到段暫存器中,偏移地址儲存另個暫存器中

線性地址= 段基地址*16+偏移地址

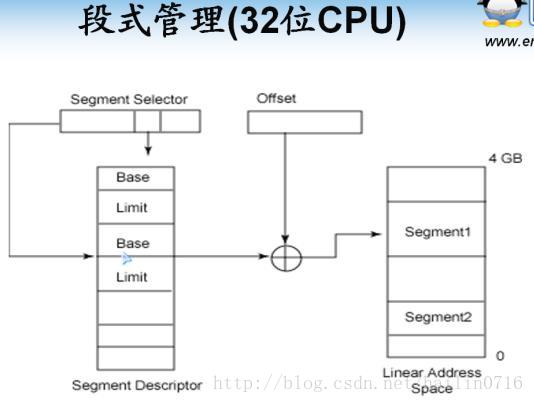

2.2.2段式管理(32位CPU)

在32位CPU兩種工作方式:由真實模式和保護模式組成。

1、 真實模式:記憶體管理與 16位CPU是一致的。

2、 保護模式:(一般X86執行模式)

段基地址長達32位,每個段的最大容量可達4G,段暫存器的值時段地址的“選擇器”(selecor),用該“選擇器”從記憶體中得到一個32位的段地址,儲存單元的

實體地址=該段基地址(Base)+段內偏移地址(offset)

2.2頁式管理(分頁管理)

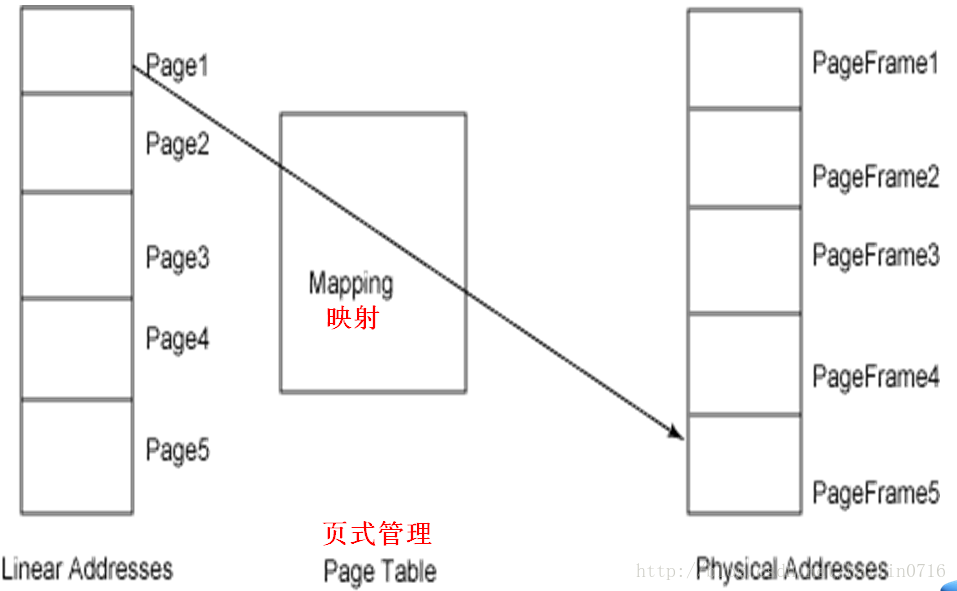

概念

1、 線性地址頁:從管理和效率的角度出發,線性地址被分為固定長度的組,稱為頁(page)。例如32位機器,線性地址最大可為4G,如果用4KB為頁容量,這樣將線性地址劃分為2^20個頁。

2、 物理頁:另一類“頁”,稱為“物理頁”,或者是“頁框、頁幀”。分頁單元把所有的實體記憶體也劃分為固定長度的管理單位,它的長度一般與線性地址頁是相同。

如何將兩者之間的對映?通過頁式管理實現對映。

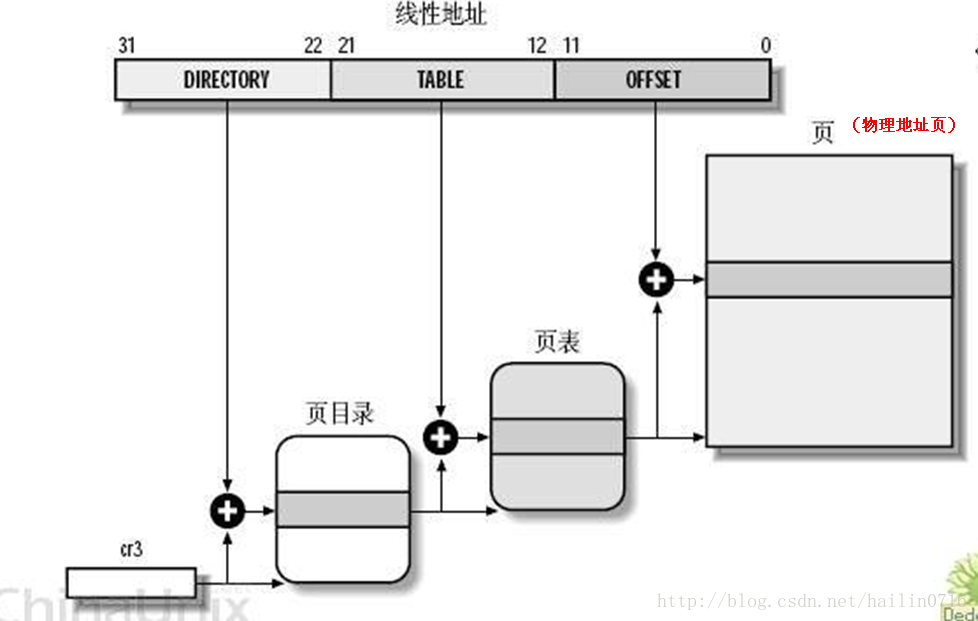

頁式管理具體流程:

說明:

1、 分頁單元中,頁目錄的地址放在CPU的CR3暫存器中,是進行地址轉換的起始點。

2、 每個程序,都有其獨立的虛擬地址空間,執行一個程序,首先需要將它的頁目錄地址放到CR3暫存器中,將其他程序儲存下來。

3、 每一個32位的線性地址被劃分三部分:頁目錄索引(10位):頁表索引(10位):偏移(12位)

下面是地址轉換的步驟:

第一步:裝入程序的頁目錄地址(作業系統在排程程序時,把這個地址裝入CR3)

第二步:根據線性地址前十位,在頁目錄中,找到對應的索引項 即頁表地址。

第三步:根據線性地址中間十位,在頁表中,找到對應的索引項 即頁的起始地址。

第四步:將頁的起始地址與線性地址最後12位相加,等到實體地址。

1、 這樣的二級模式是否支援定址4G的實體地址空間?為什麼?

支援。因為頁目錄支援定址2^10個頁表,每個頁表支援定址2^10個頁,每個頁由2^12=4Kbyte組成,即2^10* 2^10*2^12=4Gbyte滿足。

2、 由上圖實體地址的頁容量多大?有什麼決定的?

在二級模式下,頁容量由線性地址[bit11:0]決定,頁容量=2^12=4Kbyte。

根據上面的分段管理和分頁管理,得出下圖

該圖源於/www.cnblogs.com/image-eye/archive/2011/07/13/2105765.html部落格

三、linux記憶體管理

Linux核心的設計並沒有全部採用intel所提供的段機制,僅僅是有限度使用了分段機制。這不僅簡化了linux核心的設計,而且為了把linux移植到其他平臺創造了條件,因為很多RISC處理器並不支援段機制。

為什麼是linux核心設計有限度使用分段機制?

因為linux核心中記憶體管理中:所有的段的基地址均為0,即每個段的邏輯地址與線性地址保持一致(即邏輯地址的偏移量值與線性線性的地址值相同),而完成利用了分頁機制。

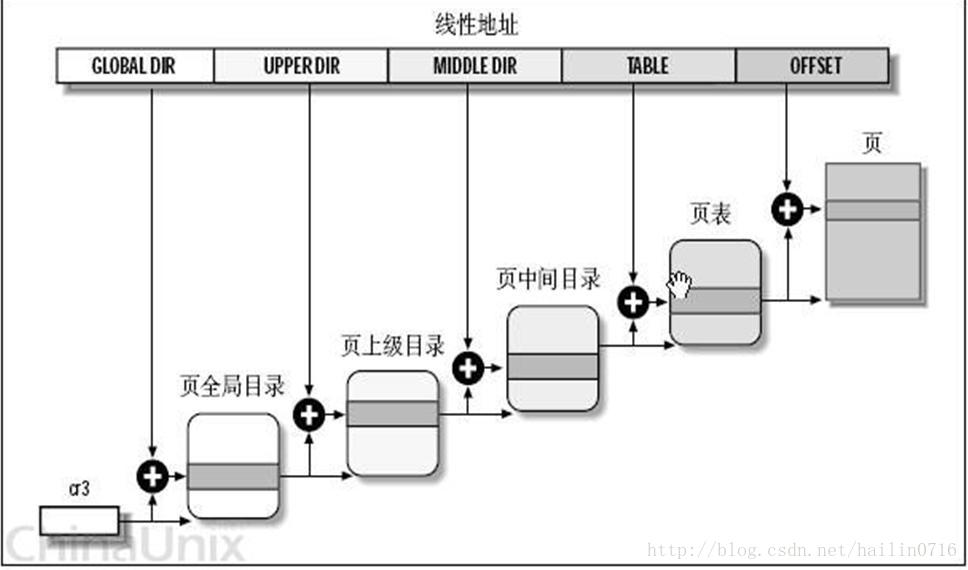

前面介紹的i386的二級頁管理架構,有些CPU使用三級或四級架構。在linux2.6.29核心為每種CPU提供統一介面,四級頁管理架構,來相容二級三級 四級管理架構的CPU。四級架構詳見下面:

其中:

1、頁全域性目錄(page global directory):多級頁表的抽象最高層

2、頁上級目錄(page upper directory):即pud3、頁中間目錄( page middle directory):即pmd 頁表的中間層

4、頁表(page table entry):pte

5、頁:即具體實體地址