【nexys3】【verilog】小設計——拆彈遊戲

設計說明書——拆彈遊戲

一. 設計背景

拆彈遊戲,現有一個定時炸彈,設有一個計時器,如果不能在限定時間內找出唯一的密碼,會發生爆炸,若在規定時間內完成,則相當於炸彈被拆除。

二.使用說明

接通電路,計時器自動開始計時,顯示在數碼管上。利用八個開關輸入二進位制數(從左到右依次為高位到低位),led燈v16亮起則表示輸入密碼偏小,led燈u16亮起則顯示輸入密碼偏大。若輸入正確,則炸彈拆除,顯示“炫酷“的流水燈。若未能在限定時間內完成,則在數碼管上會有相應提示表示”炸彈“已經爆炸。

三.設計說明

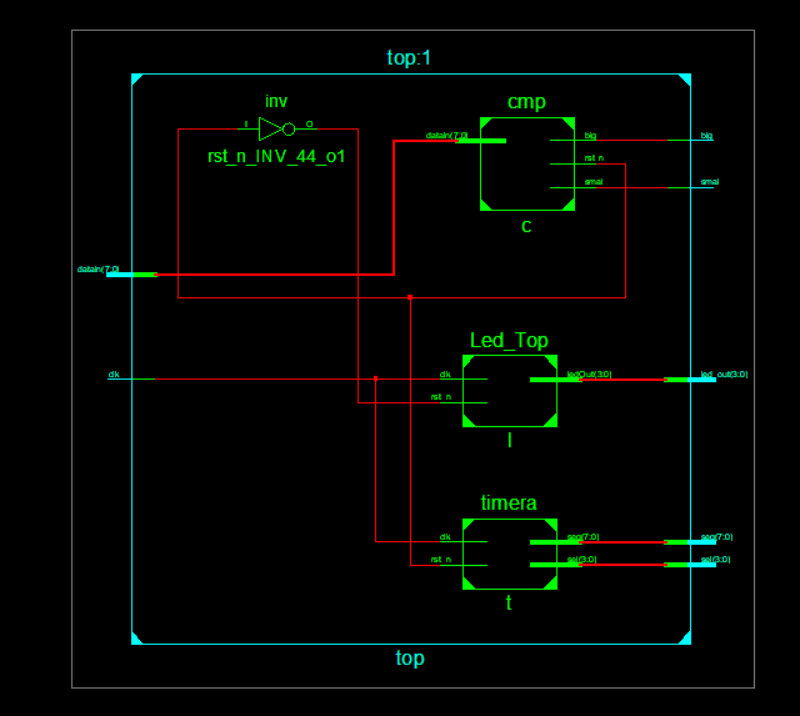

1 . 主要部分:分秒計時狀態機,數碼管顯示模組,密碼比較器,流水燈控制模組

2 . 分秒計時器:

clk頻率50Mhz,及每個時鐘週期20ns,考慮1000_000ns即1ms為一個延遲。

設定一個狀態機,轉換機制如下:計數延遲個數,每經歷1000個延遲,狀態轉換一次每次轉換,秒的個位sec_l增加1,當sec_l=9時,其變為0,十位sec_h加一。當sel_l=9且sec_h=5時,分的各位min_l增加一。同理易得min_h的變化規律。當計時器統計了60分鐘後,所有位歸零從新計時。

3 . 密碼比較器:不涉及時序,僅由邏輯電路構成。將輸入資料(一個8位無符號數)與內建密碼比較,若後者較大,則輸出相應訊號,表示輸入密碼變大,反之則輸出相應訊號,表明輸入偏小。如果恰好為密碼,則炸彈被拆除,則將rst_n置為0,控制數碼管清零,以及顯示流水燈表示慶祝。

4 . 數碼管顯示模組:利用四位從左到右分別顯示計時的分十位,分個位,秒十位,秒個位。利用視覺留影原理,動態掃描四個數碼管,時間每個顯示時間為一個延遲,即1ms,小於人眼暫留時間20ms,經測試顯示穩定。

5 . 流水燈,使用了T11,M11,R11,N11四個led作為輸出,具體輸出樣式參見程式碼。

四.程式碼

module top( input clk, input [7:0] datain, output big, output smal, output [7:0] seg, output [3:0] sel, output [3:0] led_out ); wire rst_n; cmp c(datain,big,smal,rst_n); timera t(rst_n,clk,seg,sel); Led_Top l(clk,~rst_n,led_out); endmodule

module cmp(

input [7:0]datain,

output big,

output smal,

output rst_n

);

integer key=8'b10101010;

assign smal=(datain<key);

assign big=(datain>key);

assign rst_n=~(datain==key);

endmodule

`define T1MS 16'd49_999

`define FLASH_FREQUENCY 14'd500

module Led_Top

(

input clk,rst_n,

output[3:0] ledOut

);

wire[3:0] isStart;

wire[55:0] SetMSTimes;

wire[3:0] isDone;

Led_Control Led_Control

(

.clk(clk),

.rst_n(rst_n),

.isDone(isDone),

.isStart(isStart),

.SetMSTimes(SetMSTimes)

);

Led_Driver Led_Driver[3:0]

(

.clk(clk),

.rst_n(rst_n),

.StartSig(isStart),

.setMSTimes(SetMSTimes),

.DoneSig(isDone),

.ledOut(ledOut)

);

endmodule

module Led_Control

(

input clk,rst_n,

input[3:0] isDone,

output[3:0] isStart,

output[55:0] SetMSTimes

);

reg[3:0] i,j,k;

reg[3:0] regStart;

reg[13:0] regSetMSTimes[3:0];

[email protected](posedge clk,negedge rst_n)

if(!rst_n) //³õʼ»¯

begin

i<=4'd0;

j<=4'd0;

k<=4'd0;

regStart<=4'b0000;

regSetMSTimes[0]<=14'd0;

regSetMSTimes[1]<=14'd0;

regSetMSTimes[2]<=14'd0;

regSetMSTimes[3]<=14'd0;

end

else

case(i)

0:SerialLight(`FLASH_FREQUENCY,`FLASH_FREQUENCY,`FLASH_FREQUENCY,`FLASH_FREQUENCY);

1:PipeLineLight(`FLASH_FREQUENCY,`FLASH_FREQUENCY,`FLASH_FREQUENCY,`FLASH_FREQUENCY);

2:ParallelPipeLineLight(`FLASH_FREQUENCY,`FLASH_FREQUENCY,`FLASH_FREQUENCY,`FLASH_FREQUENCY);

3:i<=4'd0; //¿ØÖÆÑ»·

endcase

assign isStart=regStart;

assign SetMSTimes={regSetMSTimes[3],regSetMSTimes[2],regSetMSTimes[1],regSetMSTimes[0]};

task SerialLight

(

input[13:0] serialSetMSTimes0,serialSetMSTimes1,

serialSetMSTimes2,serialSetMSTimes3

);

case(j)

0:

begin

regSetMSTimes[0]<=serialSetMSTimes0;

regSetMSTimes[1]<=serialSetMSTimes1;

regSetMSTimes[2]<=serialSetMSTimes2;

regSetMSTimes[3]<=serialSetMSTimes3;

regStart[0]<=1'b1;

j<=j+1'b1;

end

1:

if(isDone[0])

begin

regStart[0]<=1'b0;

regStart[1]<=regStart[0];

j<=j+1'b1;

end

2:

if(isDone[1])

begin

regStart[1]<=1'b0;

regStart[2]<=regStart[1];

j<=j+1'b1;

end

3:

if(isDone[2])

begin

regStart[2]<=1'b0;

regStart[3]<=regStart[2];

j<=j+1'b1;

end

4:

if(isDone[3])

begin

regStart[3]<=1'b0;

k<=k+1'b1;

if(k==4'd3)

begin

k<=4'd0;

j<=j+1'b1;

end

else

begin

regStart[0]<=regStart[3];

j<=4'd1;

end

end

5:

begin

j<=4'd0;

i<=i+1'b1;

end

endcase

endtask

task PipeLineLight

(

input[13:0] PipeLineSetMSTimes0,PipeLineSetMSTimes1,

PipeLineSetMSTimes2,PipeLineSetMSTimes3

);

case(j)

0:

begin

regSetMSTimes[0]<=PipeLineSetMSTimes0;

regSetMSTimes[1]<=PipeLineSetMSTimes1;

regSetMSTimes[2]<=PipeLineSetMSTimes2;

regSetMSTimes[3]<=PipeLineSetMSTimes3;

regStart[0]<=1'b1;

j<=j+1'b1;

end

1:

if(isDone[0])

begin

regStart[0]<=1'b1;

regStart[1]<=regStart[0];

regStart[2]<=regStart[1];

regStart[3]<=regStart[2];

k<=k+1'b1;

if(k==4'd2)

begin

k<=4'd0;

j<=j+1'b1;

end

else

j<=j;

end

2:

if(isDone[3])

begin

regStart[0]<=1'b0;

regStart[1]<=regStart[0];

regStart[2]<=regStart[1];

regStart[3]<=regStart[2];

k<=k+1'b1;

if(k==4'd3)

begin

k<=4'd0;

j<=j+1'b1;

end

else

j<=j;

end

3:

begin

j<=4'd0;

i<=i+1'b1;

end

endcase

endtask

task ParallelPipeLineLight

(

input[13:0] PipeLineSetMSTimes0,PipeLineSetMSTimes1,

PipeLineSetMSTimes2,PipeLineSetMSTimes3

);

case(j)

0:

begin

regSetMSTimes[0]<=PipeLineSetMSTimes0;

regSetMSTimes[1]<=PipeLineSetMSTimes1;

regSetMSTimes[2]<=PipeLineSetMSTimes2;

regSetMSTimes[3]<=PipeLineSetMSTimes3;

regStart[0]<=1'b1;

regStart[2]<=1'b1;

j<=j+1'b1;

end

1:

if(isDone[0])

begin

regStart[0]<=1'b1;

regStart[1]<=regStart[0];

regStart[2]<=1'b1;

regStart[3]<=regStart[2];

k<=k+1'b1;

if(k==4'd0)

begin

k<=4'd0;

j<=j+1'b1;

end

else

j<=j;

end

2:

if(isDone[1])

begin

regStart[0]<=1'b0;

regStart[1]<=regStart[0];

regStart[2]<=1'b0;

regStart[3]<=regStart[2];

k<=k+1'b1;

if(k==4'd1)

begin

k<=4'd0;

j<=j+1'b1;

end

else

j<=j;

end

3:

begin

j<=4'd0;

i<=i+1'b1;

end

endcase

endtask

endmodule

module Led_Driver

(

input clk,rst_n,

input StartSig,

input[55:0] setMSTimes,

output DoneSig,

output ledOut

);

wire[13:0] halrSetMSTimes;

wire timerOut;

Led_Driver_Control Led_Driver_Control

(

.clk(clk),

.rst_n(rst_n),

.StartSig(StartSig),

.setMSTimes(setMSTimes),

.timerOut(timerOut),

.DoneSig(DoneSig),

.halrSetMSTimes(halrSetMSTimes)

);

//ÏÈÇó³öÖظ´ÊµÀýµÄ×ÜλÊý£¬È»ºó°´Ã¿¸öʵÀý¶ÔӦλ´ÓµÍµ½¸ß½Ø¶Ï£¬Ã»ÓиßλµÄ¾ÍÊÇÖظ´

Timer Timer //ÿ¸ösetMSTimesÓÐ14룬4¸öTimerÓÐ14*4=56λsetMSTimes£¬

( //Ôò¸øsetMSTimes¸³ÖµÎª56룬setMSTimes»á°´¶ÔӦλ½Ø¶Ï£¬

.clk(clk), //setMSTimes[0]¶ÔÓ¦[13:0]룬setMSTimes[1]¶ÔÓ¦[27:14]λ

.rst_n(rst_n), //setMSTimes[2]¶ÔÓ¦[41:28]룬setMSTimes[3]¶ÔÓ¦[55:42]λ

.StartSig(StartSig),

.setMSTimes(halrSetMSTimes),

.timerOut(timerOut)

);

Led_Interface Led_Interface

(

.clk(clk),

.rst_n(rst_n),

.StartSig(StartSig),

.timerIn(timerOut),

.ledOut(ledOut)

);

endmodule

module Led_Driver_Control

(

input clk,rst_n,

input StartSig,

input[13:0] setMSTimes,

input timerOut,

output DoneSig,

output[13:0] halrSetMSTimes

);

reg countTimerOut;

[email protected](posedge clk,negedge rst_n) //¶ÔʱÖÓ¼ÆÊý£¬ÅжÏÇ°Ò»¸öµÆµÄÁÁÃð

if(!rst_n)

countTimerOut<=1'b0;

else if(StartSig)

begin

if(timerOut && (countTimerOut==1'b1) )

countTimerOut<=1'b0;

else if(timerOut)

countTimerOut<=countTimerOut+1'b1;

end

else

countTimerOut<=1'b0;

assign DoneSig=(StartSig && timerOut && (countTimerOut==1'b1) )?1'b1:1'b0;

assign halrSetMSTimes=setMSTimes>>1;

endmodule

module Timer

(

input clk,rst_n,

input[13:0] setMSTimes,

input StartSig,

output timerOut

);

wire MSOut;

MSTimer MSTimer

(

.clk(clk),

.rst_n(rst_n),

.StartSig(StartSig),

.MSOut(MSOut)

);

NMSTimer NMSTimer

(

.clk(clk),

.rst_n(rst_n),

.setMSTimes(setMSTimes),

.StartSig(StartSig),

.MSIn(MSOut),

.NMSOut(timerOut)

);

endmodule

module MSTimer

(

input clk,rst_n,

input StartSig,

output MSOut

);

reg[15:0] countMS;

[email protected](posedge clk,negedge rst_n)

if(!rst_n)

countMS<=16'd0;

else if(StartSig)

begin

if(countMS == `T1MS)

countMS<=16'd0;

else

countMS<=countMS+1'b1;

end

else

countMS<=16'd0;

assign MSOut=(StartSig && (countMS == `T1MS) )?1'b1:1'b0;

endmodule

module NMSTimer

(

input clk,rst_n,

input MSIn,

input StartSig,

input[13:0] setMSTimes,

output NMSOut

);

reg[13:0] countNMS;

[email protected](posedge clk,negedge rst_n)

if(!rst_n)

countNMS<=14'd0;

else if(StartSig)

begin

if(MSIn && (countNMS==(setMSTimes-1'd1) ) )

countNMS<=14'd0;

else if(MSIn)

countNMS<=countNMS+1'b1;

end

else

countNMS<=14'd0;

assign NMSOut=(StartSig && MSIn && (countNMS==(setMSTimes-1'd1) ) )?1'b1:1'b0;

endmodule

module Led_Interface

(

input clk,rst_n,

input StartSig,

input timerIn,

output ledOut

);

reg regLedOut;

[email protected](posedge clk,negedge rst_n)

if(!rst_n)

regLedOut<=1'b0;

else if(StartSig)

begin

if(timerIn)

regLedOut<=~regLedOut;

end

else

regLedOut<=1'b0;

assign ledOut=regLedOut;

endmodule

// synopsys translate_off

`timescale 1 ns / 1 ps

// synopsys translate_on

module display(

rst_n,

clk,

min_h,

min_l,

sec_h,

sec_l,

display_flag,

seg,

sel

);

input rst_n; // 全域性復位,低電平有效

input clk; // 全域性時鐘,50MHz

input [2:0] min_h; // 分的十位數

input [3:0] min_l; // 分的個位數

input [2:0] sec_h; // 秒的十位數

input [3:0] sec_l; // 秒的個位數

input display_flag; // 數碼管動態顯示標誌位

output reg [7:0] seg; // 編碼後的數碼管輸出

output reg [3:0] sel; // 數碼管的位選

function [7:0] seg_data;

input [3:0] din; // 待編碼資料

input dp; // 決定數碼管點號是否點亮,1為點亮

begin

case(din)

4'd0 : seg_data = {dp,7'b1000000};

4'd1 : seg_data = {dp,7'b1111001};

4'd2 : seg_data = {dp,7'b0100100};

4'd3 : seg_data = {dp,7'b0110000};

4'd4 : seg_data = {dp,7'b0011001};

4'd5 : seg_data = {dp,7'b0010010};

4'd6 : seg_data = {dp,7'b0000010};

4'd7 : seg_data = {dp,7'b1111000};

4'd8 : seg_data = {dp,7'b0000000};

4'd9 : seg_data = {dp,7'b0010000};

endcase

end

endfunction

wire flag;

assign flag=(min_l>=3'b010);

reg [1:0] cnt; // 由於只有四個數碼管,故只需兩位

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

cnt <= (0);

else if(display_flag == 1'b1)

cnt <= cnt + 1'b1;

else

cnt <= cnt;

end

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

seg <= (0);

sel <= (0);

end

else if(flag==1'b1)

begin

case(cnt)

2'b00 : // 顯示秒個位數

begin

seg <= {1'b1,7'b0111111};

sel <= 4'b0111;

end

2'b01 : // 顯示秒十位數

begin

seg <= {1'b1,7'b1000000};

sel <= 4'b1011;

end

2'b10 : // 顯示分個位數

begin

seg <= {1'b1,7'b0001000};

sel <= 4'b1101;

end

2'b11 : // 顯示分十位數

begin

seg <= {1'b1,7'b0000011};

sel <= 4'b1110;

end

endcase

end

else

begin

case(cnt)

2'b00 : // 顯示秒個位數

begin

seg <= seg_data(sec_l,1'b1);

sel <= 4'b0111;

end

2'b01 : // 顯示秒十位數

begin

seg <= seg_data({1'b0,sec_h},1'b1);

sel <= 4'b1011;

end

2'b10 : // 顯示分個位數

begin

seg <= seg_data(min_l,1'b0);

sel <= 4'b1101;

end

2'b11 : // 顯示分十位數

begin

seg <= seg_data({1'b0,min_h},1'b1);

sel <= 4'b1110;

end

endcase

end

end

endmodule

// synopsys translate_off

`timescale 1 ns / 1 ps

// synopsys translate_on

module time_counter(

rst_n,

clk,

min_h,

min_l,

sec_h,

sec_l,

display_flag

);

parameter CLK_CYCLE = 20; // 時鐘週期,單位ns

parameter T0 = 1000_000; // 1ms延時

parameter T0_VAL = T0/CLK_CYCLE-1; // 1ms延時

input rst_n; // 全域性復位,低電平有效

input clk; // 全域性時鐘,50MHz

output reg [2:0] min_h; // 分的十位數

output reg [3:0] min_l; // 分的個位數

output reg [2:0] sec_h; // 秒的十位數

output reg [3:0] sec_l; // 秒的個位數

output display_flag; // 數碼管動態掃描標誌位

reg [15:0] cnt;

[email protected](posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

cnt <= (0);

else if(cnt < T0_VAL)

cnt <= cnt + 1'b1;

else

cnt <= (0);

end

assign delay_1ms = (cnt == T0_VAL); // 1ms延時完成標誌位

assign display_flag = delay_1ms; // 數碼管動態掃描標誌位

reg [9:0] mse;

[email protected](posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

mse <= (0);

else

begin

if(delay_1ms == 1'b1)

begin

if(mse < 10'd999)

mse <= mse + 1'b1;

else

mse <= (0);

end

end

end

wire sec_l_flag = ((mse == 10'd999) && (delay_1ms == 1'b1)); // 1s延時完成標誌位

// 秒個位數計數

[email protected](posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

sec_l <= 0;

else

begin

if(sec_l_flag == 1'b1)

begin

if(sec_l < 4'd9)

sec_l <= sec_l + 1'b1;

else

sec_l <= 0;

end

end

end

wire sec_h_flag = ((sec_l == 4'd9) && (sec_l_flag == 1'b1)); // 秒個位數進位標誌位

// 秒十位數計數

[email protected](posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

sec_h <= 0;

else

begin

if(sec_h_flag == 1'b1)

begin

if(sec_h < 3'd5)

sec_h <= sec_h + 1'b1;

else

sec_h <= 0;

end

end

end

wire min_l_flag = ((sec_h == 3'd5) && (sec_h_flag == 1'b1)); // 秒十位數進位標誌位

// 分個位數計數

[email protected](posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

min_l <= 0;

else

begin

if(min_l_flag == 1'b1)

begin

if(min_l < 4'd9)

min_l <= min_l + 1'b1;

else

min_l <= 0;

end

end

end

wire min_h_flag = ((min_l == 4'd9) && (min_l_flag == 1'b1)); // 分個位數進位標誌位

// 分十位數計數

[email protected](posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

min_h <= 0;

else

begin

if(min_h_flag == 1'b1)

begin

if(min_h < 3'd5)

min_h <= min_h + 1'b1;

else

min_h <= 0;

end

end

end

endmodule

五。總結

本設計中主體部分是一個分秒計時器的狀態機,運用了分頻,數碼管的動態掃描等原理。靈活使用了數碼管,開關,led等裝置實現了計時器,流水燈,顯示等,從而完成了一個具有一定可玩性的小遊戲。

相關推薦

【nexys3】【verilog】小設計——拆彈遊戲

設計說明書——拆彈遊戲 一. 設計背景拆彈遊戲,現有一個定時炸彈,設有一個計時器,如果不能在限定時間內找出唯一的密碼,會發生爆炸,若在規定時間內完成,則相當於炸彈被拆除。二.使用說明接通電路,計時器自動開始計時,顯示在數碼管上。利用八個開關輸入二進位制數(從左

2018中國大學生程序設計競賽 - 網絡選拔賽 1001 - Buy and Resell 【優先隊列維護最小堆+貪心】

input 不出 def pop earch 無限 math 上交 要去 題目傳送門:http://acm.hdu.edu.cn/showproblem.php?pid=6438 Buy and Resell Time Limit: 2000/1000 MS (Java/O

【CPU微架構設計】利用Verilog設計基於飽和計數器和BTB的分支預測器

在基於流水線(pipeline)的微處理器中,分支預測單元(Branch Predictor Unit)是一個重要的功能部件,它負責收集和分析分支/跳轉指令的引數和執行結果,當處理新的分支/跳轉指令時,BPU將根據已有的統計結果和當前分支跳轉指令的引數,預測其執行結果,為流水線取指提供決策依據,進而提高流

【小知識】輕鬆學習MATLAB GUI設計

GUI是“Graphical User Interface”使用者介面介面的縮寫形式。GUI是基於圖形的互動介面,使用選單、按鈕、滑鼠和其它“圖形”與使用者進行資訊互動,而不是採用命令列的形式。 如果你接觸過多種語言的GUI設計,你會發現每種語言的基本程式設計方

【FPGA】Verilog狀態機設計

狀態機是fpga設計中極其重要的一種技巧,掌握狀態機的寫法可以使fpga的開發事半功倍。 下面記錄一下狀態機的基本知識理論。 例項: 三種狀態機實現程式碼: // 一段式狀態機 m

【小家java】 Restful風格的API設計中,怎麼實現批量刪除?

相關閱讀 每篇一句 面試高大上,面試造飛機,工作擰螺絲 因此不能以為自己工作覺得還OK,就覺得自己技術還不錯了 如題,指的是在restful風格的url設計中,怎麼實現批量刪除呢? 這裡指的刪除是真刪除,不是邏輯刪除。如果是邏輯刪除,其實就是upd

pads規則【對某一個元件單獨設計規則】【layout規則對router不適用】【不能拉layout的最小走線規則的線】

對某一個元件單獨設計規則 遇到這樣的一個情況:layout下不管怎麼樣都不能夠對某一個元件單獨設計規則(安全間隔的規則),設定之後再檢查還是會出現錯誤,後來摸索和很久終於找到了一個問題------要設定的安全間隔小於了預設規則的安全間距,這樣的設計pads是不贊同的,但是也

【verilog】單週期MIPS CPU設計

一、 實驗要求設計一個單週期MIPS CPU,依據給定過的指令集,設計核心的控制訊號。依據給定的資料通路和控制單元訊號進行設計。二、 實驗內容1.資料通路設計:mips指令格式只有三種:1)R型別 從暫存器堆中取出兩個運算元,計算結果寫回暫存器堆2)I型別 用

【小家java】String類為什麼要設計成final?不可變有什麼優點?

相關閱讀 原始碼解釋: 先貼一下String類的申明程式碼: public final class String implements java.io.Serializable, Comparable<String>, CharSeque

【BZOJ2424】[HAOI2010]訂貨 最小費用流

需求 bfs pop 容量 family light 成本 pri || 【BZOJ2424】[HAOI2010]訂貨 Description 某公司估計市場在第i個月對某產品的需求量為Ui,已知在第i月該產品的訂貨單價為di,上個月月底未銷完的單位產品要付存貯費用

【Spark深入學習 -12】Spark程序設計與企業級應用案例02

提升 算子 lin count() roi println groupby 工作問題 衍生 ----本節內容------- 1.遺留問題答疑 1.1 典型問題解答 1.2 知識點回顧 2.Spark編程基礎 2.1 Spark開發四部曲 2.2 RDD典型實例

【java設計模式】【行為模式Behavioral Pattern】策略模式Strategy Pattern

java sys algorithm stat 設計模式 log sets ace 行為模式 1 package com.tn.策略模式; 2 3 public class Client { 4 private Strategy strategy; 5

【Unity3D自學記錄】Unity3D之自制小鐘表

new 一個 unity cond 代碼 enter 歐拉角 onu text 今天來寫一個小鐘表,事實上非常easy,就運用到了歐拉角。 首先創建時鐘、分鐘、秒鐘以及4個點(12點、3點、6點、9點)偷懶了~~沒弄那麽多點。 時鐘、分鐘、秒鐘這三個父級的中心一定要註意

【java設計模式】【創建模式Creational Pattern】建造模式Builder Pattern

part main ons rod over res {} retrieve [] 1 package com.tn.pattern; 2 3 public class Client { 4 public static void main(String[

【網易】 【作業】 程序設計入門—C語言 翁愷 第二周

rate span asio tin bar ase read con hab #include<stdio.h> int main() { int a=0,b=0; scanf("%d",&a); if(a>=800)

POJ--3164--Command Network【朱劉算法】最小樹形圖

-- com 刪除 spa col namespace sca while 我們 鏈接:http://poj.org/problem?id=3164 題意:告訴n個點坐標,m條邊表示兩個點之間有路。從1點開始建立一個有向圖最小生成樹。 朱劉算法模板題 ====

【5】標題上的小logo

-- span pan shortcut color font nbsp 圖片 logo <link rel="shortcut icon" href="logo圖片的路徑"> shortcut --- 捷徑,近路 icon --- 圖標【5】標題上的小lo

【最小樹形圖(奇怪的kruskal)】【SCOI 2012】【bzoj 2753】滑雪與時間膠囊

方案 track solved views end cmp ren scoi2012 ext 2753: [SCOI2012]滑雪與時間膠囊 Time Limit: 50 Sec Memory Limit: 128 MB Submit: 1621

【朱-劉算法】【最小樹形圖】hdu6141 I am your Father!

memset 最大 ring scan freopen dir inf strong pri 題意:給你一張帶權有向圖,讓你求最大樹形圖。並在此前提下令n號結點父親的編號最小。 比賽的時候套了個二分,TLE了。 實際上可以給每個邊的權值乘1000,對於n號結點的父邊,加上(

【數學基礎】【歐拉定理模板】【費馬小定理】

基礎 int 復雜度 amp pan -1 log 分治 質數 費馬小定理:當p是一個質數時,且a和p互質,有ap-1=1(mod p) (歐拉定理的一種特殊情況) 歐拉定理:如果a和n互質,那麽aφ(n)=1(mod n) 對於任意a,b,n就有 ab=