【verilog】單週期MIPS CPU設計

一、 實驗要求

設計一個單週期MIPS CPU,依據給定過的指令集,設計核心的控制訊號。依據給定的資料通路和控制單元訊號進行設計。

二、 實驗內容

1.資料通路設計:mips指令格式只有三種:

1)R型別 從暫存器堆中取出兩個運算元,計算結果寫回暫存器堆

2)I型別 用一個16位的立即數作為一個源運算元

3)J型別 用一個26位的立即數作為跳轉的目標地址

根據以上三種類型可以設計相應的資料通路。基本原理如下

下面是實現之後的效果

2.相應模組設計

首先明確應該有哪些主要功能模組

邏輯電路:控制單元,選擇器,ALU,符號位擴充套件單元,branch加法器等

時序電路:PC暫存器,指令/資料儲存器,暫存器檔案

對應的主要程式碼如下:

(1)top模組對各部分的例化:

下面是具體的主要模組的實現

(2)控制單元

module controlunit( input [5:0] opcode, input [5:0] funct, //本實驗只考慮add所以暫時用不到這個欄位 output reg mem_write, output reg mem_toreg, output reg branch, output reg alu_src, output reg reg_dst, output reg reg_write, output reg [2:0] alu_op, output reg jump );[email protected](*) case(opcode) 6'b000000: //add begin reg_dst=1; alu_src=0; mem_toreg=0; reg_write=1; mem_write=0; branch=0; alu_op=3'b001; jump=0; end 6'b001000: //addi begin reg_dst=0; alu_src=1; mem_toreg=0; reg_write=1; mem_write=0; branch=0; alu_op=3'b001; jump=0; end 6'b100011: //lw begin reg_dst=0; alu_src=1; mem_toreg=1; reg_write=1; mem_write=0; branch=0; alu_op=3'b001; jump=0; end 6'b101011: //sw begin reg_dst=0; alu_src=1; mem_toreg=0; reg_write=0; mem_write=1; branch=0; alu_op=2'b001; jump=0; end 6'b000010: //jump begin reg_dst=1; alu_src=0; mem_toreg=0; reg_write=0; mem_write=0; branch=1; alu_op=2'b001; jump=1; end 6'b000111: //bgtz begin reg_dst=1; alu_src=0; mem_toreg=0; reg_write=0; mem_write=0; branch=1; alu_op=2'b001; jump=0; end default: begin reg_dst=1; alu_src=0; mem_toreg=0; reg_write=1; mem_write=0; branch=0; alu_op=2'b10; end endcase endmodule

(3)符號位擴充套件單元

module signextension(num_in,num_out);

input wire[15:0] num_in;

output reg[31:0] num_out;

initial begin

num_out = 0;

end

always @(num_in) begin

num_out<= {{16{num_in[15]}},num_in[15:0]};

end

endmodule(4)branch加法器模組

這裡不進行左移操作,與至指令暫存器的設定相關,本實驗中指令集暫存器每次讀取32位資料,所以不需要像8位那樣進行左移。

(5)pc自增模組

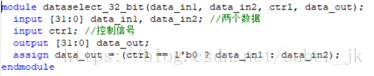

(6)選擇器

這裡是32位的,還有5位的型號,原理一致較為簡單,此不贅述

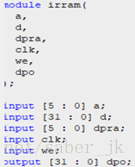

(7)列一下關於兩個ram的介面

(8)ALU,regfile參見前面幾次實驗,這裡不作分析

三、 實驗驗證

1.編寫coe檔案

根據實驗的要求以及個人設計的情況,測試程式碼如下:

(主要是因為pc暫存器指向的地址是32位而不是8位,所以做了修改,無關演算法)

MEMORY_INITIALIZATION_RADIX=16;

MEMORY_INITIALIZATION_VECTOR=

20080000,

200d0014,

8dad0000,

200b0015,

8d6b0000,

200c0015,

8d8c0001,

ad0b0000,

ad0c0001,

21a9fffe,

8d0b0000,

8d0c0001,

016c5020,

ad0a0002,

21080001,

2129ffff,

1d20fff9,

08000011;測試資料:

MEMORY_INITIALIZATION_RADIX=10;

MEMORY_INITIALIZATION_VECTOR=

0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,20,3,3;2.模擬測試

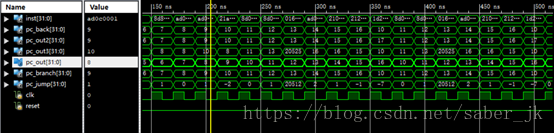

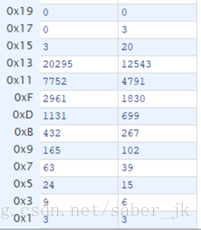

這裡主要是對pc的跳轉進行分析,發現跳轉無誤,我們進入到ram裡觀察執行的情況,下面是dataram:

正好儲存了斐波那契數列的前二十個數,符合要求。

四、 分析和總結

本實驗實現了一個單週期mipscpu,實現了addi、add、lw、sw、bgtz、j六條指令。

實驗的關鍵在於弄清楚cpu以及每條指令的資料通路,還有相應的控制訊號的具體賦值。

在具體實現的時候,最為重要的的是確保指令的跳轉正確,在此基礎上對各個指令的執行debug就輕而易舉。

需要注意的是,在例項化的時候各個對應的介面較為繁雜,應當注意不要出錯,命名簡單易懂。

相關推薦

【verilog】單週期MIPS CPU設計

一、 實驗要求設計一個單週期MIPS CPU,依據給定過的指令集,設計核心的控制訊號。依據給定的資料通路和控制單元訊號進行設計。二、 實驗內容1.資料通路設計:mips指令格式只有三種:1)R型別 從暫存器堆中取出兩個運算元,計算結果寫回暫存器堆2)I型別 用

Verilog實現單週期CPU(部分MIPS指令集的指令)

這學期比較忙,很久沒發部落格了,先附上原始碼,等過完期末再補全博文 原始碼連結:https://github.com/AlexZhang267/Single-Cycle-CPU 注:我是在編輯器中寫的,用Icarus Verilog編譯執行的,沒用vivad

【廣州網站建設公司】單頁網站如何設計?技巧在這裡

在眾多的網站中,也有著很多的單頁面網站,為什麼要做這些單頁網站呢?原因就是單頁網站導航方式簡單,使用者不易迷路,只需上下滾動。單頁網站內容更專注,資訊傳遞更清晰,更有針對性。單頁網站幾乎可以在全平臺裝置上流暢瀏覽,滾動和滑動瀏覽替代了點選。那麼,單頁面網站應該如何設計?廣東鋒火廣州網站建設公司告訴你!

【設計模式】【二】單例模式的七種寫法

相關文章 面試的時候,問到許多年輕的Android開發他所會的設計模式是什麼,基本上都會提到單例模式,但是對單例模式也是一知半解,在Android開發中我們經常會運用單例模式,所以我們還是要更瞭解單例模式才對。 定義:保證一個類僅有一個例項,並提供一個訪

【nexys3】【verilog】小設計——拆彈遊戲

設計說明書——拆彈遊戲 一. 設計背景拆彈遊戲,現有一個定時炸彈,設有一個計時器,如果不能在限定時間內找出唯一的密碼,會發生爆炸,若在規定時間內完成,則相當於炸彈被拆除。二.使用說明接通電路,計時器自動開始計時,顯示在數碼管上。利用八個開關輸入二進位制數(從左

【python】單例設計模式

動作 font 初始 記錄 sta pan dash sicp rgs 1. 定義 目的——讓類創建的對象,在系統中只有唯一的實例。 每一次執行新建對象操作,返回的都是同一個對象。 2. __new__ 方法 使用 classna

P3371 【模板】單源最短路徑

logs alt front 最短路徑 ios num return struct 有向圖 題目描述 如題,給出一個有向圖,請輸出從某一點出發到所有點的最短路徑長度。 輸入輸出格式 輸入格式: 第一行包含三個整數N、M、S,分別表示點的個數、有向邊的個數

【C#】單例模式<機房重構>

機房 .sh 不能 是否 gist 應用 調用方法 單例模式 sender 前言 在機房重構之前。我們學習了設計模式。在這次重構中,我們的任務就是將這些模式,加入到機房的重構中去。如今先來解決一個最簡單的問題——窗口的超生。 假設不加以限

單周期CPU設計

cpu 點贊 ever ref 測試 操作數 將在 寄存器 知識庫 終於有點時間了,恰好多周期的設計也已經完成,其實只想寫寫多周期的,無奈單周期補上才好,哈哈哈~ —————+—————黃金分割線—————+————— 首先要理解什麽叫單周期CPU(與後面多周期CPU對

【轉載】單片機的背後

想象 qpi 直接 依然 大腦 ati 含義 平時 二進制位 我們來思考一個問題,當我們在編程器中把一條指令寫進單片機內部,然後取下單片機,單片機就可以執行這條指令,那麽這條指令一定保存在單片機的某個地方,並且這個地方在單片機掉電後依然可以保持這條指令不會丟失,這是個什麽地

【20171109】Luogu P3371 【模板】單源最短路徑--SPFA

else 輸入 所有 rom scanf node 時空 void edge 題目描述 如題,給出一個有向圖,請輸出從某一點出發到所有點的最短路徑長度。 輸入輸出格式 輸入格式: 第一行包含三個整數N、M、S,分別表示點的個數、有向邊的個數、出發點的編號。 接

python全棧開發【補充】單例模式的四種方式

實現 創建 初始 user 它的 pooled asa args 三種 一、什麽是單例模式 保證一個類只有一個實例,並提供一個訪問它的全局訪問點 二、優點 對唯一實例的受控訪問 單利相當於全局變量,但防止了命名空間被汙染 與單利模式功能相似的概念:全局變量、靜態變量

【總結】遊戲框架與架構設計(Unity為例)

單機 業務 github 事件 概念 lec 集合 架構模式 wid 使用框架開發遊戲 優點:耦合性低,重用性高,部署快,可維護性高,方便管理。提高開發效率,降低開發難度 缺點:增加了系統結構和實現的復雜性,需要額外花費精力維護,不適合小型程序,易影響運行效率 常見

【轉載】關於generate用法的總結【Verilog】

case分支 intro 技術分享 結構 類型 img ora 做了 alt http://www.cnblogs.com/nanoty/archive/2012/11/13/2768933.html Abtract generate語句允許細化時間(Elabora

【轉】程序語言的常見設計錯誤(1) - 片面追求短小

body 缺陷 優化 簡單 code 不知道 返回 技巧 兩種 我經常以自己寫“非常短小”的代碼為豪。有一些人聽了之後很贊賞,然後說他也很喜歡寫短小的代碼,接著就開始說 C 語言其實有很多巧妙的設計,可以讓代碼變得非常短小。然後我才發現,這些人所謂的“短小”跟我所說的“短小

【轉】程序語言的常見設計錯誤(2) - 試圖容納世界

常見錯誤 rip 不一定 list 哪裏 code pre asc cti 之前的一篇文章裏,我談到了程序語言設計的一個常見錯誤傾向:片面追求短小,它導致了一系列的歷史性的設計錯誤。今天我來談一下另外一種錯誤的傾向,這種傾向也導致了很多錯誤,並且繼續在導致錯誤的產生。 今天

【kafka】單節點多broker配置

kafka broker 1.在進入多個broker設置之前,首先啟動ZooKeeper服務器/usr/local/zookeeper/bin/zkServer.sh start2.復制kafka的server.properties文件cd /usr/local/kafka/config/ cp -a

MySQL基礎入門學習【9】無限級分類表設計

父親 連接 參照物 insert gpo 平板電視 生活電器 type mysql 比如: 圖書/小說、文學.../四大名著、戲曲.../... 理論上可以設計很多張表; 但是隨著分類逐步增多,這些表的數目不可能無限擴展; 所以對於無限級分類表一般我們采用如下形式(通過自身

【數論】2016中國大學生程序設計競賽 - 網絡選拔賽 A. A water problem (大整數取模)

判斷 eight ron lin 大學生 con while php bubuko 鏈接:http://acm.hdu.edu.cn/showproblem.php?pid=5832 題意:兩個星球,一個星球一年只有137天,一個星球一年只有73天 輸入N(爆炸後第N

【STL】【HDU5842】2016中國大學生程序設計競賽 - 網絡選拔賽 K. Lweb and String (set)(水~~~)

using 試用 字母 個數 urn 答案 def ret cde 鏈接:http://acm.hdu.edu.cn/showproblem.php?pid=5842 水題,可以用來練習STL中的set 題目大意:給你一串字符串,字符串中的某個字母可以替換為一個數字