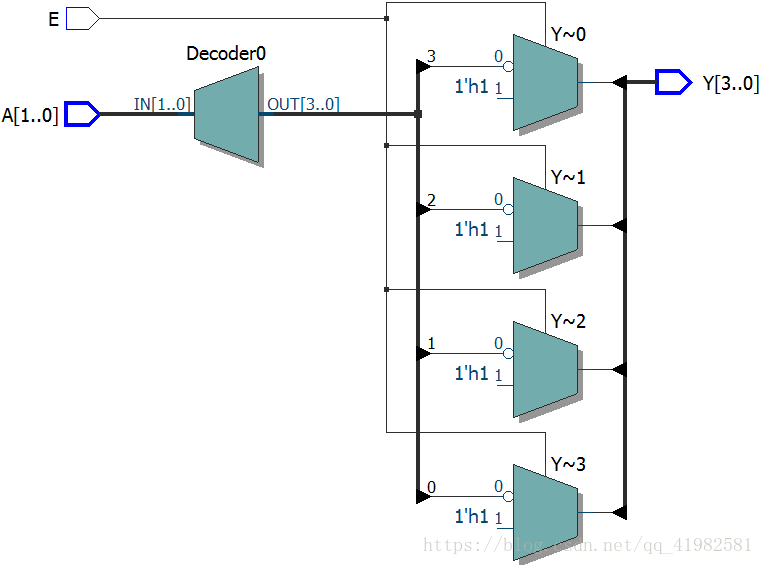

2-4線譯碼器

//2-4線譯碼器

module cy4(input[1:0] A,//輸入埠宣告

input E,//輸入埠宣告

output reg[3:0]Y//輸出埠宣告

);

always @(A,E)

if(E == 1) Y <= 4'b1111;

else

begin

case(A)

2'b00: Y <= 4'b1110;

2'b01: Y <= 4'b1101;

2'b10: Y <= 4'b1011;

2'b11: Y <= 4'b0111;

endcase

end 相關推薦

2-4線譯碼器

//2-4線譯碼器 module cy4(input[1:0] A,//輸入埠宣告 input E,//輸入埠宣告 output reg[3:0]Y//輸出埠宣告 ); always @(A,E)

VHDL實現4線-16線譯碼器

原始碼: library ieee; use ieee.std_logic_1164.all; entity decoder4_16 is port(i: in std_logic_vector(

6.1.2.4 css 選擇器

小寫 css pan col 直接 類選擇器 span 1.3 區分大小寫 1 基本選擇器 1.1 標簽選擇器 直接拿標簽名 如: p{ color: red; } 1.2 id 選擇器

實驗1:拼接 4-16譯碼器

用2片3-8 譯碼器拼接成4-16 譯碼器 模擬驗證電路的正確性 注意觀察輸出訊號的毛刺(競爭冒險) 新的改變 我們對Markdown編輯器進行了一些功能拓展與語法支援,除了標準的Markdown編輯器功能,我們增加了如下幾點新功能,幫助你用它寫部落格: 全

兩片74ls138組成4/16譯碼器-20151030

用兩片74LS138組合成4/16譯碼器如圖真值表對應如下: 輸入 輸出 D0 D1 D2 D3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 Y10 Y11 Y12 Y13 Y14

3線8線譯碼器74HC138&閘電路設計一位二進位制全減器電路

74HC138&閘電路設計一位全減器電路 這個是數電課本上的一個習題 (上課效率基本為0 所以只能下課 自己學點 所有的課程都是 這樣 )剛明白這個題目

Verilog 程式設計實驗(5)-3-8線譯碼器的設計與實現

3-8線譯碼器真值表: Implementation part: module Decoder38(data_in,data_out,enable); input [2:0] dat

Hamming(7,4)編譯碼器

實驗目的 加深理解Hamming(7,4)碼的編碼方法和抗干擾性能。 通過程式設計實現Hamming(7,4)碼的編碼演算法,進一步掌握按位二進位制加法的實現原理。 實驗要求 輸入:長度為4的任

基於proteus的51微控制器模擬例項七十四、4-16譯碼器74HC154應用例項

1、本例通過4-16譯碼器74HC154實現用4個IO口控制16個LED迴圈點亮 2、在keil c51中新建工程ex62,編寫如下程式程式碼,編譯並生成ex62.hex檔案 //4-16線譯

Hadoop-2.4.1學習之edits和fsimage查看器

文件的 順序 rup oev 兼容 require aps block mean 在hadoop中edits和fsimage是兩個至關關鍵的文件。當中edits負責保存自最新檢查點後命名空間的變化。起著日誌的作用,而fsimage則保存了最新的檢查點信息

2.4 利用FTP服務器下載和上傳目錄

logs conn lean 連接 int edi dir ack ftp服務器 利用FTP服務器下載目錄 import os,sys from ftplib import FTP from mimetypes import guess_type nonpassive

第二章 數據通信的基礎知識 計算機網絡筆記 學堂在線 2.4差錯控制

結果 避免 重新發送 通信 網絡筆記 檢驗 冗余 不同 計算機 1 檢錯碼檢錯碼C的函數f最好具備以下特點: 1 不同的數據D對應著不同的C 2 C的位數遠遠小於D且固定 3 函數f計算過程簡單 檢驗和: 計算過程: 1 將數據分為長度固定的數據段 2

Python 基礎 -2.4.3 叠代器

exc 無限 下一個 就是 都是 per iter() python 計算 叠代器 = 循環 叠代器 我們已經知道,可以直接作用於for循環的數據類型有以下幾種: 一類是集合數據類型,如list、tuple、dict、set、str等; 一類是generator,包括生成器

7.2.4 - 並發多線程 守護進程

error ssi 強調 應該 child ren range print 自己的 一 守護進程 主進程創建子進程,然後將該進程設置成守護自己的進程。 關於守護進程需要強調兩點: 其一:守護進程會在主進程代碼執行結束後就終止 其二:守護進程內無法再開啟子進程,否則拋

7.2.4 - 並發多線程 互斥鎖

可能 機制 join() 進程間 是把 == 隊列 完成 div 一 互斥鎖 進程之間數據不共享,但是共享同一套文件系統,所以訪問同一個文件,或同一個打印終端,是沒有問題的,而共享帶來的是競爭,競爭帶來的結果就是錯亂,如下 from multiprocessing

【CPU微架構設計】分布式多端口(4寫2讀)寄存器堆設計

可用 ports 同步 不同 多個 input 負責 相同 集中式 寄存器堆(Register File)是微處理的關鍵部件之一。寄存器堆往往具有多個讀寫端口,其中寫端口往往與多個處理單元相對應。傳統的方法是使用集中式寄存器堆,即一個集中式寄存器堆匹配N個處理單元。隨著

使用Hbase協作器(Coprocessor)同步資料到ElasticSearch(hbase 版本 1.2.0-cdh5.8.0, es 2.4.0 版本)

參考 https://gitee.com/eminem89/Hbase-Observer-ElasticSearch 上面的程式碼,但是由於我的es版本是2.4.0 和作者的版本不對應導致功能無法正常使用,所以特此記錄修改成能參考 程式碼如

[From 2.4]C#編譯器和程序集鏈接器(以及一些它們的命令開關)

數據表 記錄 store gui 執行 類型 全局函數 全局 以及 C#編譯器:(用csc命令來使用C#編譯器) 程序集鏈接器(Assembly Linker):(用al命令來使用C#編譯器) 除了使用C#編譯器,還可以使用”程序集鏈接器“使用程序AL.exe來創建程序。

2-3 Verilog 7 段譯碼器(動態顯示)

使用工具:Xilinx ISE 14.7 通過時間分頻在4位7段數碼管中顯示2個數字,給人眼一個錯覺是同時顯示出兩個數字。實現原理是輪流向各位數碼管送出字形碼和相應的位選訊號,利用數碼管閃爍的餘暉和人眼視覺的暫留作用,使人感覺像各位管同時在顯示,需要用到FPGA上的c

基於VHDL的層次化設計:非同步清零和同步使能4位十六進位制加法計數器和七段顯示譯碼器的元件例化實現

-----------------------------------------------------------------------------------------------方案一--------------------------------------