關於RGB屏除錯的一些知識

1.關於模式:RGB屏顯示資料輸出是分為兩種模式的,一種是DE模式,由DE輸出高低電平控制;另一種是SYNC模式,由hsync與vsync輸出行場同步訊號至RGB屏。該兩種模式由一個MODE腳進行選擇,為0 時選擇SYNC模式,為1時選擇DE模式。

通常選擇DE模式,相容支援的RGB模組較多。

2.關於幀率:通常屏的顯示幀率可以選擇58-60幀,太低眼睛會發現閃屏。太高增加系統能耗,且顯示IC不一定能支援。

幀率還與RGB屏的DCLK有著直接的線性聯絡。

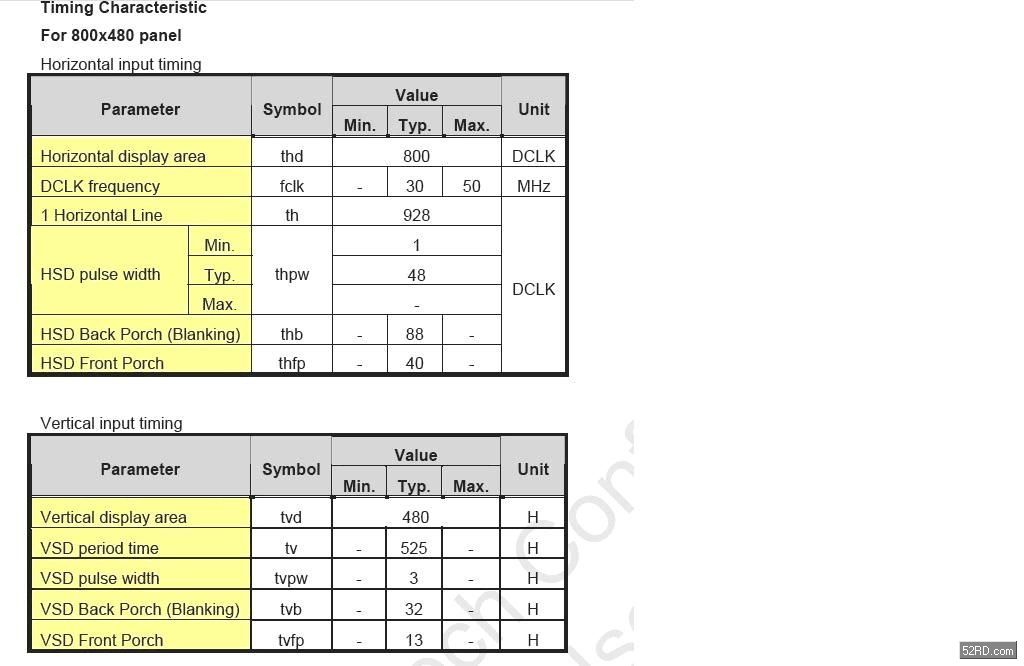

3.關於RGB屏的timing:下面針對800*480解析度的屏進行分析

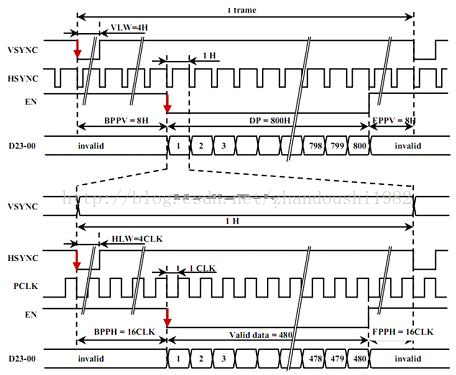

如圖所示,RGB屏的timing由兩部分組成

(1).horizontalinput timing

1HS(行)共928個PCLK,其中有800 個有效顯示PCLK,88個HSDBACK PORCH(回掃用),48個HSDFRONT PORCH(掃描輸出準備用)。

此外,HS與HS之間的間隔稱為HSDpulse width,最小值為1個PCLK。

(2).horizontal input timing(單位均為HS):

1vs(列)共525個HS,其中有480 個有效顯示HS,32個VSDBACK PORCH(回掃用),13個VSDFRONT PORCH(掃描輸出準備用)。

此外,VS與VS之間的間隔稱為VSDpulse width,典型值為3個HS。

4.關於RGB

由上圖可以看出:

A、首先看資料線,當開始傳輸第一個資料時,如果EN為下降沿,即傳輸Validdata 時EN低有效,則其極性為負,否則為正。

B、VSYNC和HSYNC分別代表一幀資料和一行資料的開始,當一幀以下降沿開始時,則其極性為負,否則為正。當一行以下降沿開始時,則其極性為負,否則為正。

需要特別說明的是,DE訊號基本可以看做一個HSD訊號。但相比HSD訊號包括HSDBACK PORCH與HSDFRONT PORCH,DE訊號則只是有效行資料輸出訊號。在本例中,一個有效DE訊號(為低)內,掃描輸出800個PCLK有效顯示資料。

5. 關於PCLK

PCLK的大小可以簡單認為:PCLK= 幀率×VSD×HSD,但須加上行與行的間隔(行脈寬),場與場的間隔(場脈寬)。因此,本例中PCLK須滿足下列條件:

PCLK>= 58(幀率)×(800+88+40+48)×(480+32+13+3)