DSP EMIF 與FPGA 雙口BRAM

為實現DSP與FPGA之間實現交換資料,通常採用DSP的EMIF外部儲存器藉口與FPGA 片內的BRAM,

BRAM 採用雙口BRAM ,一個埠給DSP EMIF介面,另一個埠給 FPGA 片內邏輯。

FPGA 片內邏輯對BRAM 的讀寫在上一文中以實現,本文主要實現DSP 對 BRAM 的讀寫。

DSP 片內EMIF 介面訊號如下圖:

訊號說明:

————————————————共用訊號——————————————————

ECLKIN EMIF外部輸入時鐘

ED[63:0] EMIF 資料匯流排

EA[19:0] ENIF 地址匯流排

BA[1:0] 當EMIF 配置為8位或是16為時,低兩位地址線

BE[7:0] 位元組使能

CE2 CE2空間片選使能 ,低有效

CE3 CE3空間片選使能 ,低有效

CE4 CE4空間片選使能 ,低有效

CE5 CE5空間片選使能 ,低有效

————————————————非同步訊號——————————————————

ARDY 非同步Ready輸入訊號

R/W 非同步讀寫訊號

AOE 非同步輸出使能訊號

AWE 非同步寫選通訊號

————————————————同步訊號——————————————————

ECLKOUT EMIF輸出時鐘

SOE 同步輸出使能

SADS/SRE 當暫存器CEnCFG中的R_ENABLE為1時,該訊號為同步讀使能訊號

當暫存器CEnCFG中的R_ENABLE為0時,該訊號為同步地址選通訊號

SWE 同步寫使能訊號

————————————————保持訊號——————————————————

HOLD 匯流排保持請求訊號

HOLDA 應答請求訊號

BUSREQ 匯流排請求訊號

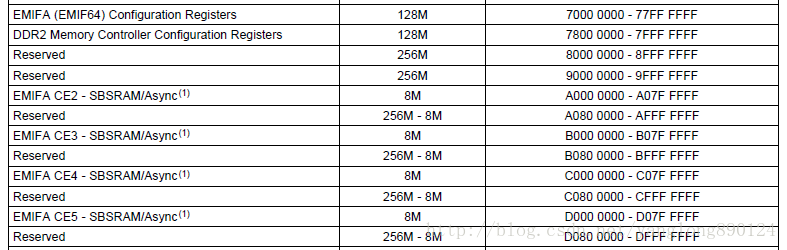

對於TMS320C6455的EMIF 儲存空間對映圖如下:

從上圖可看出,每個儲存空間有8M 的空間,都可以配置為同步和非同步介面

由於這裡FPGA內部的雙口RAM 採用了同步模式,並將BRAM掛接在CE4空間下,所以EMIF 的CE4 配置為同步模式

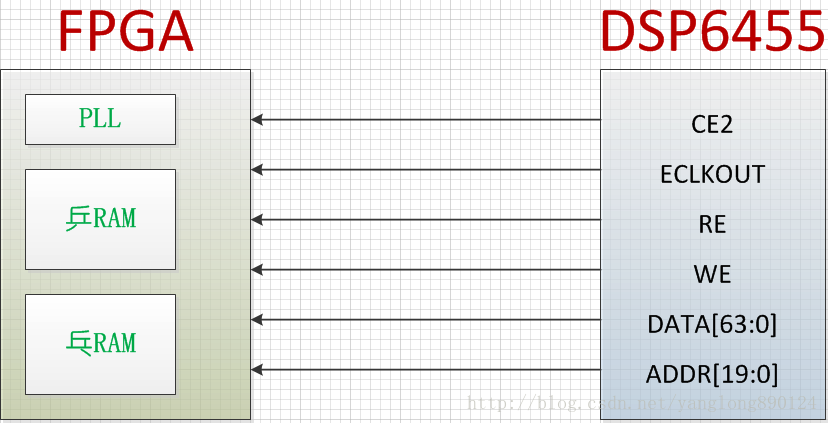

採用同步模式,首先是時鐘,將ECLKOUT 與雙口RAM 的時鐘引腳相連

使能訊號與雙口RAM 的時鐘引腳相連

讀寫訊號與雙口RAM 讀寫相連,地址匯流排,資料匯流排。

由上面的分析,FPGA 與DSP 之間的連線如下圖:

其中,FPGA 對雙口RAM 的讀寫上一篇中一實現,下面實現DSP對RAM 讀寫的實現

DSP 的配置,以實現EMIF 的CE4空間配置為同步模式,由於BRAM 掛接在CE4空間,所以要配置CE4CFG暫存器

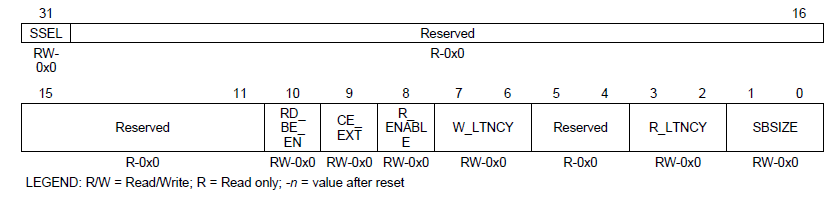

先來看看該暫存器的說明,如下圖:

暫存器說明:

——————————————————————————————————

SSEL 暫存器選擇,1同步儲存器,0非同步儲存器

RD_BE_EN 為1時在同步儲存器讀期間被驅動,為0時,在同步儲存器讀期間一直為高,

這個一般情況下都為0,也就是讀取是每個位元組都有效

CE_EXT 外部同步儲存器片選,為1

R_ENABLE 同步儲存器讀使能模式,為1時選擇ASRE,即同步讀使能訊號,為0時同步地址選通,所以這裡為1

W_LTNCY 為0時,0時鐘週期寫延時

為1時,1時鐘週期寫延時

為2時,2時鐘週期寫延時

為3時,3時鐘週期寫延時,從上一篇文中FPGA 內部雙口RAM 可知寫延時為0,這裡配置為0

R_LTNCY 為0時,0時鐘週期讀延時

為1時,1時鐘週期讀延時

為2時,2時鐘週期讀延時,從上一篇文中FPGA 內部雙口RAM 可知讀延時為2,這裡配置為2

SBSIZE 為0時,資料位寬為8

為1時,資料位寬為16

為2時,資料位寬為32

為3時,資料位寬為64

——————————————————————————————————

如何實現上述暫存器的配置,在DSP下,通常採用CSL(片上支援庫)

使用CSL配置EMIFA模組時,主要的步驟如下:

1. 使能裝置EMIFA模組

2. 配置CEnCFG暫存器

3. 初始化EMIFA模組

4. 開啟EMIFA模組

5. 把2中配置的引數設定到開啟的EMIFA模組中

所須包含的標頭檔案:

#include <csl_emifa.h>

#include <cslr_dev.h>CE4空間首地址的定義:

#define EMIFA_CE4_BASE_ADDR (0xC0000000u)儲存器型別的定義:

#define EMIFA_MEMTYPE_ASYNC 0

#define EMIFA_MEMTYPE_SYNC 1定義EMIF例項控制代碼:

CSL_EmifaHandle hEmifa;使能EMIF:

CSL_FINST(((CSL_DevRegs*)CSL_DEV_REGS)->PERCFG1, DEV_PERCFG1_EMIFACTL, ENABLE);定義同步儲存器引數:

#define CSL_EMIFA_SYNCCFG_RLTNCY_PARAMETER 2//讀延時2週期

#define CSL_EMIFA_SYNCCFG_SBSIZE_PARAMETER 2//32位資料匯流排

#define CSL_EMIFA_SYNCCFG_READEN_PARAMETER 1//同步讀使能

定義CE4CFG暫存器引數巨集:

#define CSL_EMIFA_SYNCCFG_PARAMETER {\

(Uint8)CSL_EMIFA_SYNCCFG_READBYTEEN_DEFAULT, \

(Uint8)CSL_EMIFA_SYNCCFG_CHIPENEXT_DEFAULT, \

(Uint8)CSL_EMIFA_SYNCCFG_READEN_PARAMETER, \

(Uint8)CSL_EMIFA_SYNCCFG_WLTNCY_DEFAULT, \

(Uint8)CSL_EMIFA_SYNCCFG_RLTNCY_PARAMETER, \

(Uint8)CSL_EMIFA_SYNCCFG_SBSIZE_PARAMETER \

}相關變數定義:

CSL_EmifaObj emifaObj;

CSL_Status status;

CSL_EmifaHwSetup hwSetup;

CSL_EmifaHandle hEmifa;

CSL_EmifaMemType syncVal;

CSL_EmifaSync syncMem = CSL_EMIFA_SYNCCFG_PARAMETER;//將上述引數填入儲存器變數

配置CE4CFG暫存器:

syncVal.ssel = EMIFA_MEMTYPE_SYNC;

syncVal.async = NULL;

syncVal.sync = &syncMem;

hwSetup.ceCfg[0] = NULL; //對應CE2

hwSetup.ceCfg[1] = NULL; //對應CE3

hwSetup.ceCfg[2] = &syncVal; //對應CE4

hwSetup.ceCfg[3] = NULL; //對應CE5初始化EMIFA模組:

status = CSL_emifaInit(NULL);

開啟EMIFA模組:

hEmifa = CSL_emifaOpen(&emifaObj,CSL_EMIFA,NULL,&status);

將配置的引數設定到開啟的EMIFA模組中:

status = CSL_emifaHwSetup(hEmifa,&hwSetup);