S01-CH01 FPGA設計Verilog基礎(一)

CH01 FPGA設計Verilog基礎(一)

1.1 FPGA技術背景

大規模積體電路設計製造技術和數字訊號處理技術,近三十年來,各自得到了迅速的發展。這兩個表面上看來沒有什麼關係的技術領域實質上是緊密相關的。因為數字訊號處理系統往往要進行一些複雜的數學運算和資料的處理,並且又有實時響應的要求,它們通常是由高速專用數字邏輯系統或專用數字訊號處理器所構成,電路是相當複雜的。因此只有在高速大規模積體電路設計製造技術進步的基礎上,才有可能實現真正有意義的實時數字訊號處理系統。對實時數字訊號處理系統的要求不斷提高,也推動了高速大規模積體電路設計製造技

術的進步。現代專用積體電路的設計是藉助於電子電路設計自動化(EDA)工具完成的。學習和掌握硬體描述語言(HDL)是使用電子電路設計自動化(EDA)工具的基礎。

筆者建議Verilog,雖然很多學校古董級的老師還在教VHDL.當然VHDL也是要了解的,因為這門古老的語言的歷史遺留問題,現在還有很多VHDL的模組,有的時候我們要拿來主義,所以還有必要了解下的。但是歷史的車輪總是在前進,優勝劣汰。也許不久的將來Verilog也會被C,C++這種高階語言代替。

為了更方面地切入主題,筆者假設,你已經學過微控制器,並且掌握C語言。因為微控制器,和C語言,可以說是當代大學生的一項基本能力。有了這個基礎,再學習其他現代計算機程式設計,演算法,才能達到事半功倍的效果。如果你還不會微控制器和C語言,建議你首先學會微控制器,或者C語言。當然,這只是筆者的建議,不會微控制器,或者C語言,並不代表學不好Verilog語言。

學過微控制器的都知道,我們的程式程式碼是一條指令一條指令來執行的。CPU首先通過匯流排,讀取一條指令,然後解析這條指令,再然後執行這條指令。我們寫的C程式碼總是一條一條地執行。如果我們同時要處理10個子程式,那麼CPU必須一個個子程式來執行。如果有些實時性較高的,如掃描下矩陣鍵盤,VGA刷個屏,都需要中斷來實現。如果刷屏時間比較長,就會影響到你按鍵的靈敏度。另外比如,我們的微控制器在用串列埠接收資料,並且也要傳送資料,同時我們的微控制器要處理外部的IO訊號,如果我們的IO訊號非常快,並且有幾百個訊號,可能同一個時刻觸發,很顯然,如果這些訊號比較快,那麼我們的微控制器,就沒法實現了。

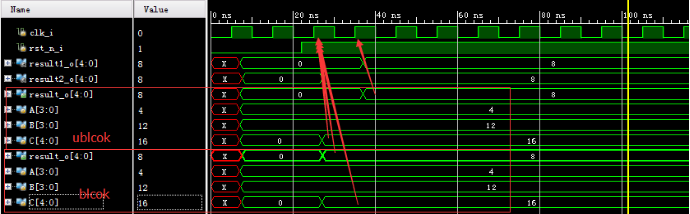

這是筆者簡單舉了兩種情況,那麼如果使用FPGA就可以很方便地解決以上問題。由於FPGA的並行性,不管是掃描鍵盤,還是掃描VGA,都可以把它們做成獨立的模組,時間上沒有衝突,每個模組可以同時執行。

再比如用一個FPGA,就可以同時完成串列埠的收發,以及IO的監控,因為FPGA的程式實際上就是電路,是瞬間就完成了,我們只要用Verilog寫出來相應功能的程式模組,這些模組是同時執行的。

這樣看來FPGA真是太強大了,太完美了。但不要高興地太早,由於FPGA可以在一個時鐘內,完成多條語句的賦值,但是如果賦值必須有個前後順序呢?也就是需要一步步的完成,怎麼辦?如果說並行控制是FPGA的優點,那麼順序控制就是他的不足之處。世界上永遠沒有完美的東西,我們在獲得一種優勢的時候,往往也獲得了一種劣勢。但是,辦法總比問題多。

- 順序控制的第一種辦法——狀態機設計

可以說,我們用Verilog來寫程式,狀態機無處不在。顧名思義,通過設計狀態機,我們可可以控制Verilog讓他該快的時候快,該慢的時候慢,該做什麼的時候就做什麼。這才是我們想要的。狀態機是很不錯的東西,初學者對他望而生畏,而熟悉Verilog語言的人都對其會愛不釋手。

- 順序控制的第二種方法——FPGA中執行CPU

FPGA也可以執行CPU?是的,沒錯,FPGA也可以像微控制器一樣使用,這樣我們就可以用C程式碼來一條條指令來執行了,這不是太強大了?是的,沒錯。關鍵的問題是,我們是可以把一些邏輯控制順序複雜的事情用C程式碼來實現,而實時處理的部分仍然用Verilog來實現。並且那部分Verilog可以被C程式碼控制。Xilinx FPGA目前支援的CPU有Microblaze,ARM9,POWERPC,CortexA9(zynq就Xilinx比較新的一款片子,完美的將CortexA9和FPGA整合到一起,有興趣的可以淘寶搜尋MiZ702)其中Microblaze是一款軟CPU,是軟核。ARM9,CortexA9和POWERPC是硬核。這裡有兩個概念:

1)軟核就是用程式碼就是能現的CPU核,這種核配置靈活,成本較低。但是要佔用FPGA寶貴的資源。

2)硬核就是一塊電路,做到FPGA內部,方便使用,效能更高。比如Xilinx的DDR記憶體控制器,就是一種硬核,其執行速度非常高,我們只要做些配置,就可以方便使用。

兩種核可謂各有所長。

- FPGA還是ASIC

根據具體看情況而定,從我們上面的一些介紹,筆者相信你已經有一定的判斷能力了。筆者的建議是,低速場合,實時性要求的低的地方用ASIC,有些功能用ASIC方便的用ASIC,成本低的用ASIC。排除那些可以不用FPGA地方,那麼剩餘的就要考慮是不是用FPGA來實現更加方便。一般來說,FPGA程式開發相對來說要難度大一些,並且成本要高一些。

講了這麼多的背景知識,我們來看一小段程式碼:

| //C語言 u32sum(a,b) { a=a+1; b=b+1; c=a+b; return c; }

//Verilog always@(posedge clk) begin a = a + 1; b = b + 1; c = a + b; end |

同樣是實現了求和,但是,C程式碼需要N多個(很多)CPU週期才得出結果,而用Verilog一個clk週期就計算出來了。

或許現在你還不知道為什麼。沒關係,下面的內容筆者講解Verilog語言基礎。

1.2 Verilog基礎語法

Verilog和C在外形上有很大相識的地方,有了C基礎背景,Verilog看起來就並不陌生。

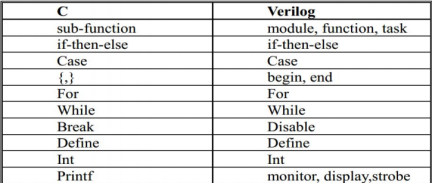

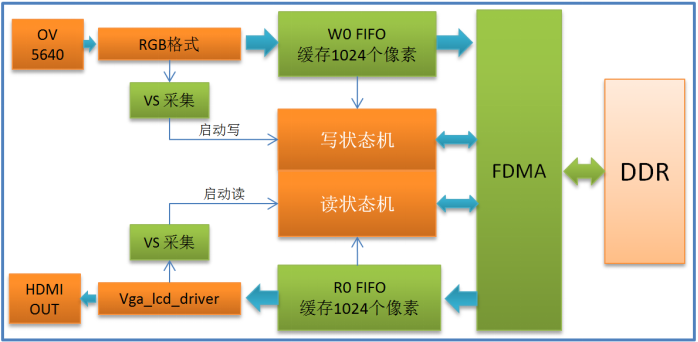

C語言和Verilog的關鍵詞和結構對比:

C語言和Verilog運算子對比:

真是太振奮人心了,一切都是這麼熟悉。學好FPGA已經沒有心理障礙了。

1.3 關鍵字

1.3.1 module

| module() … endmodule |

代表一個模組,我們的程式碼寫在這個兩個關鍵字中間

1.3.2 input output

input關鍵詞,模組的輸入訊號,比如input Clk,Clk是外面關鍵輸入的時鐘訊號;

output關鍵詞,模組的輸出訊號,比如output[3:0]Led; 這個地方正好是一組輸出訊號。其中[3:0]表示0~3共4路訊號。

inout模組輸入輸出雙向訊號。這種型別,我們的例子24LC02中有使用。數匯流排的通訊中,這種訊號被廣泛應用;

wire關鍵詞,線訊號。例如:wire C1_Clk; 其中C1_Clk就是wire型別的訊號;

線訊號,三態型別,我們一般常用的線訊號型別有input,output,inout,wire;

reg關鍵詞,暫存器。和線訊號不同,它可以在always中被賦值,經常用於時序邏輯中。比如reg[3:0]Led;表示了一組暫存器。

1.3.3 always

always@()括號裡面是敏感訊號。這裡的always@(posedge Clk)敏感訊號是posedge Clk含義是在上升沿的時候有效,敏感訊號還可以negedge Clk含義是下降沿的時候有效,這種形式一般時序邏輯都會用到。還可以是*這個一符號,如果是一個*則表示一直是敏感的,一般用於組合邏輯。

1.3.4 assign

assign用來給output,inout以及wire這些型別進行連線。assign相當於一條連線,將表示式右邊的電路直接通過wire(線)連線到左邊,左邊訊號必須是wire型(output和inout屬於wire型)。當右邊變化了左邊立馬變化,方便用來描述簡單的組合邏輯。示例:

| wire a, b, y; assign y = a & b; |

1.3.5 if...else...

這些語句含義上都和高階語言一樣:

| if(...)begin ............ End

if(...)begin ............ end else begin ............ End

if(...)begin ............ end else if(...)begin ............ end

case(...) ............ endcase |

1.3.6 case...endcase

case...endcase作用域用於狀態機的編寫

| case(s) 1:begin ... end 2:begin ... end default:begin ... end endcase |

1.3.7 begin...and

begin..... end作用域範圍,類似於C的大括號。用法舉例:

| always@(posedge clk)begin ............ end |

1.3.8 parameter

parameter定義一個符號a為常數(十進位制180找個常量的定義等效方式):

| parameter a = 180;//十進位制,預設分配長度32bit(編譯器預設) parameter a = 8’d180;//十進位制 parameter a = 8’HB4; //十六進位制 parameter a = 8’b1011_0100; //二進位制 |

1.3.9 include&define

Include 和define都是預處理命令,用於常量闡述的定義

| //-------------------------------- `include file1.v //-------------------------------- `define X = 1; //-------------------------------- `deine Y;

`ifdef Y Z=1; `else Z=0;

`endif //--------------------------------

|

有的時候我們一些公共的巨集引數,我們可以放在一個檔案中,比如這個檔名字為xx.v那麼我們可以`include xx.v就可以包含找個檔案中定義的一些巨集引數。我還是來詳細說明下吧!

話說Verilog 的`include和C語言的include用法是一樣一樣的,要說區別可能就在於那個點吧。

include一般就是包含一個檔案,對於Verilog這個檔案裡的內容無非是一些引數定義,所以這裡再提幾個關鍵字:`ifdef `define `endif(他們都帶個點,呵呵)。

他們聯合起來使用,確實能讓你的程式多樣化,就拿VGA程式說事吧。

首先,你可以新建一個.v檔案(可以直接新建一個TXT,讓後將字尾換成.v)其實這個字尾沒所謂,.v也是可以的,我覺得,寫成.v更能體現出這個檔案的意義。

假設有個lcd_para.v檔案,內容如下:

| // 640 * 480 `ifdef VGA_640_480_60FPS_25MHz `define H_FRONT 11'd16 `define H_SYNC 11'd96 `define H_BACK 11'd48 `define H_DISP 11'd640 `define H_TOTAL 11'd800

`define V_FRONT 11'd10 `define V_SYNC 11'd2 `define V_BACK 11'd33 `define V_DISP 11'd480 `define V_TOTAL 11'd525 `endif // 800 * 600 `ifdef VGA_800_600_72FPS_50MHz `define H_FRONT 11'd56 `define H_SYNC 11'd120 `define H_BACK 11'd64 `define H_DISP 11'd800 `define H_TOTAL 11'd1040

`define V_FRONT 11'd37 `define V_SYNC 11'd6 `define V_BACK 11'd23 `define V_DISP 11'd600 `define V_TOTAL 11'd666 `endif //--------------------------------- `define H_Start (`H_SYNC + `H_BACK) `define H_END (`H_SYNC + `H_BACK + `H_DISP) `define V_Start (`V_SYNC + `V_BACK) `define V_END (`V_SYNC + `V_BACK + `V_DISP) |

這裡為VGA定義了兩種解析度,通過`define VGA_800_600_60MHz或 VGA_640_480_60FPS_25MHz 或`define VGA_800_600_72FPS_50MHz來決定使用哪種解析度。

比如,我的xxx.v檔案想呼叫lcd_para.h,那麼xxx.v我可以寫到:

| `define VGA_800_600_60MHz //這句要放在"lcd_para.h"的上面,不然編譯不通過 `include "lcd_para.h" |

那麼xxx.v檔案中就可以用lcd_para.v中的引數了,且對應是VGA_800_600_60MHz下的引數。

其次`include "lcd_para.v" 這個路徑也有一點講究,xxx.v作為引用lcd_para.v的檔案它和lcd_para.v在同一資料夾下才能怎麼寫,就是相對路徑一說了。也就是以xxx.v為當前路徑去引索lcd_para.v檔案的位子。所以如果他們不再一個資料夾那麼請寫出更詳細(正確)的路徑。順便說一句,lcd_para.v添不新增到工程是無所謂的,只要路徑

對了即可,當然我還是建議新增到工程,且和.v檔案放在同一資料夾下,以方便觀察和管理。

1.3.10 符號部分

“;”分號用於每一句程式碼的結束,以表示結束,和C語言一樣。

“:”冒號,用在陣列,和條件運算子以及case語句結構中。case結構會在後面講解。

“<=”賦值符號,非阻塞賦值,在一個always模組中,所有語句一起更新。它也可以表示小於等於,具體是什麼含義編譯環境根據當前程式設計環境判斷,如果“<=”是用在一個if判斷裡如:if(a <= 10);當然就表示小於等於了。

“=”阻塞賦值,或者給訊號賦值,如果在always模組中,這條語句被立刻執行。阻塞賦值和非阻塞賦值將再後面詳細舉例說明。

“+,-,*,/,% ”是加、減、乘、除運算子號,這些使用和C語言基本是一樣的,當你用到這些符號時,編譯後會自動生成或者消耗FPGA原有的加法器或是乘法器等。其中符號/,%會消耗大量的邏輯,謹慎使用。

“<”小於,比如A<B含義就是A和B比較,如果A小於B就是TURE,否則為FALSE。

“<=”小於等於,比如A<=B含義就是A和B比較,如果A小於等於B就是TURE,否則為FALSE。

“>”大於,比如A>B含義就是A和B比較,如果A大於B就是TURE,否則為FALSE。

“>=”大於等於,比如A>=B含義就是A和B比較,如果大於等於B就是TURE,否則為FALSE。

“==”等於等於,比如A==B含義就是A和B比較,如果A等於B就是TURE,否則為FALSE。

“!=”不等於,A!=B含義是A和B比較,如果A不等於B就是TURE,否則為FALSE.

“>>”右移運算子,比如A>>2表示把A右移2位。

“<<”左移運算子,比如A<<2表示把A左移2位。

“~”按位取反運算子,比如A=8’b1111_0000;則~A的值為8’b0000_1111;

“&”按位於與,比如A=8’b1111_0000;B=8’b1010_1111;則A&B結果為8’b1010_0000;

“^”異或運算子,比如A=8’b1111_0000;B=8’b1010_1111;則A^B結果為8’b0101_1111;

“&&”邏輯與,比如A==1,B==2;則A&&B結果為TRUE;如果A==1,B==0,則A&&B結果為FALSE,一般用於條件判斷。

A = B ? C : D是一個條件運算子,含義是如果B為TRUE則把C連線A,否則把D連線A。B通常是個條件判斷,用小括弧括起:

assign C1_Clk = (C1==25'd24999999) ? 1 : 0 ;

C1_Clk,是一個wire型別的訊號,當C1==25'd24999999時候,連線到1,否則連線到0.

“{}”在Verilog中表示拼接符,{a,b}這個的含義是將括號內的數按位並在一起,比如:{1001,1110}表示的是10011110。拼接是Verilog相對於其他語言的一大優勢,在以後的程式設計中請慢慢體會。

1.4 Verilog中數值表示的方式

如果我們要表示一個十進位制是180的數值,在Verilog中的表示方法如下:

二進位制:8’b1011_0100; //其中“_”是為了容易觀察位數,可有可無。

十進位制:8’d180;

16進位制:8’HB4;

1.5 阻塞賦值和非阻塞賦值詳解

說到阻塞賦值和非阻塞賦值,是很多初學者很迷惑的地方。原因是C語言沒有可以類比的東西。

學習FPGA和微控制器最大的區別在於,學FPGA時,你必須時刻都有著時鐘的概念。不像微控制器時鐘相關性比較差,FPGA你必須卻把握每一個時鐘。

首先來說說非阻塞賦值,這個在時序邏輯中隨處可見:

| reg A; reg B; always @(posedge clk) begin A <= 1'b1; B <= 1'b1; /***或者** B <= 1'b1; A <= 1'b1; *********/ end

|

這段程式裡,A和B是同時被賦值的,具體是說在時鐘的上升沿來的時刻,A和B同時被置1。調換A和B的上下順序,將得到相同的結果。

接著看另外一段程式:

| reg A; reg B; always @(posedge clk) begin A <= 1'b1; end always @(posedge clk) begin B <= 1'b1; end

|

這段程式,與第一段程式也是完全等價的,A和B在同一時刻被賦值。兩段程式綜合出的邏輯也是完全相同的。這就是非阻塞賦值的特點,體現了FPGA的並行性!

接著來看阻塞賦值,它少了一個非,表示會阻塞住,那麼體會下這個阻塞:

| always @(posedge clk) begin A = 1'b1; B <= 1'b1; end

|

看到,上面這個程式是阻塞和非阻塞的混合使用,一般教材是極力反對這種寫法的。其實只要你理解了,有的時候這種用法還能幫上大忙。只不過,不理解的話亂用會導致時序違規。

回到正題,我們這麼寫是為了更好的理解阻塞賦值:當時鐘上升沿來臨的時刻,首先A會被置1,然後B暫存器再置1。區別就是A和B不再同時置1。A要比B提前零點幾納秒。這樣就出現了先後順序。這個過程還是在一個時鐘內完成的,但是資料到達B暫存器相比上面兩段程式晚了那麼零點幾納秒!

當我們的時鐘跑的比較慢的時候,比如50M,一個週期有20ns,那麼這麼短暫的延時基本可以忽略不計,但是隨著設計的複雜,以及時鐘速度的提高,這樣的語句就要小心。

假設,我們要計算AB求和再除以2的結果。先用非阻塞方法去實現,由於AB求和再除以2是兩個步驟,而非阻塞所以的事情都在一個時鐘完成,所以這裡我們用狀態機,將兩個步驟分配到兩個時鐘裡去完成:

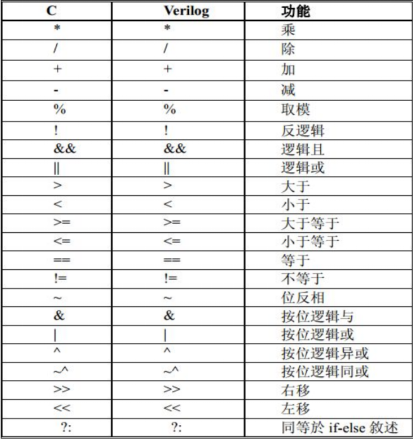

| module unblock ( input clk_i, input rst_n_i, output reg [4:0]result_o ); reg [3:0]A; reg [3:0]B; reg [4:0]C; reg i; always @(posedge clk_i ) if(!rst_n_i) begin #2 A <= 4'd4; B <= 4'd12; C <= 5'd0; result_o = 5'd0; end else begin #2 C <= A + B; result_o <= (C >> 1); end endmodule |

第一個時鐘上升沿來臨時,完成C <= A + B;

第二個時鐘來臨時完成result <= (C >> 1);

求出結果,這個過程耗費兩個時鐘。(不考慮復位消耗的時鐘)

再來,用新增阻塞的方式實現:

| module block( input clk_i, input rst_n_i, output reg [4:0]result_o ); reg [3:0]A; reg [3:0]B; reg [4:0]C;

always @(posedge clk_i) if(!rst_n_i) begin #2 A = 4'd4; #0.2 B = 4'd12; #0.2 C = 5'd0; #0.2 result_o = 5'd0; end else begin #2 C = A + B; #0.2 result_o = (C >> 1); end

endmodule |

模擬結果:

先通過阻塞的方法提前得到C的值,再將C右移1位,達到除以2的效果。整個過程耗時一個時鐘。

以上的程式並沒有什麼實際的參考價值,但是解釋清楚阻塞和非阻塞賦值,它已經做到了~~。

講到這裡,筆者以最快的速度,最簡單的方式,讓讀者學習了Verilog語言的語法部分。具備這些基礎知識,下面筆者將帶你通過程式碼來學習Veriog語言。最後,筆者提一點建議,學習Verilog多看別人寫的優秀的程式碼,多看官方提供的程式碼和文件。其中官方提供的程式碼,很多時候代表了最新的用法,或者推薦的用法。讀者學習,首先把最最基礎的掌握好,這樣,在專案中遇到了問題,也能快速學習,快速解決。

對於理論知識的學習,沒必要一開始就研究得那麼深刻,只是搞理論學習,對於學習Verilog語言,或者FPGA開發是不實際的,要聯絡理論和實踐結合。多模擬,多驗證,多問題,多學習,多改進。

1.6 Verilog HDL程式碼規範

- 專案構架設計

專案的構架用於團隊的溝通,以及專案設計的全域性把控

- 介面時序設計規範

模組和模組之間的通過模組的介面實現關聯,因此規範的時序設計,對於程式設計的過程,以及程式的維護,團隊之間的溝通都是非常必要的。

- 命名規則

1、頂層檔案

物件+功能+top

比如:video_oneline_top

2、邏輯控制檔案

介於頂層和驅動層檔案之間

物件+ctr

比如:ddr_ctr.v

3、驅動程式命名

物件+功能+dri

比如:lcd_dri.v、uart_rxd_dri.v

4、引數檔案命名

物件+para

比如:lcd_para.v

5、模組介面命名:檔名+u

比如lcd_dir lcd_dir_u(........)

6、模組介面命名:特徵名+檔名+u

比如 mcb_read c3_mcb_read_u

7、程式註釋說明

| ////////////////////////////////////////////////////////////////////////////////// // Company: cz123 milinker // Engineer: tjy // bbs:http://www.osrc.cn // taobao:http://osrc.taobao.com // Create Date: 2019/02/27 22:09:55 // Design Name: fdma_controller // Module Name: fdma_controller // Project Name:FDMA_1080P_TS // Copyright: msxbo Copyright (c) 2019 // Revision 0.01 - File Created // Additional Comments: // this codes is used for images frams control //1) _i input //2) _o output //3) _n activ low //4) _dg debug signal //5) _r delay or register //6) _s state mechine |

8、埠註釋

input Video_vs_i,//輸入場同步入

9、訊號命名

命名總體規則:物件+功能(+極性)+特性

10、時鐘訊號

物件+功能+特性

比如:phy_txclk_i、sys_50mhz_i

11、復位訊號

物件+功能+極性+特性

比如:phy_rst_n_i、sys_rst_n_i

12、延遲訊號

物件+功能+特性1+特徵2

比如:fram_sync_i_r0、fram_sync_i_r1

13、特定功能計數器

物件+cnt

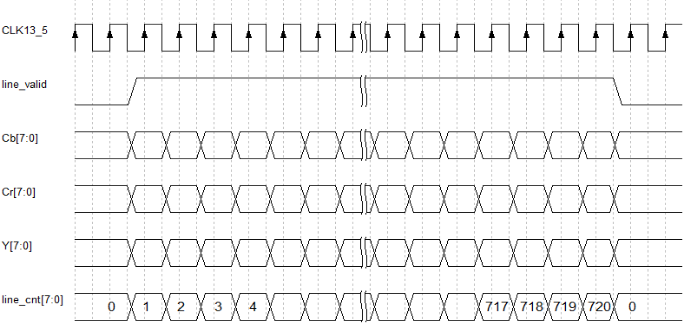

比如:line_cnt、div_cnt0、div_cnt1

功能+cnt

比如:wr_cnt、rd_cnt

物件+功能+cnt

比如:fifo_wr_cnt、mcb_wr_cnt、mem_wr_cnt

物件+物件+cnt

比如:video_line_cnt、video_fram_cnt

14、一般計數器

cnt+序號

用於不容易混淆的計數

比如:cnt0、cnt1、cnt2

15、 時序同步訊號

物件+功能+特性

比如:line_sync_i、fram_sync_i

16、 使能訊號

功能+en

比如:wr_en、rd_en

物件+功能+en

比如:fifo_wr_en、mcb_wr_en

相關推薦

S01-CH01 FPGA設計Verilog基礎(一)

CH01 FPGA設計Verilog基礎(一) 1.1 FPGA技術背景 大規模積體電路設計製造技術和數字訊號處理技術,近

System Verilog基礎(一)

學習文字值和基本資料型別的筆記。 1.常量(Literal Value) 1.1.整型常量 例如:8‘b0 32'd0 '0 '1 'x 'z 省略位寬則意味著全位寬都被賦值。 例如: wire [7:0] sig1; assign sig1 = '1; //sig1

學習筆記:FPGA設計Verilog基礎(一)——Verilog程式碼規範

本筆記內容轉自米聯客。一、Verilog 設計規範及背景介紹1、專案架構設計專案的構架用於團隊的溝通,以及專案設計的全域性把控2、介面時序設計規範模組和模組之間的通過模組的介面實現關聯,因此規範的時序設計,對於程式設計的過程,以及程式的維護,團隊之間的溝通都是非常必要的。3、

Linux內核設計基礎(一)之中斷處理

family ng- 內存 irq strong 睡眠 sign 技術 struct 假設讓內核定期對設備進行輪詢。以便處理設備,那會做非常多無用功,假設能讓設備在

FPGA 設計 Verilog 基礎(二)

1.1 狀態機設計 狀態機是許多數字系統的核心部件,是一類重要的時序邏輯電路。通常包括三個部分:一是下一個狀態的邏輯電路,二是儲存狀態機當前狀態的時序邏輯電路,三是輸出組合邏輯電路。通常,狀態機的狀態數量有限,成為有限狀態機(FSM)。由於狀態機的所有觸發器的時鐘由同一脈衝

FPGA 學習之路(一)EDA軟體設計流程

以QuartusII13.0EDA軟體為例,介紹Verilog文字輸入的EDA設計流程。 1.首先在D盤或G盤等新建一個資料夾,用英文字母命名,例如建立資料夾SY1。 FPGA工程目錄 : de

python大法之二-一些基礎(一)

計算機編程 python 獨立博客 hello 解釋器 個人獨立博客出處:http://www.xbman.cn/出處:http://www.xbman.cn/article/3Python是一種解釋性計算機編程語言。采用縮進式語法,寫起來的感覺有點像排了版的shell,這裏要註意寫pyt

系統分析與設計學習筆記(一)

學習 掌握 應該 溝通 基本 最終 表示 對象 毫無 為什麽要學習這門課程? “擁有一把錘子未必能成為建築師”。 這門課程學習的是面向對象分析和設計的核心技能的重要工具。對於使用面向對象技術和語言來,創建設計良好、健壯且可維護的軟件來說,這門課程所

Linux基礎(一)

顯示文件 單用戶 重要 命令 普通 art 免費使用 出現 文件夾 一、了解Unix和Linux 1.Unix和Linux的起源 出現分時操作系統的概念後,貝爾實驗室和通用電氣在CTTS成功研制後決定開發能夠同時支持上百終端的MULTICS,但是失敗了。後來一位參加過M

23種設計模式介紹(一)---- 創建型模式

接口 ret static 深復制 return 對象 相互 object c png 由於設計模式篇幅比較大,如果在一篇文章講完所有的設計模式的話不利於閱讀。於是我把它分為三篇文章 23種設計模式介紹(一)---- 創建型模式 23種設計模式介紹(二)---- 結構型模

DOM 基礎(一)

引號 nod pro 操作符 結果 所有組 數組 tag 方式 DOM(document object model)由節點構成,元素節點,文本節點,屬性節點是一份DOM的所有組成。 <p id="p">this is a node</p>

Jquery基礎(一)

4.2 aaa round next apu eat addclass 3.1 什麽 一 jQuery是什麽? <1> jQuery由美國人John Resig創建,至今已吸引了來自世界各地的眾多 javascript高手加入其team。 &

Java基礎(一)異常處理關鍵字:try catch finally throw throws

cut main 5.1 模型 指針 str control 情況 實例 嗨咯,大家晚上好,我的博客首篇開始了 ,我們一起加油吧! 都說java 語言是非常健壯性 如:垃圾回收機制、內存模型、異常處理,強類型轉換、跨平臺,等等,使得Java語言的受到青睞。今天我們先來聊

計算機系統基礎(一)

指令譯碼 多核cpu 數據處理 計數 sin 單元 中央處理器 ssi 緩沖 計算機硬件系統 :運算器、控制器、存儲器、輸入設備、輸出設備 中央處理器(Center Processing Unit,CPU):運算器、控制器 存儲器:內部存儲器、外部存儲器 外部設備:輸

三維渲染引擎設計與時間(一)

註冊 三維 特定 渲染引擎 交互 文件 集合 工具 調度 一、初始osg 三維渲染引擎:為了實現三維場景圖形的結構管理和繪制而提供的一系列API的集合。包括構建層和交互層。 Crystal Space、Java3D、Unreal…… osg庫:構件場景圖形的場景圖形節點類、

Linux下MySQL的基礎(一)

mysql基於解釋MYSQL的基礎1. MySQL服務器中幫助的使用格式: mysql> help command eg: mysql> help create database Name: ‘CREATE DATABASE‘ Description: Sy

Python基礎(一)

類型 spa 例子 hat except 存在 內容 限制 字符數 Python基礎1 1.Hello World程序 2.變量 3.用戶輸入 4.模塊初識 5.數據類型初識 6.數據運算 7.表達式if ...else語句 8.表達式fo

Django基礎(一)

forever sha 以及 sta sim localhost 3.1 tro def 一 什麽是web框架? 框架,即framework,特指為解決一個開放性問題而設計的具有一定約束性的支撐結構,使用框架可以幫你快速開發特定的系統,簡單地說,就是你用別人搭建好的舞臺來做

Javascript 基礎(一)

個數 復制 oat con test 代碼 轉換成 com ros 彈窗: alret(“要彈出的內容”);彈出來之後不點確定網頁不會執行下去 confirm("要彈出的內容");確定對話框,點確定返回True,點取消返回False,可用變量接受 promp

設計模式學習(一)-概述

項目 site 相對 實體 pattern 需要 gre 維護 pri 設計模式(Design Patterns) ——可復用面向對象軟件的基礎 設計模式(Design pattern)是一套被反復使用、多