米聯客 ZYNQ/SOC 精品教程 S05-CH06 可程式設計差分晶振 Si570 使用

6.1概述

使用 FPGA 的高速序列收發器(GTP、GTX 等)設計不同傳輸速率的高速介面時,往往需要收發器所在 BANK 的差分參考時鐘引腳提供不同頻率的參考時鐘輸入。例如,1G-BASEX:125M,Display Port :135M,SATA :120M, 3G-SDI:148.5M,10G-BASER:156.25M。收發器的參考時鐘一般都直接由差分晶振所提供。

為了提高 MIZ7035 開發板 GTX 使用的靈活性,在底板中搭載了 1 款頻率可程式設計的差分晶振 Si570,將其輸出作為GTX Bank 的參考時鐘。

MIZ7035 所使用的 Si570 的輸出頻率可在 10~810M 之間進行任意調節。通過 I2C 介面對其內部暫存器進行設定,使用者便可以獲得所需要頻率的時鐘。可以更好的滿足不同應用場合、不同型別和傳輸速率的高速介面對於參考時鐘頻率的要求。

本教程介紹了 Si570 的工作原理以及使用方法,通過 PS 的 I2C 介面實現對Si570 時鐘輸出頻率的動態配置,同時,通過 PL 粗略測算所設定頻率的值是否正確。本教程參考了 Xilinx KC705 開發板的參考設計rdf0194-kc705-si570-prog-c-2014-3 以及 xtp204-kc705-si570-prog-c-2014-3。

6.2 Si570 介紹

6.2.1基本結構

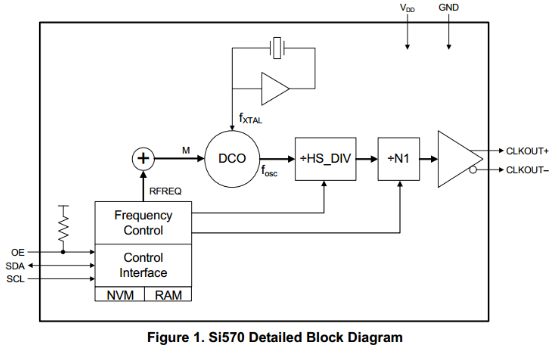

Si570 的內部結構如下圖所示。

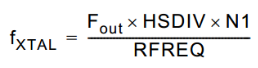

其輸出就是由晶振內部振盪器產生的固定頻率為 fXTAL 的時鐘經過 1 次倍頻和 2 次分頻而獲得。輸出時鐘頻率

fout 的計算公式為:

輸出時鐘頻率fout 由 fDCO 和輸出分頻係數所決定。

fDCO=fXTAL×RFREQ

其中,晶振內部振盪器產生的時鐘頻率 fXTAL≈114.285000000MHz。需要說明的是,fXTAL 不是一個完全準確的值,由於生產工藝的限制,對於每一個晶振,fXTAL 都會存在細微的差別。RFREQ 是 38bit 的倍頻係數,其高 10bit 為整數,低 28bit 為小數。由於fDCO 的可設定範圍為 4.85G~5.67GHz,因而倍頻係數RFREQ 也有一個固定的範圍。另外,HSDIV 為 3bit 的分頻係數,N1 為 7bit 的分頻係數,兩者均為整數。

簡而言之,對於使用者來說,在 Si570 上獲取所需要頻率的時鐘就是通過I2C 介面對上述公式中的RFREQ、HSDIV

和 N1 共 3 項引數進行設定。

每個 Si570 都有一個預設的上電頻率和 I2C 地址,兩者都是可選的,具體組合和型號對應關係可以諮詢生產商。在出廠時,這兩個預設值都寫入其內部的 Flash 裡,使用者後續都無法更改。晶振雖然可以在上電狀態下通過 I2C 設定改變輸出頻率,但是重新上電後又會從 Flash 里加載出廠設定輸出預設的上電頻率。

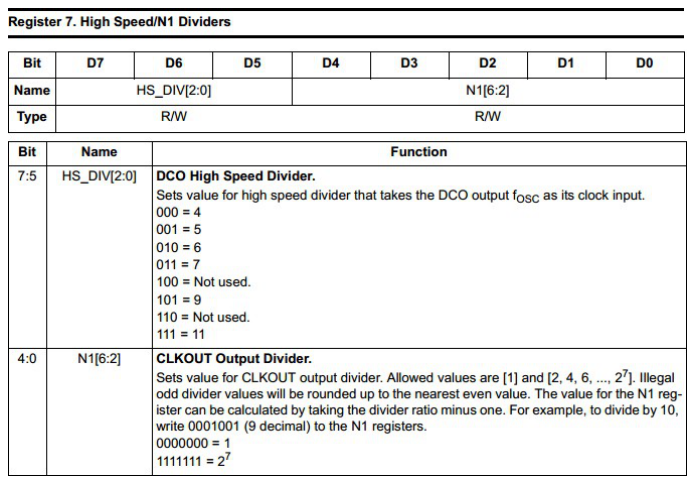

6.2.2 暫存器

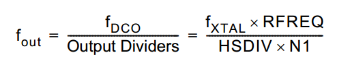

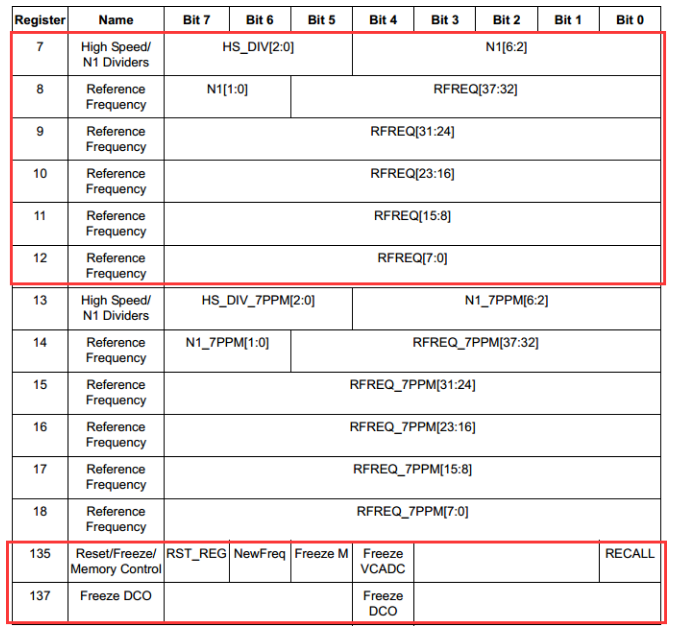

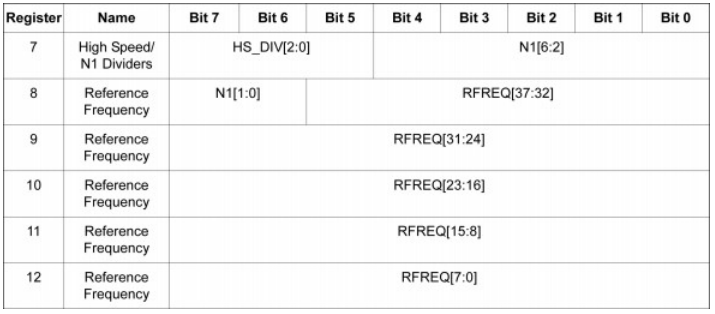

Si570 內部的暫存器如下圖所示。其中我們只需要關注。暫存器 7~12,以及 135、137。

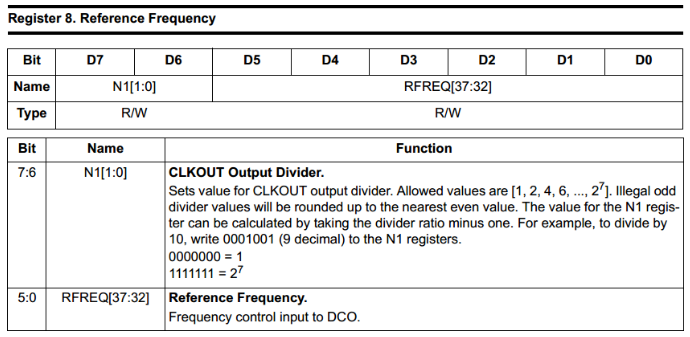

6.2.2.1 暫存器 7、8

暫存器 7 和暫存器 8 的 bit[7:6]用於設定分頻係數HSDIV 和N1。具體含義如下圖所示。

6.2.2.2 暫存器 8~12

暫存器 8~12 用於設定 38bit 的倍頻係數RFREQ。

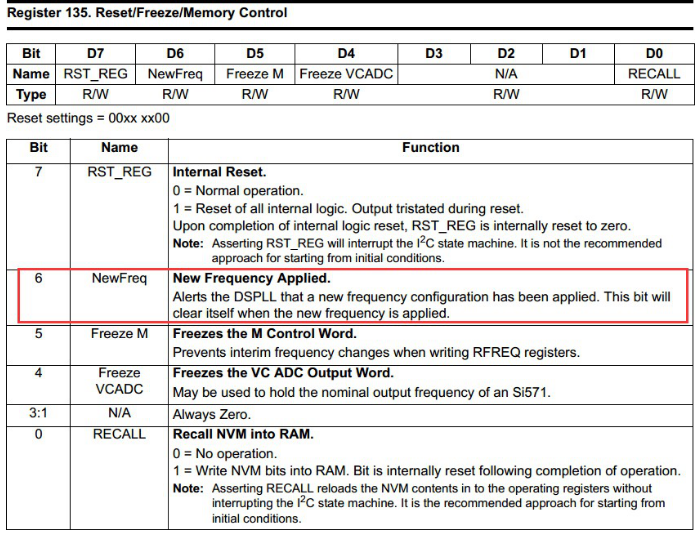

6.2.2.3 暫存器 135

暫存器 135 的定義如下圖所示。該暫存器主要用於晶振的控制,在重新配置晶振的頻率的過程中一般只需要用到 bit6。

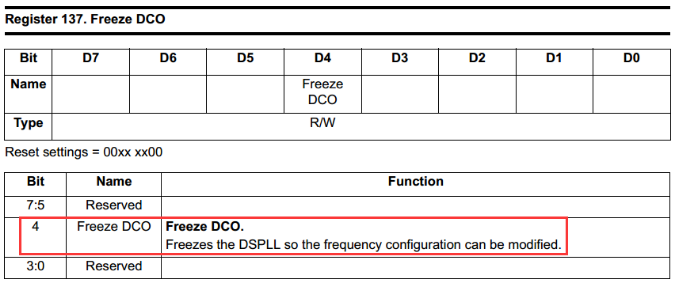

6.2.2.4 暫存器 137

暫存器 137 定義如下圖所示。該暫存器用於鎖住 DCO 的頻率。在對晶振頻率進行重新設定時必須用到這個暫存器。

6.3使用方法

6.3.1引數計算原理

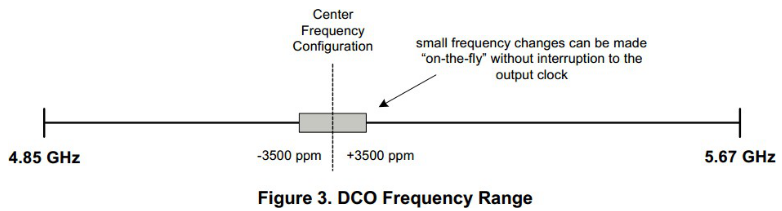

晶振上電後以預設頻率輸出時鐘。此時若需要改變輸出頻率,首先,需要計算需要設定的倍頻係數 RFREQ、以及分頻係數 HSDIV 和 N1。對於引數計算需要分 2 種情況進行討論。以 DCO 的中心頻率±3500ppm(±0.35%) 範圍作為劃分。如下圖所示。

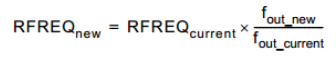

第一種情況,當晶振輸出頻率更改所造成的 fDCO 變化在 fDCO 中心頻率的±3500ppm(±0.35%) 範圍內。則只需要對倍頻係數 RFREQ 進行重新設定就可以直接改變輸出頻率。晶振工作不會造成中斷,輸出頻率進行動態改變。新的倍頻係數 RFREQ 計算方法如下:

例如,輸出頻率從 148.35MHz 變為 148.5MHz。新倍頻係數RFREQ 計算過程如下:

第二種情況,當晶振輸出頻率更改所造成的 fDCO 變化超過 fDCO 中心頻率的±3500ppm(±0.35%) 範圍。則倍頻係數 RFREQ 和分頻係數 HSDIV、N1 都需要進行更改。此時,更改將使晶振輸出產生短暫的中斷,然後才會輸出新頻率的時鐘。

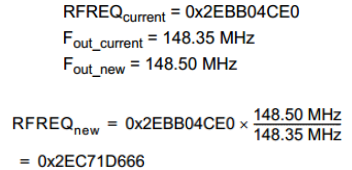

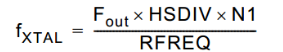

要計算新的 RFREQ、HSDIV、N1 值,必須先計算出晶振內部的固定頻率fXTAL。這裡再次強調,由於每個晶振的 fXTAL 都會存在細微差異,因此每一個晶振的引數設定都是唯一的,不能適用於其他任何 1 個相同型號的 Si570。要計算 fXTAL,必須先通過I2C 讀出晶振在當前頻率下暫存器 7~12 中對應的 RFREQ、HSDIV、N1 值。然後通過如下公式計算出 fXTAL 的值。

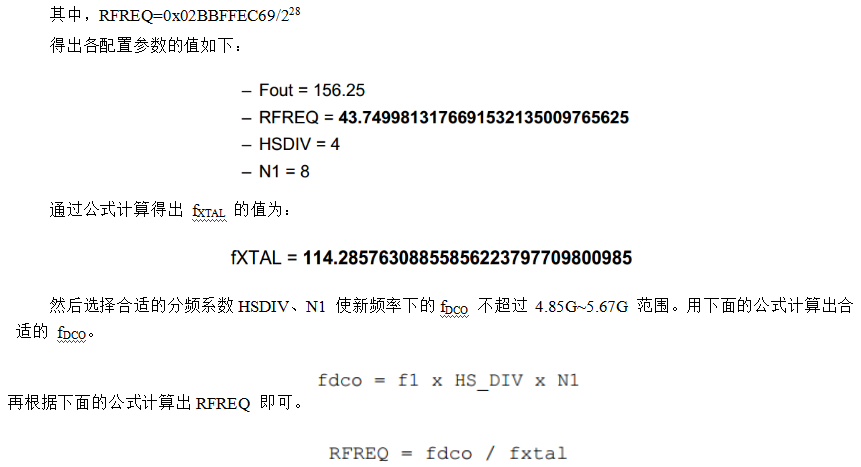

例如,當前頻率為 156.25MHz,讀出各暫存器值如下:

6.3.2引數計算步驟

綜上所述,引數的計算步驟可以總結為 5 個步驟,如下圖所示。(由 156.25M 變為 200M)。

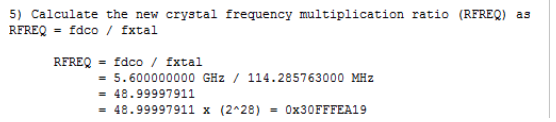

由於HSDIV、N1 值的選擇以及 RFREQ 的計算比較繁瑣。可以藉助Silicon 官方的設定工具來進行計算。(下載頁面:https://www.silabs.com/products/development-tools/software/oscillator-software-tools

下載地址:https://www.silabs.com/documents/login/software/ProgOscillatorSwInstall.zip

)。

安裝完成後,開啟Programmable Oscillator Calculator,如下圖,選擇 Si570,然後點選 OK。

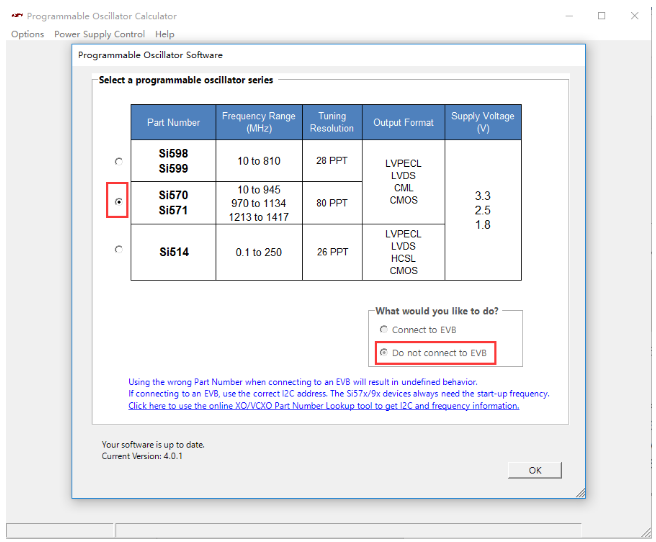

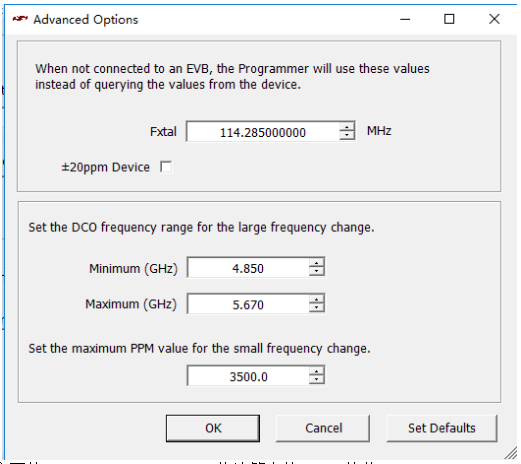

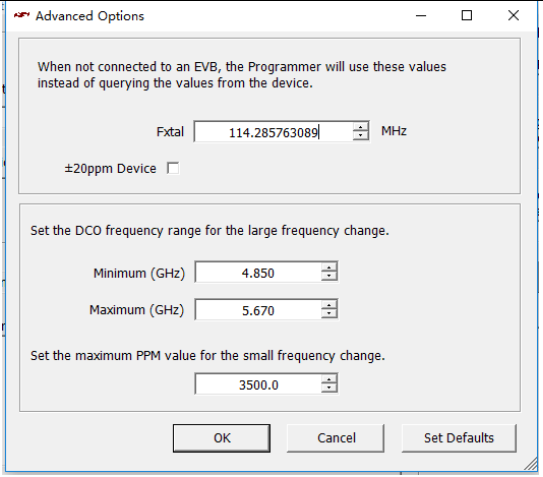

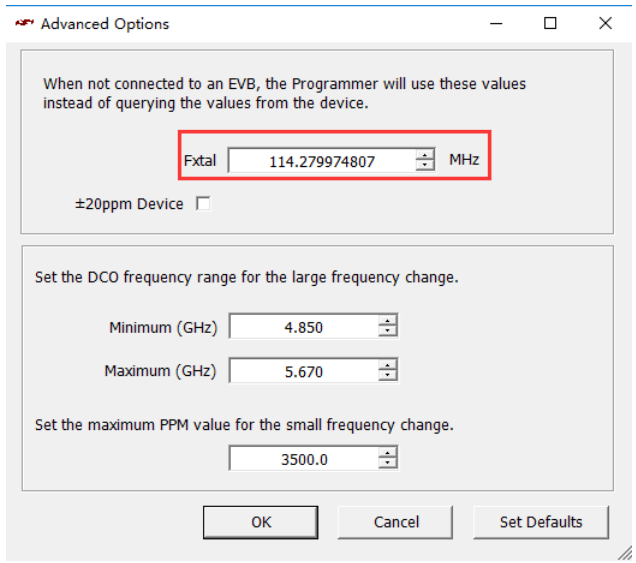

選擇Option,Advanced。如下圖所示。

可以看到 fXTAL 的預設值為 114.285M。如下圖所示。

輸入根據當前頻率下的RFREQ、HSDIV、N1 值計算出的 fDCO 的值,

![]()

軟體會自動近似成最相近的值。然後點選 OK。如下圖所示。

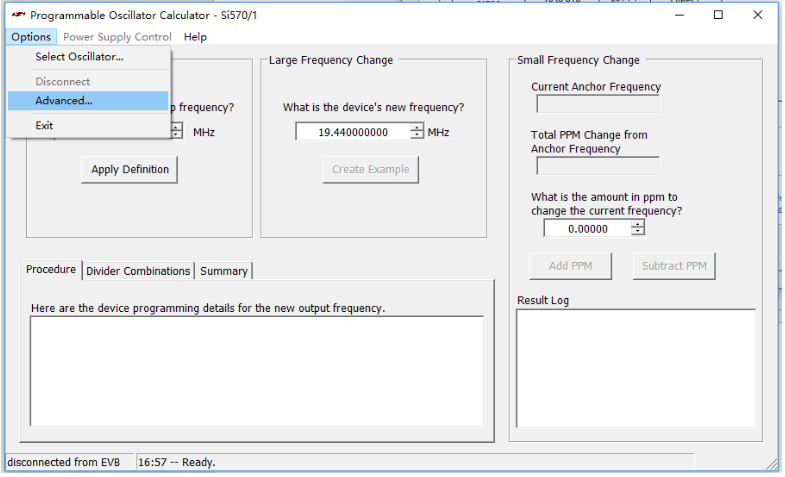

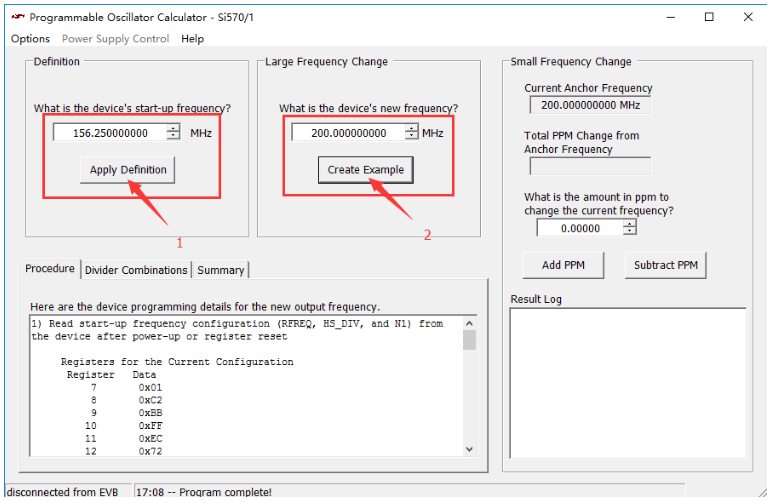

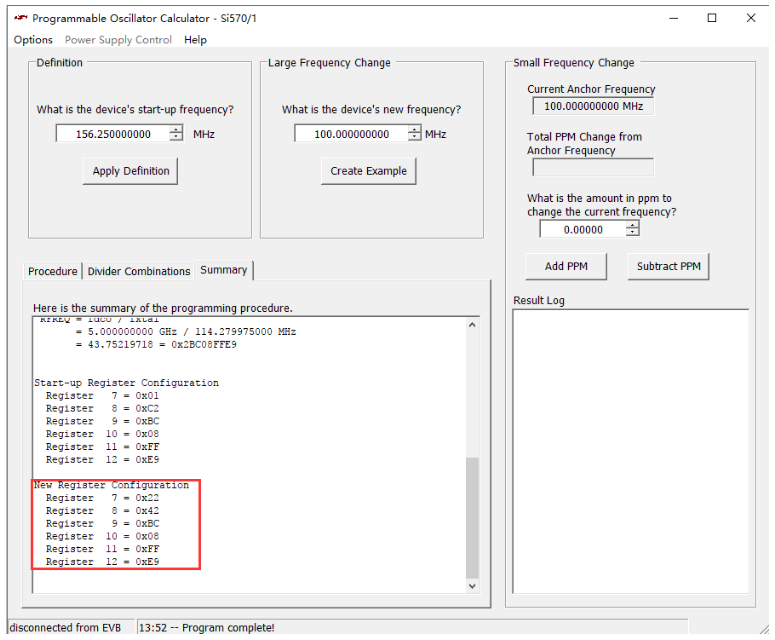

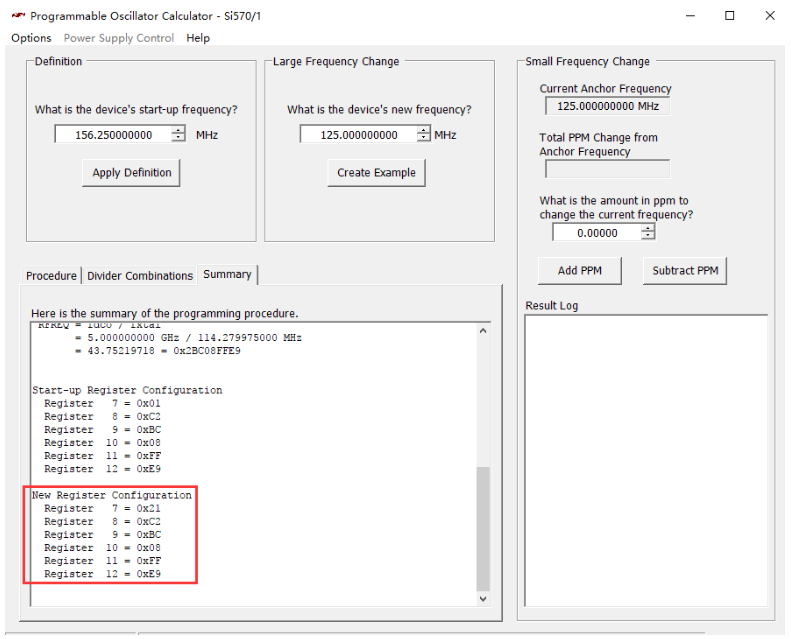

輸入當前頻率值 156.25MHz,點選Apply Definition,輸入要設定的頻率 200MHz,點選 Create Example。如下圖所示。

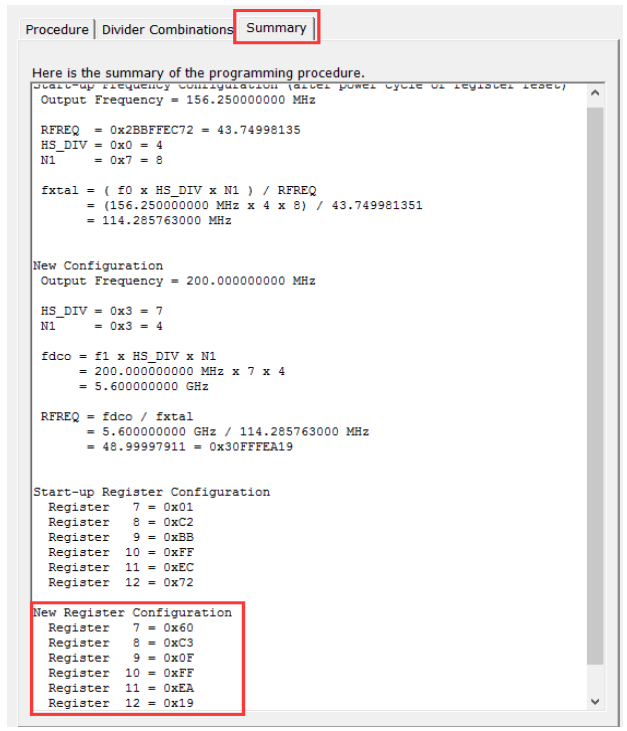

軟體將會自動生成所需要設定的值,並在 summary 裡顯示計算過程。如下圖所示。

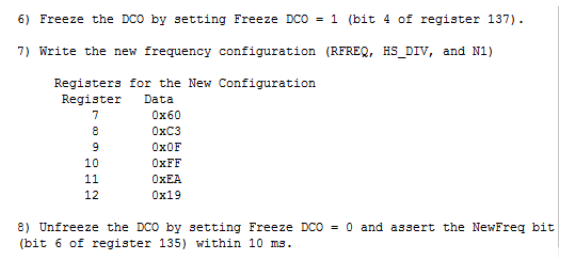

6.3.3暫存器配置

當計算出所需的倍頻係數RFREQ,以及分頻係數 HSDIV、N1 後,需要將這些值通過 I2C 寫入暫存器中。暫存器的配置分為 3 個步驟。如下圖所示。

6.3.4 I2C 配置原理

6.3.4.1讀暫存器

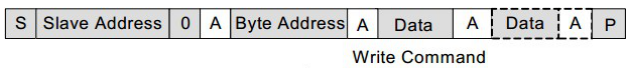

Si570 I2C 暫存器配置過程如下圖所示。可以對單個暫存器值進行配置,也可以對地址連續的暫存器進行連續配置。連

續配置只需要傳送起始暫存器的地址即可,這種方式配置較為方便。

6.3.4.2寫暫存器

Si570 I2C 暫存器值讀取過程如下圖所示。同理,可以對單個暫存器值進行讀取,也可以對地址連續的暫存器進行連續讀取。連續

讀取只需要傳送起始暫存器的地址即可。

6.3.4.3 I2C 地址

不同型號的 Si570 具有不同的 I2C 地址,MIZ7035 開發板中所使用的型號為 570BAB000544DG,其 I2C 地址為 0x5D。

6.4程式設計

6.4.1PL 端設計

6.4.2 PS 配置

將PS 的 I2C0 通過EMIO 方式引出,如下圖所示。

![]()

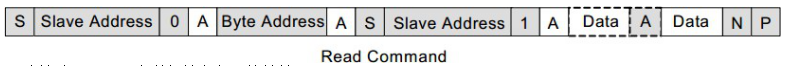

通過PS 引出 1 個 200M 的時鐘,作為PL 部分對Si570 時鐘頻率測算的參考時鐘。如下圖所示。

6.4.2.1 Si570 頻率測算

為了驗證 PS 端配置 Si570 輸出時鐘頻率的正確性,在不使用示波器進行測量的前提條件下。可以在 PL 端對Si570 輸入時鐘頻率值進行統計測算,能夠得出較為接近頻率真實值的估計值。這部分設計採用了 Xilinx KC705 開發板的參考設計 rdf0194。

6.4.2.2測算原理

頻率測算由 ibert_freq_counter.v 和 ibert_freq_mult.v 兩個模組完成。

首先,介紹一下頻率測算的原理。測算過程首先要以一個已知頻率的時鐘訊號作為參考,例如,rdf0194 參考設計中使用了 1 個 200MHz 的時鐘。然後,同時以參考時鐘和 Si570 輸入的待測時鐘為基準,各自使用 1 個暫存器同時進行計數。當參考時鐘累加到我們所設定的閾值時,儲存此時待測時鐘的計數值,然後根據比例法便可以計算出此時的待測時鐘的頻率。

為了使最終的統計結果能夠直觀的反映出頻率值,且能保留 2 位小數。例如,200M 的時鐘的十進位制統計值為20000,156.25M 時鐘的十進位制統計值為 15625。需要將上述的暫存器計數值乘以 1 個係數就可得到我們所需要的直觀的統計值。

例程中,ibert_freq_counter 模組負責對參考時鐘和待測時鐘進行暫存器計數,參考時鐘的計數閾值為 16’h4000。當以PS 產生的200M同時作為參考時鐘和待測時鐘時,由於在計數時使用了4 分頻,實際的計數閾值為4096-1=4095。此時,根據這個結果便可以計算出該係數,計算過程如下:

20000/4095≈4.8840=48840/10000。

所以暫存器計數值所需要乘的係數近似為 48840/10000。在 ibert_freq_mult 模組中,將 ibert_freq_counter 模組的計數值通過係數換算成最終的結果。

乘以係數後,為了補償捨去小數部分,將相乘結果再加 1 便可以得到最終結果。需要注意的是,該結果只是近

似統計,由於非同步取樣和小數計算誤差,統計結果可能會存在個位數的誤差(即小數點第 2 位)。但這對於我們直觀判斷設定值是否正確並不存在較大影響。

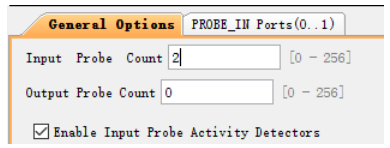

6.4.2.3 VIO

為了便於實時觀察 Si570 輸入待測時鐘的頻率測算值,在 PL 端使用 VIO IP 核通過 vivado 軟體來觀察。VIO 的設

置如下圖所示。

6.5 PS 端程式設計

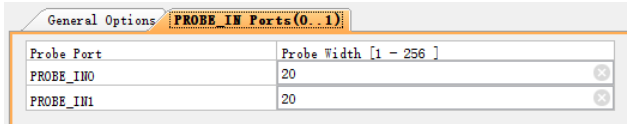

PS 端的主要工作是通過I2C 介面對Si570 的輸出時鐘頻率進行配置。PS 端的設計同樣參考了 Xilinx KC705 開發板的參考設計 rdf0194。

PS 端的工程主要包含以下幾個原始檔,如下圖所示。

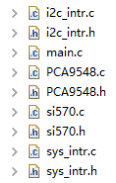

6.5.1 Main 函式

main 函式主要完成如下功能:

- 初始化 ARM 中斷控制器及系統中斷

- 初始化並配置 I2C 介面及其中斷

- 通過 I2C 介面復位 Si570

- 通過 I2C 介面讀取 Si570 的暫存器值,通過串列埠輸出。並從串列埠接收使用者輸入的新暫存器配置值,將其寫入 Si570。

main 函式的執行流程如下圖所示:

6.5.2 I2C 介面

PS 端使用了I2C0 介面,I2C0 工作於 Master 模式。在程式中使用了 I2C 介面的中斷,I2C 介面在資料接收或傳送完成後均會產生中斷。PS 端 I2C 介面的驅動程式在i2c_intr.c 和 i2c_intr.h 檔案中進行定義。

I2C 介面的驅動函式主要包括:

- I2C_init,用於配置和初始化PS的I2C0介面。

- I2C_write,通過I2C介面以Master形式向外部發送資料。

- I2C_read,通過I2C介面以Master形式從外部讀取資料。

- I2C_Setup_Intr_System,配置和初始化I2C介面的中斷。

- Iic_Handler,I2C介面的中斷服務函式。

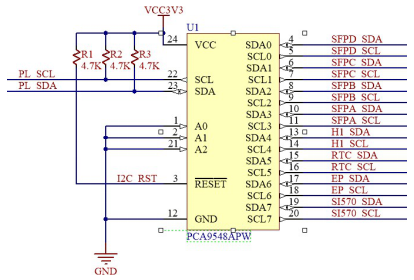

6.5.3配置PCA9548 I2C 通路切換

利用PCA9548晶片可以很方便實現I2C複用通路之間的切換。比如SI570是在通道7只要一條指令就可以完成通路的切換。

PCA9548_sel(PCA9548_ADDRESS,0x81);

具體的函式請看PCA9548.h 和PCA9548.c

6.5.4配置Si570

Si570 的驅動程式在si570.c 和 si570.h 檔案中進行定義。

6.5.3.1 復位

通過 reset_si570 函式可以使Si570 晶振復位,並輸出預設的上電頻率 156.25MHz。

6.5.3.2 讀暫存器

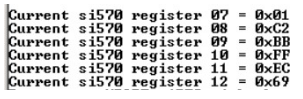

在上文中已經強調過,每 1 個 Si570 晶振的內部 fXTAL 都會存在細微的差別,要對 Si570 進行配置,必須先根據Si570 出廠的預設配置來計算出其內部的 fXTAL 頻率值。因此,在配置 Si570 之前首先要通過 I2C 介面,依次從 Si570 中讀出暫存器 7、8、9、10、11、12 的出廠預設值,根據這些值計算出fXTAL 的精確值。

讀取這些暫存器的過程是通過 read_si570 函式完成。

6.5.3.3 寫暫存器

得出開發板中 Si570 晶振的 fXTAL 值之後,便可以使用 0 節中提到的方法使用官方軟體 Programmable Oscillator Calculator 計算出新頻率下暫存器 7、8、9、10、11、12 所需要設定的值。然後按照 0 節所介紹 3 個步驟將這 6 個暫存器的值寫入 Si570 中,並使之設定生效。

配置這些暫存器的過程是通過 write_si570 函式完成。

6.6 程式測試

6.6.1獲取Si570 預設暫存器配置

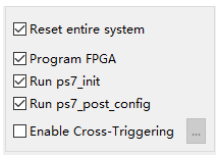

首先,通過 SDK 的system debugger,將PL 的bit 檔案和PS 的elf 檔案同時下載到開發板中。其中,system debugger

的選項應如下圖所示。

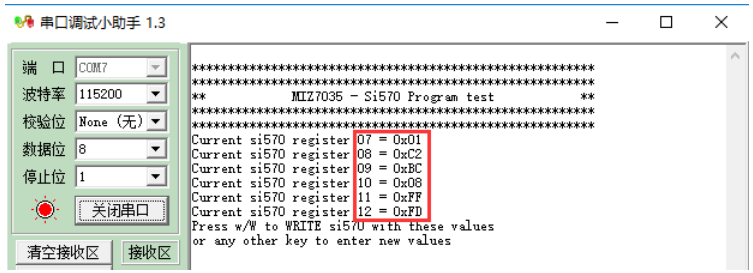

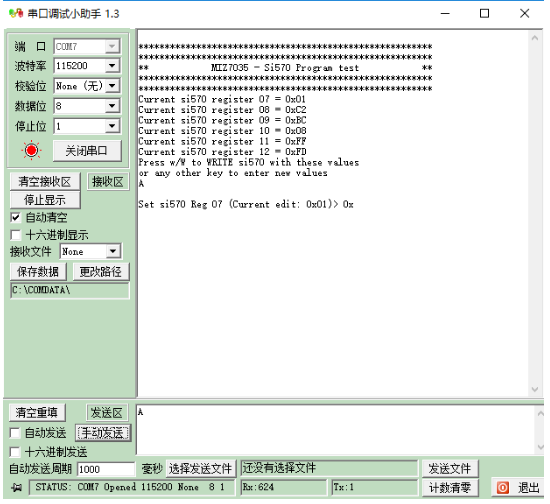

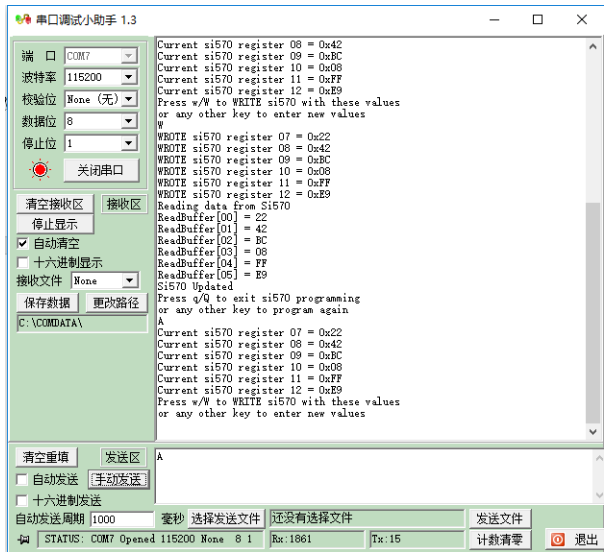

開啟串列埠除錯助手,設定波特率為 115200,連線 MIZ7035 開發板所對應的COM 口,然後使PS 執行程式。此

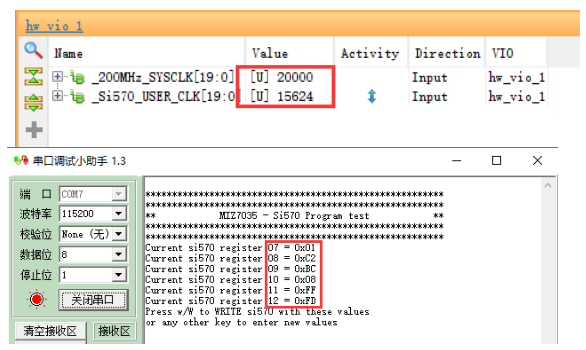

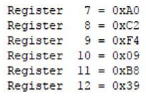

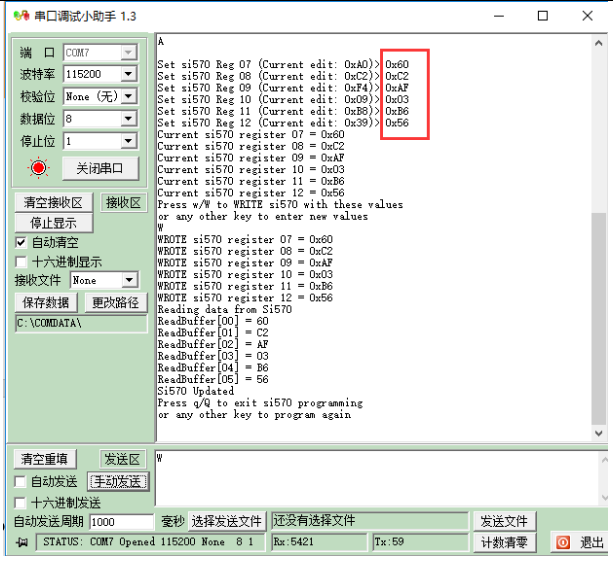

時串列埠除錯助手出現的介面如下圖所示,顯示出當前 Si570 內部出廠預設的暫存器配置。

6.6.2計算晶振的fXTAL

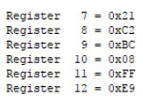

從上圖中便可以得到測試所使用的 MIZ7035 開發板中的 Si570 的預設暫存器配置。需要注意的是,這些值只適用於測試所用的 Si570 晶振。換一個相同型號的 Si570,這些預設配置值必然會存在差別。當用戶對自己的 MIZ7035 開發板進行 Si570 測試時,需要注意這一點,不同的值時完全正常的現象,並不代表錯誤。

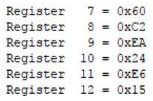

根據下圖,可以獲得所測試的 Si570 相應的引數值。

HS_DIV = 0b000,表示 4;N1=0b0000111,代表 23=8;RFREQ=0x2BC08FFFD ,高 10bit 為整數,低 28bit 為小數,將其除以 228 可得出其實際值為 43.7521972544491291046142578125。已知 Si570 的預設上電輸出頻率為156.25M,然後根據下面的公式計算出 fXTAL ≈ 114.2799748072436210734652474654。

6.6.3輸出頻率引數計算

在Programmable Oscillator Calculator 軟體中輸入上面計算出的 fXTAL 值。軟體會作自動近似,如下圖所示。

接下來便可以在軟體中開始計算 Si570 在不同輸出頻率時的引數值。下面列舉幾個例項。

6.6.3.1 100MHz

6.6.3.2 125MHz

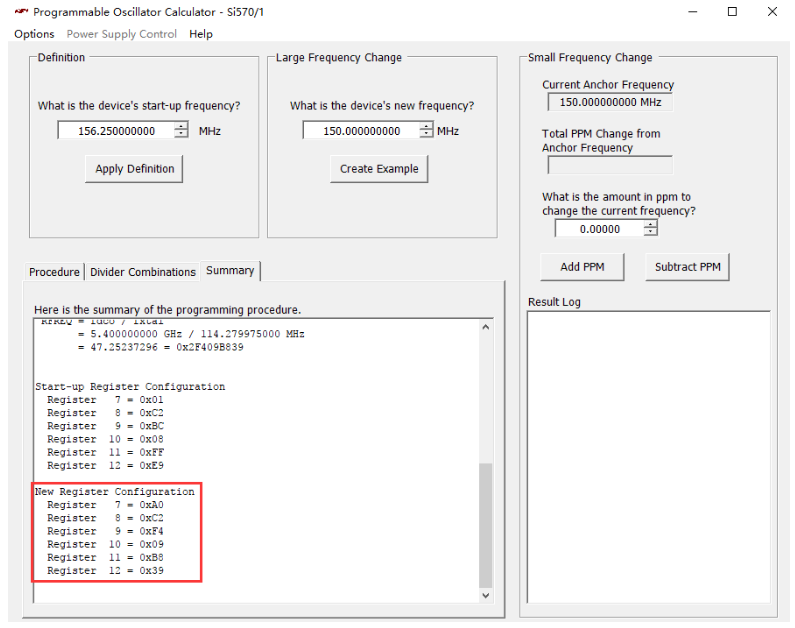

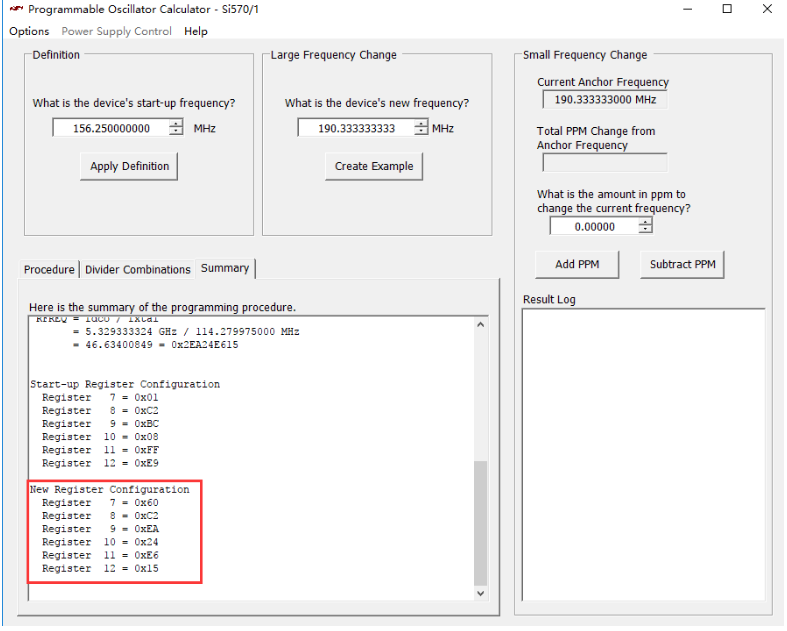

6.6.3.3 150MHz

6.6.3.4 175.25MHz

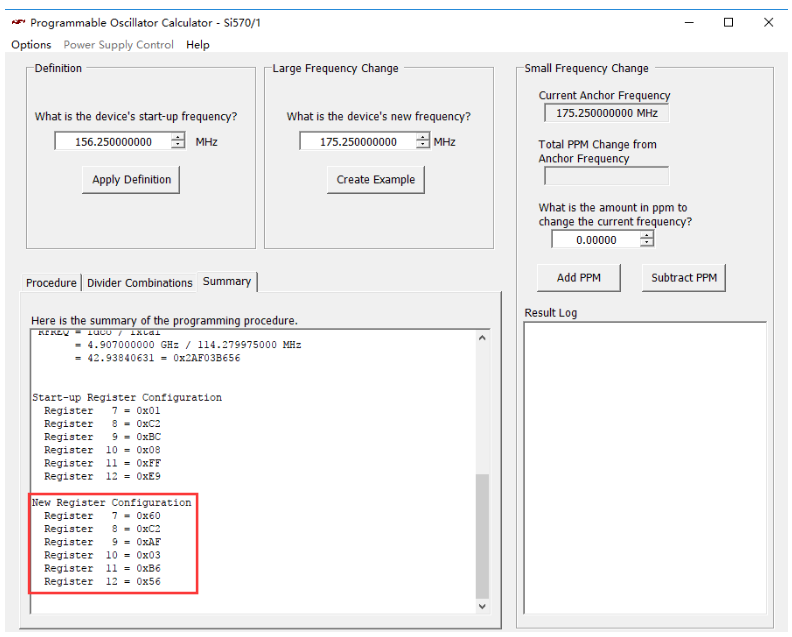

6.6.3.5 190.33MHz

6.6.4更改並監測輸出頻率

6.6.4.1預設上電頻率

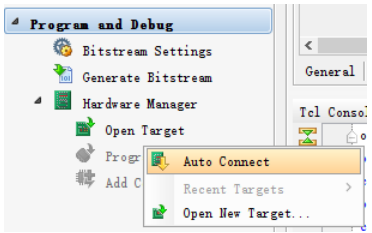

在經過 0 節中的步驟後,接著開啟 vivado 的 hardware manager。點選 Open Target,然後選擇Auto Connect。如下圖所示。

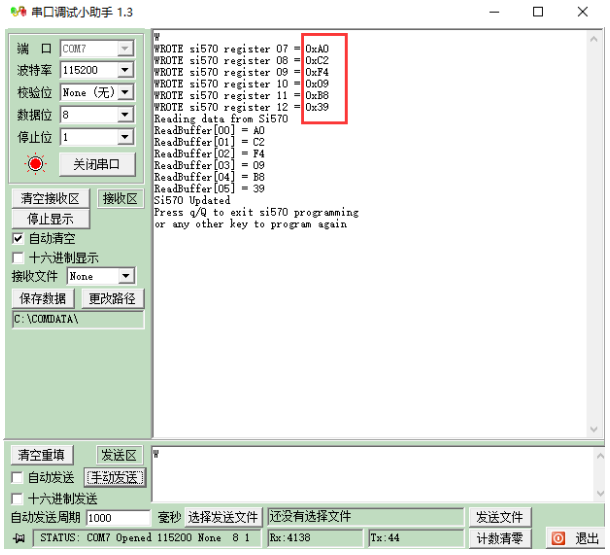

此時,hardware manager 將自動檢測到所下載 bit 檔案中所嵌入的 VIO IP 核,並彈出 vio 介面,如下圖所示。

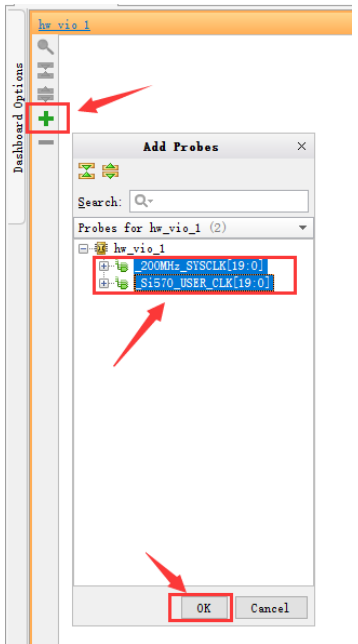

點選“+”按鈕,將VIO 的兩個輸入訊號選中並新增到列表中。如下圖所示

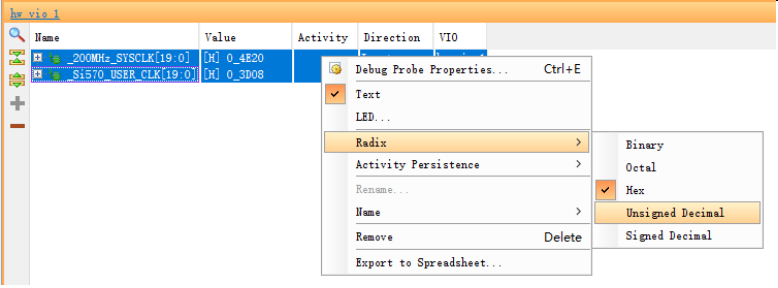

將 2 個頻率統計值的顯示方式改為十進位制,如下圖所示。

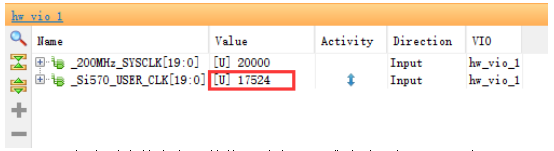

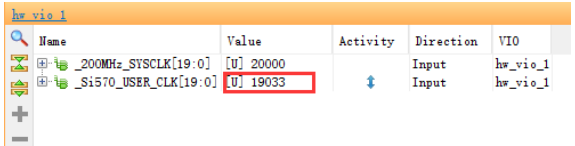

此時,頻率的統計值便可以直觀的顯示出來,如下圖所示。200M 的參考時鐘顯示為 20000,Si570 的預設上電。156.25M 的時鐘顯示為 15624,這裡存在-1 的誤差。

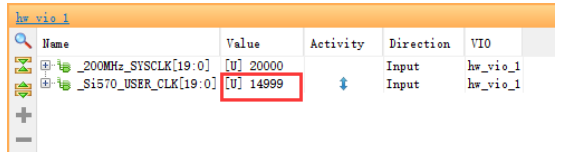

在串列埠除錯助手出現如下Si570 預設暫存器值的介面後。

通過除錯助手輸入 1 個任意除了大小寫 W 之外的字母,便開始進入暫存器配置步驟。例如,通過串列埠除錯助手以ASCII 碼形式輸入“A”,如下圖所示。

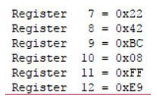

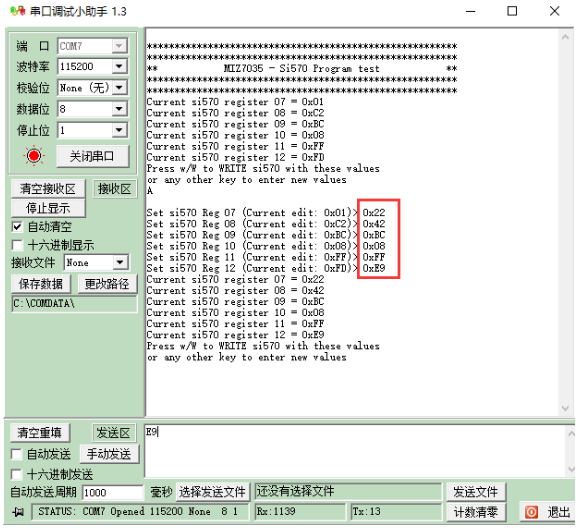

依次以 ASCII 碼形式輸入頻率為 100MHz 時的引數,如下圖所示。

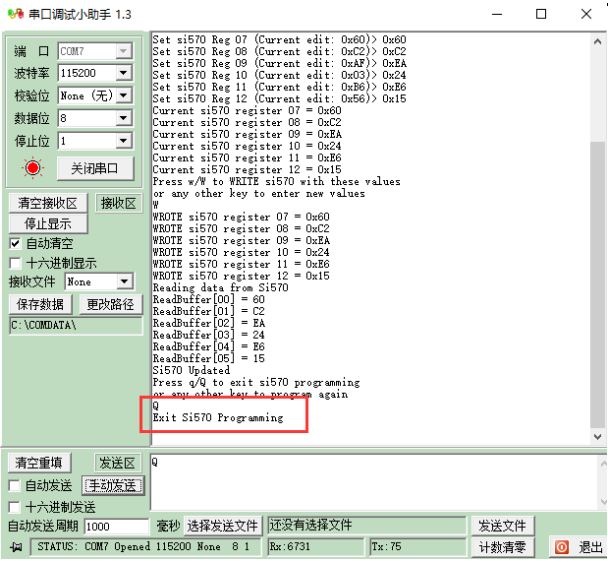

然後,傳送大寫或小寫的 w,代表要將這些值寫入 Si570 對應的暫存器中,如下圖所示。出現下圖的提示,代表此時已經成功完成暫存器配置,Si570 的輸出頻率發生了改變。

下一步,如果想終止程式,則可通過串列埠除錯助手大小寫字母 Q,若要繼續對 Si570 進行程式設計,則傳送其他任意字母即可。通過串列埠除錯助手傳送“A”,繼續對Si570 進行配置。如下圖所示。

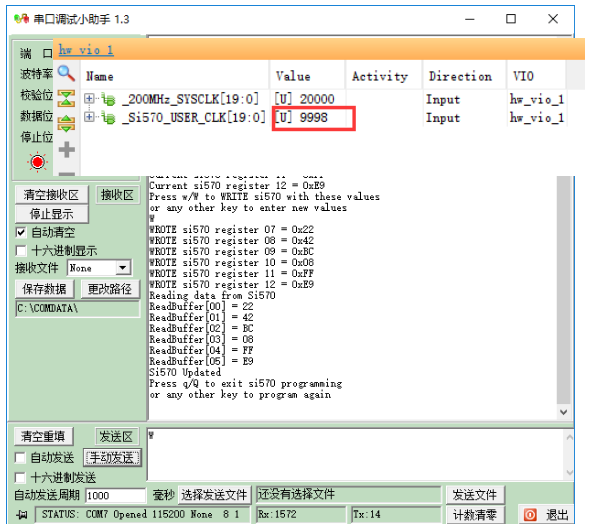

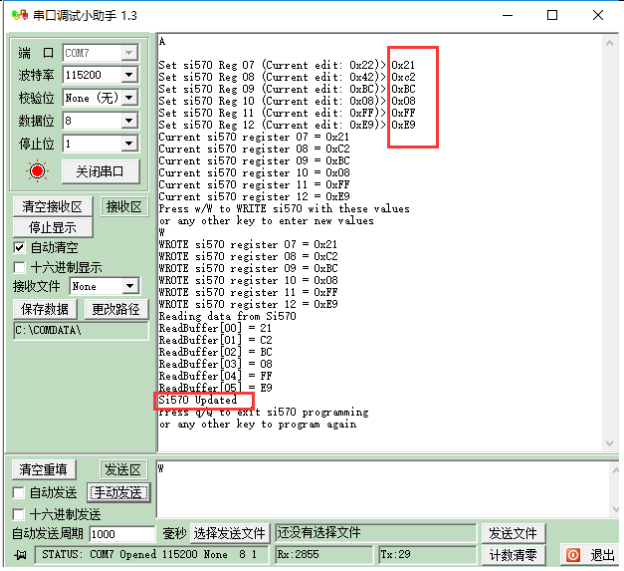

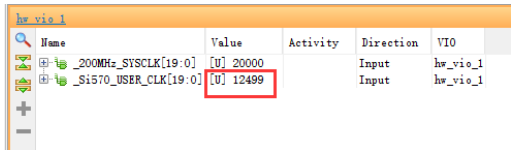

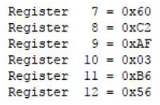

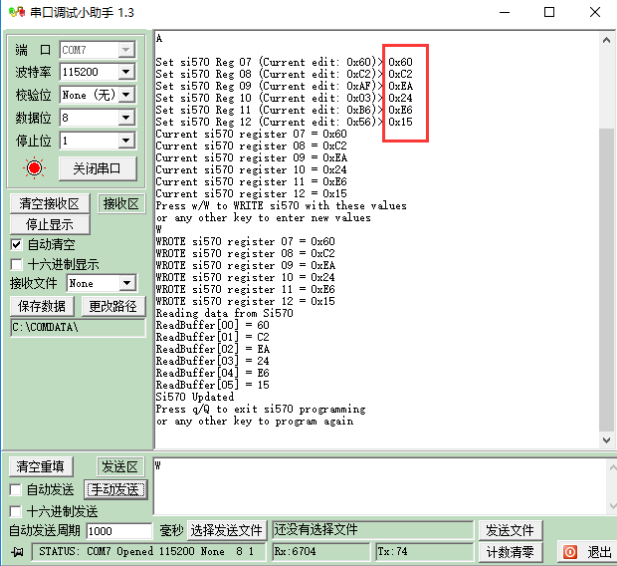

再次輸入“A”,將 125MHz 對應的暫存器數值輸入,然後輸入“W”將其寫入 Si570 中,如下圖所示。

在 VIO 中可以觀察到,此時Si570 輸出頻率測算結果 12499,代表 124.99MHz。如下圖所示。

同理,再將 150MHz 頻率對應的暫存器數值通過串列埠除錯助手寫入 Si570 中。如下圖所示。

在 VIO 中可以觀察到,此時Si570 輸出頻率測算結果 14999,代表 149.99MHz。如下圖所示。

同理,再將 175.25MHz 頻率對應的暫存器數值通過串列埠除錯助手寫入 Si570 中。

在 VIO 中可以觀察到,此時Si570 輸出頻率測算結果 17524,代表 175.24MHz。如下圖所示。

同理,再將 190.33MHz 頻率對應的暫存器數值通過串列埠除錯助手寫入 Si570 中。

在 VIO 中可以觀察到,此時Si570 輸出頻率測算結果 19033,代表 190.33MHz。如下圖所示。

到此,我們所計算的 5 種頻率引數全部配置完成,在串列埠除錯助手傳送“Q”退出程式,如下圖所示。

6.6.4.3說明

VIO 中觀察到的Si570 輸出頻率測算值並不是完全準確的,而且可能會出現小幅度的跳變。該結果只是近似統計, 由於非同步取樣和小數計算誤差,統計結果會存在一定的誤差。僅作為使用者直觀的參考資料。精確測量Si570 的時鐘頻率是否準確,還是需要依靠示波