從延遲觸發器鏈到邊沿檢測

本文記錄一下關於延遲觸發器鏈與它的常用用法(即邊沿檢測。多級延遲的觸發器應該是比較常用的,當我們需要對信號信號進行延時,這個時候我們就用到了延遲觸發器鏈。下面就來記錄一下吧。

一、多級延遲觸發器(或延遲觸發器鏈)

(1)多級延遲觸發器電路

多級延遲觸發器,顧明思議就是多個觸發器串在一起,對信號進行打拍,一個觸發器就延時了一拍,也就是延遲了一個時鐘周期。

多級觸發器的代碼如下所示:

1 module DFF_N #(parameter N=3)( 2 input clk, 3 input reset, 4 input [N-1:0] D,5 output reg [N-1:0] Q 6 ); 7 reg [N-1:0]d0; 8 reg [N-1:0]d1; 9 always@(posedge clk or negedge reset) 10 if(!reset)begin 11 d0 <= 0; //同步清 0,低電平有效 12 d1 <= 0; //同步清 0,低電平有效 13 Q <= 0; //同步清 0,低電平有效 14 end 15 else begin 16 d0 <= D; 17 d1 <= d0; 18 Q <= d1;19 end 20 21 endmodule

d0 是 D 的延遲一級采樣或者稱為 D 的延遲一拍信號,同樣 d1 是 D 的延遲兩拍信號,而 Q 則是 延遲三拍信號。一方面可以通過修改N來改變對多少位的信號的進行延時;另一方面,可以用通過修改部分代碼,添加或者減少延遲計數。

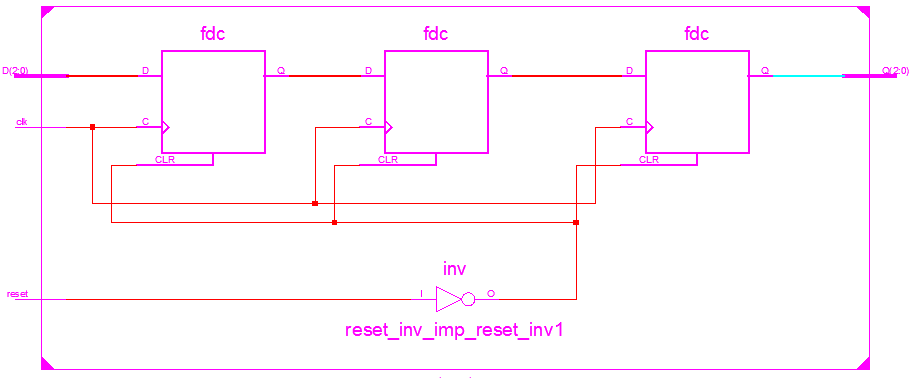

代碼綜合得到的電路(綜合之後)如下所示:

電路中顯示出三級延時,可以延時三個時鐘節拍(也就是三個時鐘周期),需要說明的是,上述每一級觸發器都包含了3個觸發器(對三位數據總線進行延時)。

(2)多級延遲觸發器的主要用法

①簡單的延時

多級延遲觸發器最原始的作用單純的對 D 信號做延遲操作,這裏就不進行詳述。

②降低亞穩態往後級傳輸的概率

如果 D 信號相對 clk 屬於不穩定信號,則 Q 和 d1 輸出相對 clk 屬 於穩定信號,這樣就有效地降低了亞穩態往後級傳輸的概率,多級延時觸發器鏈有時也稱為同步器。有關多級觸發器在降級亞穩態傳輸概率的內容,請查看我的另一篇博文:http://www.cnblogs.com/IClearner/p/6485389.html 。

③用來邊沿檢測

可以通過 d1 和 Q 信號獲取 D 信號的上升沿或者下降沿,具體介紹如下第二大點所示。

二、邊沿檢測電路

邊沿檢測的電路如下所示:

代碼如下所示:

綜合得到的電路如下所示:

從延遲觸發器鏈到邊沿檢測