數字邏輯設計基礎-事件/邊沿檢測

阿新 • • 發佈:2018-11-08

在數字邏輯設計中常常需要在邊沿或者訊號發生變化的時候做出相應的動作,因此,邊沿檢測就和重要。在其中(如果訊號來自於同一個時鐘域,那就不需要進行同步化處理,如果訊號來自於不同的時鐘域,就要就行同步化處理之後再進行檢測)。邊沿檢測主要分為:

(1):上升沿檢測

(2):下降沿就檢測

(3):上升/下降沿(雙邊)檢測

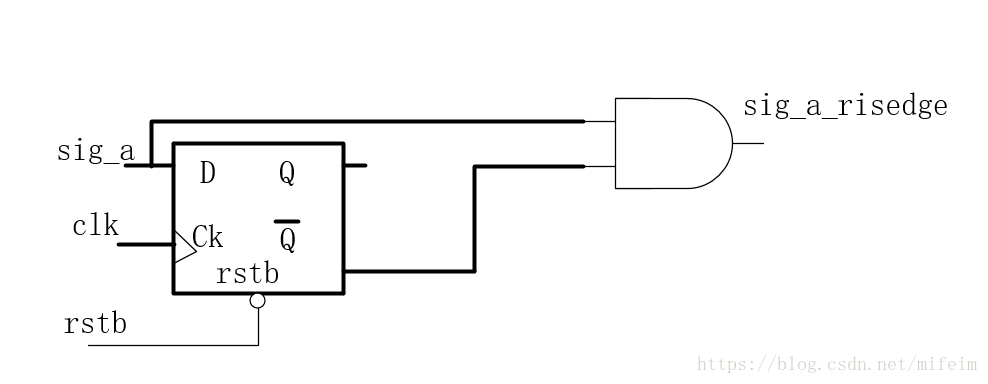

一:同步上升沿檢測

程式碼示例:

input sig_a; reg sig_a_d1; wire sig_a_risedge; [email protected](posedge clk or negedge rstb) begin if(!rstb) sig_a_d1 <= 1'b0; else sig_a_d1 <= sig_a; end assign sig_a_risedge = sig_a&!sig_a_d1;

邏輯結構圖:

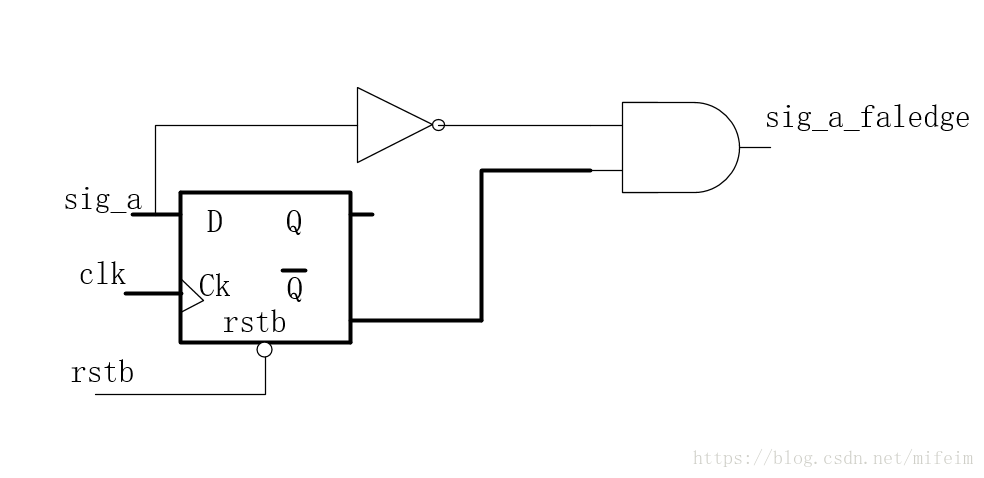

二:同步下降沿檢測

程式碼示例:

input sig_a;

reg sig_a_d1;

wire sig_a_faledge;

[email protected](posedge clk or negedge rstb) begin

if(!rstb)

sig_a_d1 <= 1'b0;

else

sig_a_d1 <= sig_a;

end

assign sig_a_faledge = !sig_a&sig_a_d1;邏輯結構圖

三:同步上升/下降沿檢測

程式碼示例:

input sig_a;

reg sig_a_d1;

wire sig_a_anyedge;