Xilinx DCM(Virtex-5)

1. 概述

Virtex-5 FPGA中的數字時鐘管理器(Digital Clock Managers,DCM)提供了廣泛而又強大時鐘管理功能,如時鐘偏移校正(Clock Deskew)、頻率合成(Frequency Synthesis)、相移(Phase Shifting)、動態重配置(Dynamic Reconfiguration)。

1.1 時鐘偏移校正

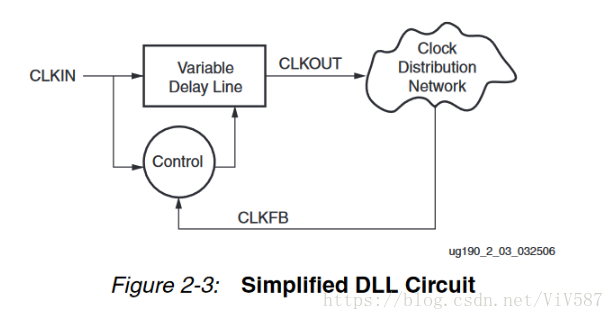

DCM包含一個延遲鎖定環(DLL),通過與輸入時鐘比較來校正DCM的輸出時鐘偏移以完全消除時鐘分配延遲。DLL包含延遲元件(單個小緩衝區)和控制邏輯,輸入時鐘驅動一系列延遲元件,因此每個延遲元件的輸出為輸入時鐘不同延遲的版本。

控制邏輯包含相位檢測器和延遲線選擇器,相位檢測器將輸入時鐘訊號(CLKIN)與反饋輸入(CLKFB)進行比較,並控制延遲線選擇器。本質上是將延遲新增到DCM的輸出,直到CLKIN和CLKFB重合為止。

1.2 頻率合成

單獨的二倍頻(CLK2X、CLK2X180)。

指定倍數的分頻(CLKDV)。

同時倍頻和分頻(CLKFX、CLKFX180)。

1.3 相移

DCM提供粗粒度相移和細粒度相移。粗粒度相移為:CLK0、CLK90、CLK180、CLK270、CLK2X、CLK2X180、CLKFX、CLKFX180。細粒度相移有四種模式:fixed、variable-positive、variable-center和direct模式。細粒度相移在粗粒度相移的基礎上相對於CLKIN進行相移。fixed模式在配置期間定義固定的相移有效輸入時鐘週期/256的倍數,variable-positive和variable-center模式中,相位可以在初始相移的基礎上動態地重複地向前或向後相移有效輸入時鐘週期/256,direct模式在零相移的基礎上動態地重複地向前或向後相移DCM_TAP。

1.4 動態重配置

詳見Virtex-5 FPGA Configuration Guide。

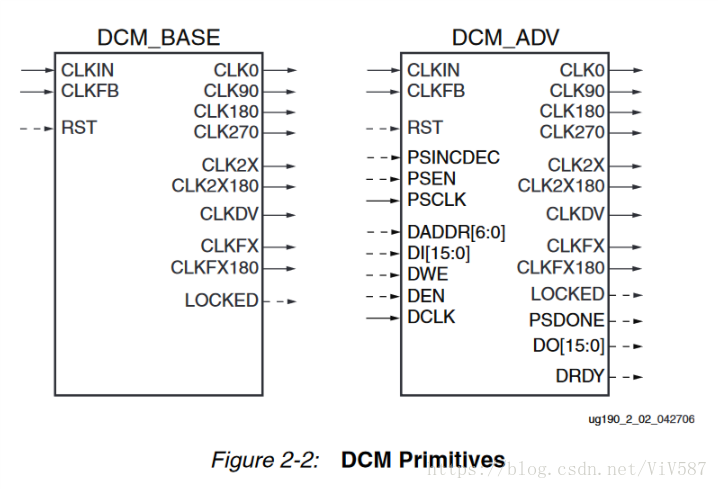

2. DCM原語

DCM原語DCM_BASE和DCM_ADV如下圖:

DCM_BASE原語:DCM_BASE具有時鐘偏移校正、頻率合成、固定相移等功能。

DCM_ADV原語:DCM_ADV具有時鐘偏移校正、頻率合成、固定或可變相移、動態重配置等功能。

3. DCM埠

DCM埠分為四類:DCM時鐘輸入埠、DCM控制和資料輸入埠、DCM時鐘輸出埠、DCM狀態和資料輸出埠。

3.1 DCM時鐘輸入埠

3.1.1 原時鐘輸入-CLKIN

源時鐘輸入引腳(CLKIN)為DCM提供源時鐘,它必須在指定的範圍之內,詳見Virtex-5 FPGA Data Sheet

IBUFG(全域性時鐘輸入緩衝器):當CLKFB連線,且IBUFG與DCM位於裝置的同一半時(即頂部或底部),DCM將補償時鐘輸入路徑。

BUFGCTRL(內部全域性時鐘緩衝器):任何BUFGCTRL都可以使用專用的全域性路由驅動Virtex-5器件中的任何DCM。串聯兩個DCM時,BUFGCTRL可以驅動DCM CLKIN引腳。

PLL(鎖相環):同一個CMT內,PLL可以直接驅動DCM的CLKIN引腳,中間不需要全域性時鐘緩衝器。

IBUF(輸入緩衝器):當IBUF驅動CLKIN輸入時,PAD到DCM的輸入偏移不會得到補償。

3.1.2 反饋時鐘輸入-CLKFB

反饋時鐘輸入向DCM提供反饋訊號,以此來對輸出時鐘進行延遲補償,使其與輸入時鐘對齊。要向DCM提供必要的反饋,需將DCM輸出CLK0連線到CLKFB。當CLKFB引腳連線時,所有的輸出時鐘都將相對於CLKIN進行偏移校正;當CLKFB未連線時,輸出時鐘不會進行偏移校正,但輸出時鐘之間會保持相應的相位關係。

對於內部反饋配置,DCM的輸出CLK0連線到同一半(同一頂部或底部)的全域性時鐘緩衝器,全域性時鐘緩衝器輸出再連線到自身的CLKFB輸入。

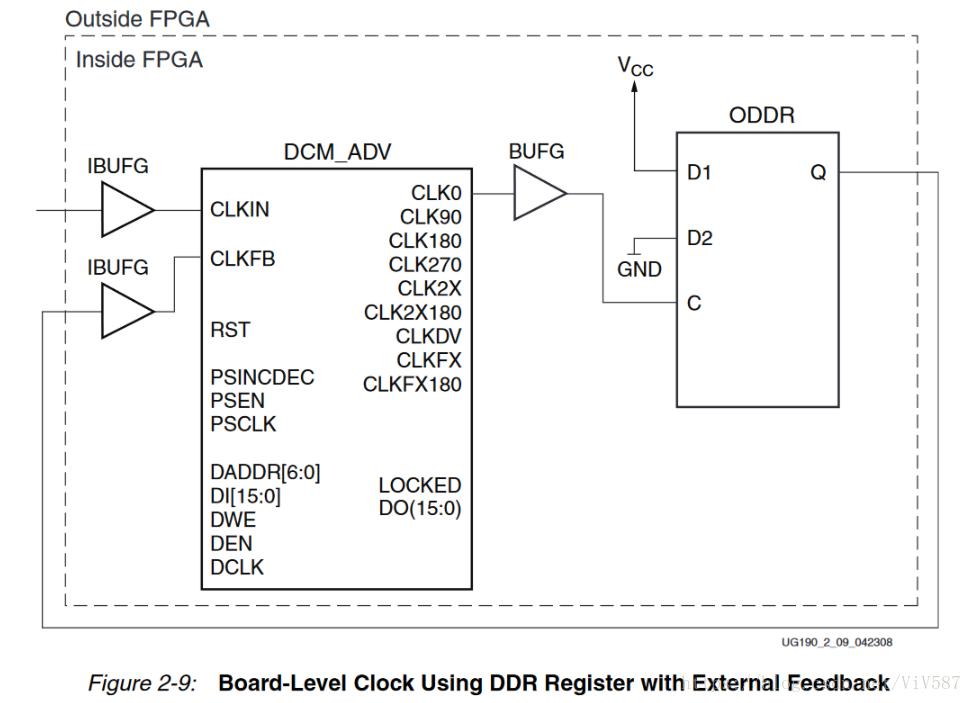

對於外部反饋配置,需要遵循如下規則:

1、要轉發時鐘,DCM的輸出CLK0必須直接驅動OBUF或BUFG-to-DDR。

2、在FPGA外部,轉發的時鐘必須連線到IBUFG(全域性時鐘引腳)或者IBUF來驅動DCM的CLKFB引腳。CLK和CLKFB應具有相同的I / O緩衝。

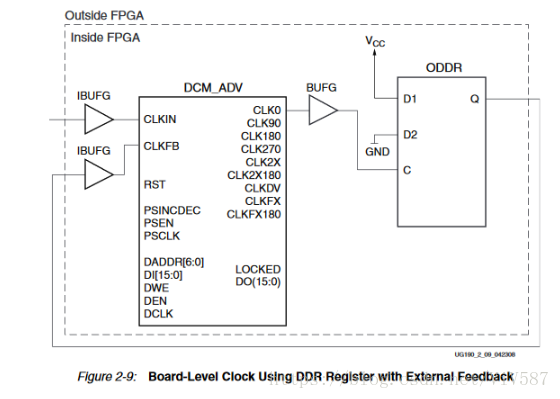

下圖展示了外部反饋配置:

反饋時鐘輸入訊號可以來自以下緩衝器之一:

IBUFG(全域性時鐘輸入緩衝器):這是外部反饋配置的首選來源。當IBUFG在DCM的同一頂部或底部時,PAD到DCM偏斜將被補償以進行偏移校正。

BUFGCTRL(內部全域性時鐘緩衝器):這是由CLK0驅動的內部反饋配置。

IBUF(輸入緩衝器):這是外部反饋配置。PAD到DCM的偏斜不會得到補償,無法保證其效能。

3.1.3 相移時鐘輸入-PSCLK

相移時鐘輸入引腳(PSCLK)為DCM相移提供源時鐘,PSCLK可以與CLKIN非同步(相位和頻率)。相移時鐘訊號可由以下時鐘源(內部或外部)驅動:

IBUF:輸入緩衝器。

IBUFG:全域性時鐘輸入緩衝器,只有與DCM相同一半(頂部或底部)上的IBUFG用於驅動DCM的PSCLK輸入才能使用專用路由。

BUFGCTRL:內部全域性時鐘緩衝器。

內部時鐘:使用通用路由的任何內部時鐘。

PSCLK的頻率範圍詳見Virtex-5 FPGA Data Sheet。當CLKOUT_PHASE_SHIFT屬性設定為NONE或FIXED時,此輸入必須接地。

3.1.4 動態重配置時鐘輸入-DCLK

動態重配置時鐘輸入引腳(DCLK)為DCM的動態重配置電路提供源時鐘, DCLK可以與CLKIN非同步(相位和頻率)。 動態重配置時鐘訊號可由以下時鐘源(內部或外部)驅動:

IBUF:輸入緩衝器。

IBUFG:全域性時鐘輸入緩衝器。

BUFGCTRL:內部全域性時鐘緩衝器。

內部時鐘:使用通用路由的任何內部時鐘。

DCLK的頻率範圍詳見Virtex-5 FPGA Data Sheet。不使用動態重配置時,此輸入必須接地。

3.2 DCM控制和資料輸入埠

3.2.1 復位輸入-RST

復位輸入引腳(RST)復位DCM電路,該復位為高有效非同步復位。非同步置位RST,經過傳播延時之後,強制所有DCM輸出為低電平,包括LOCKED訊號、所有狀態訊號和所有輸出時鐘。當RST被置為時,時鐘的最後一個週期會表現出短脈衝和嚴重的佔空比失真,或者彼此之間不再進行偏移校正。取消RST訊號的下一個週期開始鎖定過程。

為確保正確的DCM復位和鎖定過程,必須保持RST訊號,直到CLKIN訊號出現並穩定至少三個CLKIN週期。(即在CLKIN出現並穩定三個週期之前,DCM需保持在復位狀態,這樣才能確保正確的DCM復位和鎖定過程)

復位後DCM鎖定所需的時間在Virtex-5 FPGA Data Sheet中由LOCK_DLL(用於DLL輸出)和LOCK_FX(用於DFS輸出)指定,頻率越高鎖定越快。在CLKIN穩定之前,DCM必須保持復位狀態。

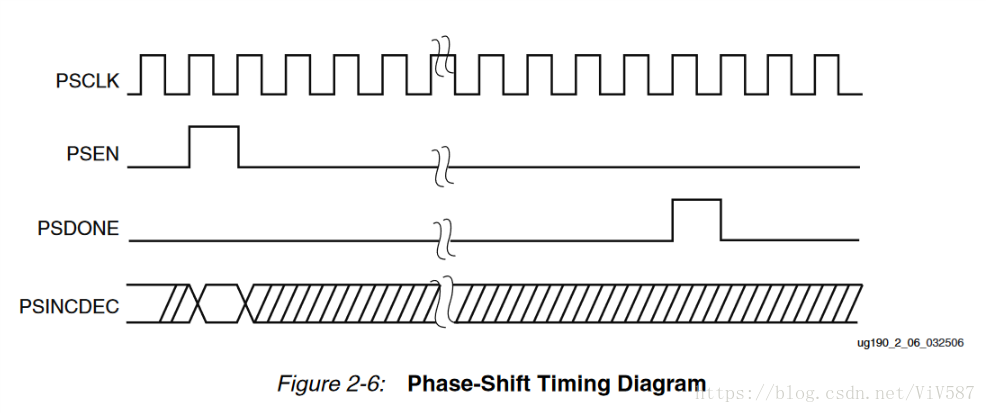

3.2.2 相移增量/減量輸入-PSINCDEC

當PSEN被啟用時,PSINCDEC輸入訊號用於遞增或遞減相移因子,它必須與PSCLK同步。PSINCDEC訊號置為高電平表示遞增,置為低電平表示遞減,將導致輸出時鐘被移位。當CLKOUT_PHASE_SHIFT屬性設定為NONE或FIXED時,此輸入必須接地。

用於VARIABLE_POSITIVE、VARIABLE_CENTER、DIRECT三種相移模式。

3.2.3 相移使能輸入-PSEN

PSEN輸入訊號啟動可變相移操作,它必須與PSCLK同步,且必須在PSCLK的一個週期內啟用。PSEN啟動後,DCM輸出時鐘從其原始相移逐位移動到目標相移,PSDONE高脈衝指示相移完成。在相變期間,任何輸出都沒有零星的變化或毛刺。當CLKOUT_PHASE_SHIFT屬性設定為NONE或FIXED時,PSEN必須接地。時序如下圖:

3.2.4 動態重配置資料輸入-DI[15:0]

動態重配置資料輸入匯流排(DI)為動態重配置提供重配置資料。不使用時,必須為所有位分配零。

3.2.5 動態重配置地址輸入-DADDR[6:0]

動態重配置地址輸入匯流排(DADDR)為動態重配置提供重配置地址。不使用時,必須為所有位分配零。

3.2.6 動態重配置寫使能輸入-DWE

動態重配置寫使能輸入引腳(DWE)提供寫使能控制訊號,以將DI資料寫入DADDR地址。 不使用時,必須綁低。

3.2.7 動態重配置啟用輸入-DEN

動態重配置使能輸入引腳(DEN)提供使能控制訊號以訪問動態重配置功能。 如果未使用動態重配置功能,則必須將DEN繫結為低電平。 當DEN接低電平時,DO反映DCM狀態訊號。

3.3 DCM時鐘輸出埠

DCM提供9個具有特定頻率和相位關係的時鐘輸出。當CLKFB連線時,所有DCM時鐘輸出與CLKIN具有固定的相位關係,未連線CLKFB時,DCM輸出與CLKIN不是相位對齊的,但是,所有輸出時鐘之間具有固定的相位關係。

3.3.1 1x輸出時鐘-CLK0

CLK0輸出時鐘的時鐘頻率與DCM的有效CLKIN頻率相同。 預設情況下,有效輸入時鐘頻率等於CLKIN頻率,CLKIN_DIVIDE_BY_2屬性設定為TRUE時,有效CLKIN頻率為實際CLKIN頻率的1/2。當CLKFB連線時,CLK0與CLKIN相位對齊。

3.3.2 1x輸出時鐘,90°相移-CLK90

CLK90輸出時鐘為CLK0相移90°。

3.3.3 1x輸出時鐘,180°相移-CLK180

CLK90輸出時鐘為CLK0相移180°。

3.3.4 1x輸出時鐘,270°相移-CLK270

CLK90輸出時鐘為CLK0相移270°。

3.3.5 2x輸出時鐘-CLK2X

CLK2X輸出時鐘與CLK0相位對齊,頻率為CLK0頻率的兩倍,並具有自動50/50佔空比校正。 在DCM鎖定之前,CLK2X輸出為輸入時鐘的1x版本,佔空比為25/75。 此行為(1x版本,佔空比25/75)允許DCM鎖定相對於源時鐘的正確邊沿。

3.3.6 2x輸出時鐘,180°相移-CLK2X180

CLK2X180輸出時鐘為CLK2X相移180°。

3.3.7 分頻輸出時鐘-CLKDV

CLKDV輸出時鐘與CLK0相位對齊,頻率是有效CLKIN頻率的分頻,分頻倍數由CLKDV_DIVIDE屬性確定。

3.3.8 頻率合成輸出時鐘-CLKFX

CLKFX輸出時鐘頻率:CLKFX frequency = (M / D) X effective CLKIN frequency

其中,M值由CLKFX_MULTIPLY屬性定義,D值由CLKFX_DIVIDE屬性定義。 M和D的範圍以及頻率合成器的輸入和輸出頻率範圍詳見Virtex-5 FPGA Data Sheet。

CLKFX輸出的上升沿與CLK0,CLK2X和CLKDV的上升沿對齊,當M和D沒有共同因子時,對齊僅在CLK0的每D個週期發生一次。

3.3.8 頻率合成輸出時鐘,180°相移-CLKFX180

CLKFX180輸出時鐘為CLKFX相移180°。

3.4 DCM狀態和資料輸出埠

3.4.1 鎖定輸出-LOCKED

LOCKED輸出指示DCM時鐘輸出是否有效。復位後,DCM取樣數千個時鐘週期以實現鎖定,DCM鎖定後,LOCKED訊號被置為高電平。鎖定時間的估算詳見Virtex-5 FPGA Data Sheet。

為了在啟動週期結束時保證建立的系統時鐘,DCM可以延遲完成裝置配置過程,直到DCM鎖定為止。STARTUP_WAIT屬性啟用此功能。

在LOCKED訊號置為高電平之前,DCM輸出時鐘無效,並且可能出現毛刺、尖峰或其他虛假運動。並且,CLK2X輸出顯示為1x時鐘,佔空比為25/75。

3.4.2 相移完成輸出-PSDONE

相移完成輸出訊號(PSDONE)與PSCLK同步,在所請求的相移完成時,PSDONE在PSCLK的一個週期內脈衝為高電平。 該訊號還表明可以發起新的相移。 如果未使用相移功能或處於固定模式,則PSDONE輸出訊號無效。

3.4.3 狀態或動態重配置資料輸出-DO[15:0]

使用動態重配置時,DO輸出匯流排提供DCM狀態或資料輸出。如果未使用動態重新配置埠,強烈建議使用DCM_BASE而不是DCM_ADV。

DO[0]:相移溢位。當DCM相移超過允許的相移值時,或超過相移延遲線的絕對延遲範圍時,DO[0]置位。如果未使用相移功能(CLKOUT_PHASE_SHIFT = NONE),DO[0]將置為0。

DO[1]:CLKIN停止。當輸入時鐘停止時置位(CLKIN在一個或多個時鐘週期內保持高電平或低電平)。當CLKIN停止時,DO[1]將在9個CLKIN週期之內被置位(即第10個週期來臨之前DO[1]已經置位),當CLKIN重新啟動時,CLK0開始翻轉,DO[1]將在9個週期之內建為無效。

DO[2]:CLKFX停止。當CLKFX停止時置位。DO[2]在CLKFX停止後的260個週期之內建位。在DCM復位前,CLKFX不會恢復,DO[2]也不會置為無效。 如果未使用CLKFX / CLKFX180輸出,則DO[2]置為無效。

DO[3]:CLKFB停止。當反饋時鐘停止時置位(CLKFB在一個或多個時鐘週期內保持高電平或低電平)。當CLKFB停止時,DO[3]在6個CLKIN週期之內被置位,當CLKFB重新啟動時,DO[3]將在6個CLKIN週期之內建為無效。

CLKFB偶爾跳過不會影響DCM操作,但是,CLKFB長時間停止可能會導致DCM丟失LOCKED。 當LOCKED丟失時,需要重置DCM以恢復操作。當未使用DCM的DLL部分時(例如,僅使用CLKFX輸出時),CLKFB可以保持未連線狀態。在這種情況下,DO[3]被置為無效。

DO[15:4]:保留。

當LOCKED為低電平時(復位或鎖定過程),所有狀態訊號都置為低電平。

3.4.4 動態重配置就緒輸出-DRDY

動態重配置就緒輸出引腳(DRDY)為DCM的動態重配置功能的DEN訊號提供響應。

4. DCM屬性

4.1 CLKDV_DIVIDE屬性

CLKDV_DIVIDE屬性控制CLKDV的頻率。

CLKDV_DIVIDE的可能值為:1.5,2,2.5,3,3.5,4,4.5,5,5.5,6,6.5,7,7.5,8,9,10,11,12,13,14,15,16,預設值為2。

在低頻模式下,任何CLKDV_DIVIDE值都會產生具有50/50佔空比的CLKDV輸出。

在高頻模式下,將CLKDV_DIVIDE值設為整數值才能產生具有50/50佔空比的CLKDV輸出,若設為非整數值,則佔空比如下:

1.5-->1/3;2.5-->2/5;3.5-->3/7;4.5-->4/9;5.5-->5/11;6.5-->6/13;7.5-->7/15。

4.2 CLKFX_MULTIPLY屬性和CLKFX_DIVIDE屬性

CLKFX_MULTIPLY屬性和CLKFX_DIVIDE屬性控制CLKFX的頻率。

M的可能值為2到33之間的任何整數,D的可能值為1到32之間的任何整數,預設設定為M = 4和D = 1。

4.3 CLKIN_PERIOD屬性

CLKIN_PERIOD屬性指定源時鐘週期(單位ns), 預設值為0.0 ns。

可以幫助DCM調整最佳CLKFX / CLKFX180輸出。

4.4 CLKIN_DIVIDE_BY_2屬性

CLKIN_DIVIDE_BY_2屬性用於在DCM的輸入時鐘路徑中啟用觸發器。

CLKIN_DIVIDE_BY_2的可能值為TRUE和FALSE, 預設值為FALSE。

CLKIN_DIVIDE_BY_2設為FALSE時,DCM的有效CLKIN頻率等於驅動CLKIN輸入端源時鐘的頻率;設為TRUE時,DCM的有效CLKIN頻率等於驅動CLKIN輸入端源時鐘頻率的一半。

可以使高頻輸入時鐘滿足DCM輸入時鐘頻率要求。

4.5 CLKOUT_PHASE_SHIFT屬性

CLKOUT_PHASE_SHIFT屬性指示DCM的相移模式。

CLKOUT_PHASE_SHIFT的可能值為NONE、FIXED、VARIABLE_POSITIVE、VARIABLE_CENTER、DIRECT,預設值為NONE。

NONE:不能執行相移,相移值對DCM輸出沒有影響。

FIXED:DCM對CLKIN進行固定相位的相移,相移值由PHASE_SHIFT屬性確定。

(CLKOUT_PHASE_SHIFT屬性設為FIXED或NONE時,PSEN、PSINCDEC、PSCLK輸入必須接地。)

VARIABLE_POSITIVE:DCM輸出在可變模式下相對於CLKIN的正範圍內進行相移。

VARIABLE_CENTER:DCM輸出在可變模式下相對於CLKIN的正範圍和負範圍內進行相移。

(CLKOUT_PHASE_SHIFT屬性設為VARIABLE_POSITIVE或VARIABLE_CENTER時,每個相移增量(或減量)將增加(或減少)相位移動1/256 x CLKIN週期,即相移單位為1/256xCLKIN週期。)

DIRECT:DCM輸出在可變模式下相對於CLKIN的正範圍內進行相移。每個相移增量/減量將增加/減少相位移動一個DCM_TAP。DCM_TAP詳見Virtex-5 FPGA Data Sheet。

VARIABLE_POSITIVE和VARIABLE_CENTER模式的初始相移由PHASE_SHIFT屬性值決定的,而DIRECT模式中的初始相移始終為零,當使用DIRECT模式時,PHASE_SHIFT屬性應設為零。也可以使用Virtex-5 FPGA Configuration Guide中的動態重配置埠將DIRECT模式的非零初始相移值載入到DCM。

4.6 CLK_FEEDBACK屬性

CLK_FEEDBACK屬性確定CLKFB的反饋型別。

CLK_FEEDBACK的可能值為1X或NONE,預設值為1X。

CLK_FEEDBACK設為1X時,CLKFB引腳必須由CLK0驅動;設為NONE時,CLKFB引腳保持未連線狀態。

4.7 DESKEW_ADJUST屬性

DESKEW_ADJUST屬性會影響反饋路徑中的延遲量。

DESKEW_ADJUST的可能值為

SYSTEM_SYNCHRONOUS、SOURCE_SYNCHRONOUS、0,1,2,...,31,預設值為SYSTEM_SYNCHRONOUS。

對於大多數設計,預設值是合適的。 在源同步設計中,將此屬性設為SOURCE_SYNCHRONOUS。 其餘值應在諮詢Xilinx後使用。

4.8 DFS_FREQUENCY_MODE屬性

DFS_FREQUENCY_MODE屬性指定數字頻率合成器(DFS)的頻率模式。

DFS_FREQUENCY_MODE的可能值為Low 或 High,預設值為Low。

兩種模式的頻率範圍詳見Virtex-5 FPGA Data Sheet。 DFS_FREQUENCY_MODE確定CLKIN,CLKFX和CLKFX180的頻率範圍。

4.9 DLL_FREQUENCY_MODE屬性

DLL_FREQUENCY_MODE屬性指定延遲鎖定環(DLL)的頻率模式。

DLL_FREQUENCY_MODE的可能值為Low 或 High,預設值為Low。

兩種模式的頻率範圍詳見Virtex-5 FPGA Data Sheet。

4.10 DUTY_CYCLE_CORRECTION屬性

DUTY_CYCLE_CORRECTION屬性控制1x時鐘輸出(CLK0,CLK90,CLK180和CLK270)的佔空比校正。

DUTY_CYCLE_CORRECTION的可能值為TRUE和FALSE,預設值是TRUE。

設定為TRUE時,1x時鐘輸出的佔空比校正到指定的限制範圍內,詳見Virtex-5 FPGA Data Sheet。強烈建議將DUTY_CYCLE_CORRECTION屬性設定為TRUE,將此屬性設定為FALSE不一定會產生與源時鐘具有相同佔空比的輸出時鐘。

4.11 DCM_PERFORMANCE_MODE屬性

DCM_PERFORMANCE_MODE屬性為高頻低抖動或低頻寬相移優化DCM。

DCM_PERFORMANCE_MODE的可能值為MAX_SPEED和MAX_RANGE,預設值為MAX_SPEED。

DCM_PERFORMANCE_MODE設為MAX_SPEED時,DCM為產生低抖動高頻時鐘優化,但是相移範圍比設為MAX_RANGE時小。

DCM_PERFORMANCE_MODE設為MAX_RANGE時,DCM為產生低頻寬範圍相移時鐘優化。

DCM_PERFORMANCE_MODE會影響以下值:

DCM輸入和輸出頻率範圍,相移範圍,輸出抖動,DCM_TAP,CLKIN_CLKFB_PHASE,CLKOUT_PHASE和佔空比精度,詳見Virtex-5 FPGA Data Sheet。

大多數情況下,DCM_PERFORMANCE_MODE應設為MAX_SPEED,當頻率需低於MAX_SPEED設定的低頻限制或需要更大的絕對相移範圍時,設為MAX_RANGE。

4.12 Factory_JF屬性

Factory_JF屬性會影響DCM的抖動濾波器特性。

Factory_JF的預設值為0xF0F0。

4.13 PHASE_SHIFT屬性

PHASE_SHIFT屬性確定DCM輸出的相移量,可用於固定或可變相移模式,如果用於可變相移模式,則為初始相移量。

當CLKOUT_PHASE_SHIFT = VARIABLE_POSITIVE時,PHASE_SHIFT值範圍為0到255。當CLKOUT_PHASE_SHIFT = VARIABLE_CENTER或FIXED時,PHASE_SHIFT值範圍為-255到255。當CLKOUT_PHASE_SHIFT = DIRECT時,PHASE_SHIFT值範圍為0到1023。預設值為0。

4.14 STARTUP_WAIT屬性

STARTUP_WAIT屬性確定DCM是否等待DCM鎖定,等待時間為一個啟動週期。

STARTUP_WAIT的可能值為TRUE和FALSE,預設值為FALSE。

當STARTUP_WAIT設定為TRUE且使用LCK_cycle BitGen選項時,配置啟動序列將在LCK_cycle指定的啟動週期中等待,直到DCM被鎖定。

5. DCM設計指南

5.1 時鐘偏移校正

Virtex-5 FPGA DCM具有全數字、專用、片上時鐘偏移校正功能,偏移校正能夠提供原時鐘和輸出時鐘之間的零傳播延遲、輸出時鐘(分佈在整個器件中)之間的低時鐘偏斜、高階時鐘域控制。偏移校正功能還可用作為多個器件提供服務的板級時鐘的時鐘映象,這是通過將CLK0輸出到電路板(以及電路板上的其他器件),然後將時鐘作為反饋時鐘來實現的。利用偏移校正功能極大地簡化並改進了涉及高扇出,高效能時鐘的系統級設計。

5.1.1 時鐘偏移校正操作

時鐘偏移校正功能使用的是DCM中的DLL電路,簡化的DLL是由單個可變延遲線和控制邏輯組成(如下圖),可變延遲線包含單獨的小延遲原件或緩衝器,每個固有延遲元件的大小為DCM_TAP。輸入時鐘驅動延遲線,延遲線的每個延遲元件的輸出為輸入時鐘(CLKIN)不同點的延遲版本。控制邏輯包含相位檢測器和延遲線選擇器,相位檢測器將輸入時鐘訊號(CLKIN)與反饋輸入(CLKFB)進行比較,並控制延遲線選擇器,實質上等同於為DCM輸出增加延遲,直到CLKIN和CLKFB重合,此時兩個時鐘相位相差360°,因而同相,當輸入時鐘邊沿與反饋時鐘邊沿對齊時,DCM實現鎖定。時鐘分配網路將時鐘路由到所有時鐘輸出和時鐘反饋CLKFB引腳,DCM輸出時鐘補償時鐘分配網路中的延遲,有效地消除源時鐘與其負載之間的延遲。

為了提供正確的時鐘偏移校正,DCM取決於時鐘源和反饋輸入使用的專用路由和資源。 附加的延遲元件(Deskew Adjust)可用於補償時鐘源或反饋路徑。 Xilinx ISE工具分析DCM周圍的佈線,以確定是否必須插入延遲來補償時鐘源或反饋路徑, 因此,需要使用專用路由來實現可預測的偏移校正。

5.1.2 輸入時鐘要求

DCM的時鐘輸入可以由IBUFG / IBUFGDS,IBUF,BUFGMUX或BUFGCTRL驅動。由於IBUF和DCM時鐘輸入之間沒有專用路由,因此使用IBUF會導致無法補償的額外輸入延遲,並且無法保證效能。

DCM的輸出時鐘訊號本質上是輸入時鐘的延遲,輸入時鐘上的任何不穩定性都將反映在輸出時鐘上。DCM輸入時鐘的要求詳見Virtex-5 FPGA Data Shee。一旦鎖定,DCM可以容忍輸入時鐘週期的變化,變化值最高可達CLKIN_PER_JITT_DLL_HF(高頻情況下)或CLKIN_PER_JITT_DLL_LF(低頻情況下)指定的值。較大的抖動(週期變化)可能導致DCM失鎖,由LOCKED輸出無效指示,失鎖後,使用者必須重置DCM。輸入週期差抖動率必須保持低於低頻的CLKIN_CYC_JITT_DLL_LF和高頻的CLKIN_CYC_JITT_DLL_HF

5.1.3 輸入時鐘變化

輸入時鐘週期的變化超過最大輸入週期抖動規定時需要手動復位DCM,未重置DCM會產生不可靠的LOCKED訊號和輸出時鐘。

只要不使用CLKFX和CLKFX180,暫時停止輸入時鐘和反饋時鐘對偏移校正電路影響很小。若使用CLKFX和CLKFX180且輸入時鐘停止,CLKFX或CLKFX180可能會停止翻轉,並且DO[2]被置位,必須重置DCM才能恢復。在CLKFX停止後100μs,DO[2]置位,在DCM復位之前,CLKFX和DO[2]不會恢復。

在任何其他情況下,時鐘不應停止超過100毫秒,以儘量減少裝置冷卻的影響,否則,延時可能會改變。時鐘應在高電平或低電平處停止,並且使用相同頻率週期的輸入時鐘恢復,在此期間,以及時鐘恢復後,LOCKED保持高電平。因此,LOCKED高電平並不一定意味著有效時鐘可用。

當輸入時鐘停止(CLKIN在一個或多個時鐘週期內保持高電平或低電平)時,在重新整理延遲線時仍會產生一到九個輸出時鐘週期,當輸出時鐘停止時,DO[1]置位。當重新啟動時鐘時,在延遲線被填滿前,輸出時鐘不會產生,這裡有一到八個時鐘週期,通常是兩個或三個時鐘週期,一旦產生輸出時鐘,DO[1]置為0。CLKIN可以從前一個時鐘的任何相位處啟動,但如果頻率改變,則需要復位DCM。LOCKED為低電平或DCM處於鎖定過程中時,DO[1]強制保持為0。

5.1.4 輸出時鐘

DCM的九個時鐘輸出都可以驅動全域性時鐘網路,全域性時鐘分配網路可最大限度地減少因載入差異而導致的時鐘偏差。通過監視輸出時鐘(CLK0)的樣本,去歪斜電路補償路由網路上的延遲,有效地消除了從外部輸入埠到裝置內各個時鐘負載的延遲。

輸出引腳的連線有一些限制,DCM時鐘輸出必須驅動全域性時鐘緩衝器BUFGCTRL,DCM時鐘輸出無法驅動一般路由。DCM時鐘輸出必須驅動同一頂部或底部的BUFGCTRL才能使用專用路由。如果DCM和BUFGCTRL不在同一頂部或底部,則使用本地路由,但DCM可能無法正確校正偏移。在LOCKED訊號置位之前,DCM輸出時鐘無效。

5.1.5 配置和啟動期間的DCM

在FPGA配置期間,DCM處於復位狀態,並在啟動序列開始時鎖定。 當DCM開始鎖定時,DCM需要CLKIN和CLKFB輸入時鐘存在且穩定。 如果器件在沒有輸入時鐘或輸入時鐘不穩定的情況下進入配置啟動序列,則必須在配置穩定時鐘後復位DCM。

5.1.6 偏移校正調整

DESKEW_ADJUST屬性設定可配置的可變抽頭延遲元件的值,以控制新增到DCM反饋路徑的延遲量。如下圖:

該延遲元件允許調整時鐘源和CLK0之間的有效時鐘延遲,以保證器件中IOB輸入觸發器的非正保持時間。

向DCM反饋路徑新增更多延遲會減少從FPGA時鐘輸入引腳到任何觸發器的時鐘輸入的實際時鐘路徑的有效延遲。減小時鐘延遲會增加輸入觸發器中的建立時間,並減少所需的正保持時間。時鐘路徑延遲包括通過IBUFG,路由,DCM,BUFG和時鐘樹到目標觸發器的延遲。 如果反饋延遲等於時鐘路徑延遲,則有效時鐘路徑延遲為零。

系統同步設定:

預設情況下,反饋延遲設定為系統同步模式。系統同步系統的主要時序要求是非正保持時間(或最小正保持時間)和最小的時鐘輸出和建立時間。更快的時鐘輸出和建立時間允許使用更短的系統時鐘週期。理想情況下,DLL的目的是將時鐘延遲清零,以產生更快的時鐘輸出和非正保持時間。 DESKEW_ADJUST的系統同步設定(預設)配置反饋延遲元件,以保證所有輸入IOB暫存器的非正保持時間。 新增到反饋路徑的確切延遲數取決於裝置大小。在時序報告中,這包括作為TDCMINO引數表示的輸入時鐘路徑的時序減少。 如上圖所示,反饋路徑包括預設設定(紅線)中的抽頭延遲。

在某些情況下,DCM不會新增此額外反饋延遲,並且DESKEW_ADJUST引數無效。BitGen選擇適當的DCM Tap設定。 這些情況包括:

兩個或多個DCM級聯時的下游DCM;

具有外部反饋的DCM;

帶有外部CLKIN的DCM,它不是來自專用時鐘輸入引腳。

源同步設定:

當DESKEW_ADJUST設定為源同步模式時,DCM反饋延遲元素設定為零。如上圖所示,在源同步模式下,DCM時鐘反饋延遲元件設定為最小化取樣視窗。與系統同步模式相比,這導致更長的保持時間和更長的時鐘輸出。

5.1.7 偏移校正電路特性

通過新增一個時鐘週期延遲來消除時鐘分配延遲。

時鐘偏移校正到CLKOUT_PHASE內。

消除片上和片外時鐘延遲。

對反饋時鐘路徑的延遲沒有限制。

需要連續執行的輸入時鐘。

適應很大範圍的頻率。 但是,一旦鎖定某個頻率,就不能容忍大的輸入頻率變化。

不消除抖動。 偏移校正電路輸出抖動是由輸入抖動和偏移校正電路引起的抖動值的累積。

配置可在DCM鎖定以保證系統時鐘在啟動裝置之前建立之後完成。

5.2 頻率合成

CLK2X、CLK2X180:有效輸入頻率的兩倍。

CLKDV:頻率是有效CLKIN頻率的分頻,分頻倍數由CLKDV_DIVIDE屬性確定。

CLKFX、CLKFX180:CLKFX frequency = (M / D) X effective CLKIN frequency。

頻率合成輸出可以驅動全域性時鐘路由網路,良好的全球時鐘分配網路可最大限度地減少因距離或負載不同而造成的時鐘偏差。

5.2.1 頻率合成操作

僅當向DCM的CLKFB輸入提供反饋時,頻率合成器輸出相位與時鐘輸出CLK0對齊。

5.2.2 頻率合成特性

頻率合成器提供的輸出頻率等於輸入頻率乘以M併除以D.

輸出CLKFX和CLKFX180的佔空比始終為50/50。

較小的M和D值可實現更快的鎖定時間,將M和D除以最大公因子即可得到最小值。

當CLKFB連線時,則CLKFX在CLK0的每個D週期或CLKFX的每M個週期與CLK0相位對齊。

5.3 相移

DCM提供粗粒度和細粒度的相移。粗粒度相移為:CLK0、CLK90、CLK180、CLK270、CLK2X、CLK2X180、CLKFX、CLKFX180。粗略的相移時鐘由DLL電路的延遲線產生。當CLKFB未連線時,輸出時鐘之間的關係還會保留。

細粒度相移根據CLKOUT_PHASE_SHIFT和PHASE_SHIFT屬性對CLKIN進行相移,由於CLKIN作為參考時鐘,因此CLKFB需要連線,以將輸入時鐘與輸出相移時鐘進行比較。

5.3.1 相移操作

細粒度相移對所有9個輸出時鐘都有效,CLKIN和CLKFB上升沿之間的相移單位為輸入時鐘週期除以256或DCM_TAP。

相移範圍:

PHASE_SHIFT屬性值範圍和FINE_SHIFT_RANGE DCM引數影響了相移的範圍。

PHASE_SHIFT:

在FIXED、VARIABLE_POSITIVE、VARIABLE_CENTER相移模式下,相移量(初始相移量)如下公式計算:

在FIXED和VARIABLE_CENTER模式下,PHASE_SHIFT屬性值的範圍為-255~255,在VARIABLE_POSITIVE模式下,PHASE_SHIFT屬性值的範圍為0~255。

在DIRECT相移模式下,相移量(初始相移量)如下公式計算:

在DIRECT模式下,PHASE_SHIFT屬性值的範圍為0~1023。

FINE_SHIFT_RANGE:

FINE_SHIFT_RANGE表示相移延遲線可實現的總延遲,總延遲延遲抽頭數的函式。Absolute Range可在Virtex-5 FPGA Data Sheet中查詢,此處討論不同的Absolute Range。

Absolute Range (Fixed) = ± FINE_SHIFT_RANGE

Absolute Range (Variable-Center Mode) = ± FINE_SHIFT_RANGE / 2

Absolute Range (Variable-Positive and Direct Modes) = + FINE_SHIFT_RANGE

在可變模式和直接模式下,當PSEN輸入有效時,PHASE_SHIT值可以根據PSINCDEC動態遞增或遞減。

相移示例:

如果PERIODCLKIN = 2 x FINE_SHIFT_RANGE,PHASE_SHIFT值在Fixed模式下範圍為-128~128,在Variable-Positive模式下範圍為0~128,在Variable-Center模式下範圍為-64~64。

如果PERIODCLKIN <= FINE_SHIFT_RANGE,PHASE_SHIFT值在Fixed模式和Variable-Center模式下範圍為-255~255,在Variable-Positive模式下範圍為0~255。

在Direct模式下,PHASE_SHIFT值的範圍為0~1023。

可用粗粒度相移來擴充套件相移範圍,也可設定DCM_PERFORMANCE_MODE屬性值為MAX_RANGE來增加FINE_SHIFT_RANGE。

下圖基於FINE_SHIFT_RANGE=10ns。

在可變模式下,通過將PSEN啟用一個PSCLK週期來改變相移量,PSINCDEC將決定是增加相移還是減少相移,在偏移校正電路完成增加或減少的相移後,將PSDONE置位,表示允許下一次的相移改變。

除了Direct模式,其他相移模式對溫度、電壓適應,即溫度、電壓的改變不會改變相移量,而Direct模式直接控制DCM_TAP,因而溫度電壓比改變後,由於DCM_TAP改變,Direct模式相移量也會改變。

5.3.2 PSEN,PSINCDEC,PSCLK和PSDONE的相互作用

PSEN、PSINCDEC、PSCLK、PSDONE控制著Variable模式和Direct模式。PSEN,PSINCDEC和PSDONE與PSCLK同步,當PSEN被置位一個PSCLK時鐘週期時,啟動相移遞增/遞減,每次遞增或遞減將相移增加或減少CLKIN週期的1/256。PSEN必須在一整個PSCLK週期內有效,否則不保證能完成相移。當相移完成時,PSDONE在一個PSCLK週期內為高電平,完成相移操作所需的時間各不相同,因此,必須監視PSDONE的狀態。在置位PSEN和PSDONE輸出高電平之間,DCM輸出時鐘從其原始相移逐漸變為遞增/遞減後的相移。 PSDONE為高意味著一個相移遞增遞減操作完成,可以啟動下一個遞增/遞減操作。

DCM鎖定之後,VARIABLE_POSITIVE和VARIABLE_CENTER模式的初始相移由PHASE_SHIFT值決定,Direct模式的初始相移時鐘為0。DCM在初始相移的基礎上由PSEN、PSINCDEC、PSCLK、PSDONE控制進行相移遞增和遞減。下圖顯示了相移遞增遞減過程:

當相移計數器達到PHASE_SHIFT的最大值之後,PSEN被啟用,此時,在經過一段時間之後,PSDONE仍會輸出一個PSCLK週期的高電平,但是,由於相移溢位標誌置位,因而不會執行相移增加或減少。

5.3.3 相移溢位

相移溢位狀態訊號DO[0]在以下情況下會被置位:

DCM相移值超過了允許的PHASE_SHIFT值。

DCM相移值超過了相移延遲線的Absolute Range。

5.3.4 相移特性

細粒度相移調整的解析度為有效輸入時鐘週期的1/256,或者是一個DCM_TAP,相移可在使用者控制下動態改變。

相移對9個輸出時鐘都有效。

除了Direct模式,電壓和溫度不影響相移。

細粒度相移可由粗粒度相移擴充套件。

MAX_RANGE模式擴充套件了相移範圍。

DCM中的相移功能(DPS)需要CLKFB進行延遲調整,DPS功能的最小CLKIN頻率由DLL頻率模式決定。

5.4 動態重配置

動態重配置埠可以更新初始DCM設定,而無需將新的位元流檔案載入到FPGA中。動態重配置埠可動態調整CLKFX_MULTIPLY(M)和CLKFX_DIVIDE(D)值以產生新的CLKFX頻率。通過以下步驟來調整M和D的值:

將所需的M和D值減1。如果期望的M / D = 9/4,則載入M / D = 8/3。

保持DCM復位並在寫入新的M和D值後解除復位,在LOCKED再次置位後,便可以使用CLKFX輸出。

讀取DADDR0以恢復D0的預設狀態。

解除復位。

6. DCM與Virtex-5內部其他時鐘資源的連線

大多數DCM功能需要連線到專用時鐘資源,包括專用時鐘I / O(IBUFG)、時鐘緩衝器(BUFGCTRL)和PLL,這些時鐘資源位於Virtex-5器件的中間列。

6.1 IBUFG to DCM

Virtex-5器件包含20個時鐘輸入,通過例項化IBUFG可以訪問這些時鐘輸入。Virtex-5器件的頂部和底部各包含10個IBUFG,它們都可以驅動位於器件同一頂部或底部的DCM的時鐘輸入引腳(CLKIN,CLKFB,PSCLK或DCLK)。

6.2 DCM to BUFGCTRL

任何DCM時鐘輸出都可以驅動器件同一頂部或底部的任何BUFGCTRL輸入,且對同時使用DCM輸出數量沒有限制。

6.3 BUFGCTRL to DCM

任何BUFGCTRL都可以驅動Virtex-5器件中的任何DCM,但是由於一個時鐘域中僅存在最多十個專用時鐘路由資源,且BUFGCTRL輸出需要使用時鐘路由,因此間接限制了BUFGCTRL與DCM的連線。如果一個時鐘域中已經使用了十個BUFGCTRL輸出,那麼在這個時鐘域中不能再使用額外的BUFGCTRL,包括連線到DCM引腳的BUFGCTRL。

6.4 PLL To and From DCM

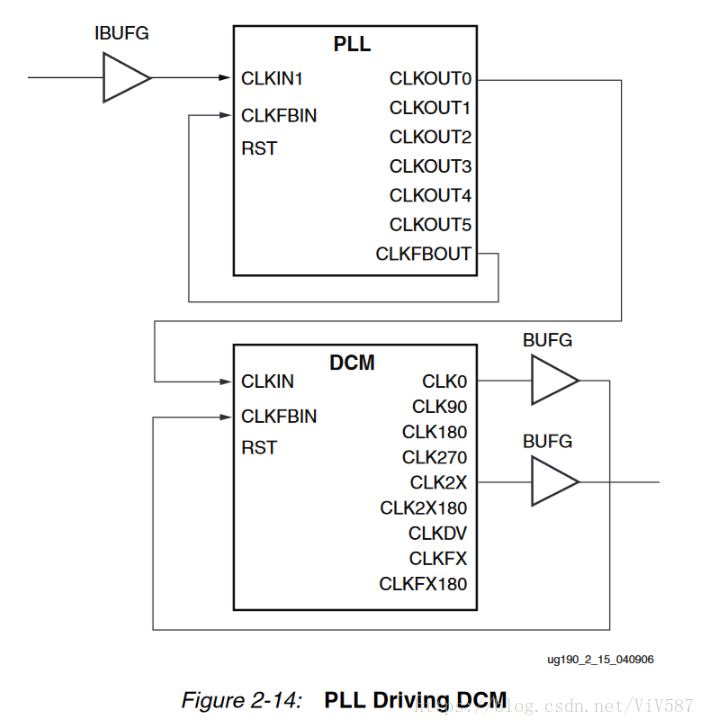

下圖總結了同一CMT模組中DCM和PLL之間的專用連線,PLL可以使用專用連線驅動同一CMT塊中的DCM,DCM也可以通過專用連線在同一CMT塊內驅動PLL,PLL和DCM之間不需要BUFGCTRL。

7. 應用例項

7.1 標準用法(Standard Usage)

下圖顯示了使用內部反饋實現的DCM_BASE,是DCM的最簡單用法。

7.2 板級時鐘生成(Board-Level Clock Generation)

下圖板級時鐘生成示例(外部反饋)說明了如何使用DCM為電路板上的其他元件生成輸出時鐘。本例使用DDR暫存器,其輸入連線到GND和VCC。由於DCM的輸出路由到BUFG,因此時鐘在到達輸出暫存器之前保持在全域性路由中,保證了時鐘的質量。

下圖板級時鐘生成示例(帶有內部反饋)說明了板上轉發時鐘的時鐘生成。

7.3 使用內部偏移校正的板級偏移校正(Board Deskew with Internal Deskew)

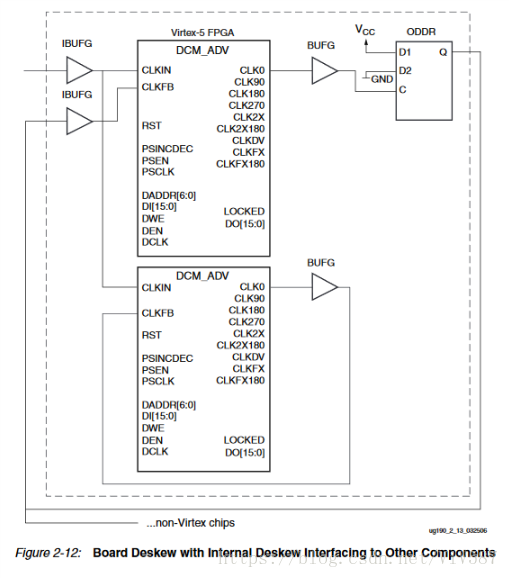

某些應用需要使用內部偏移校正的電路板偏移校正以與其他裝置連線,可以使用兩個或多個DCM來實現這些應用,下圖所示的電路可用於在同一系統中的多個Virtex器件之間校正系統時鐘。

下圖示例顯示了從Virtex-5 FPGA到Virtex FPGA以外的元件的介面。

7.4 兩個DCM時鐘切換(Clock Switching Between Two DCMs)

下圖說明了在兩個DCM之間切換時鐘,同時保持兩個DCM鎖定。

7.5 DCM和PLL(DCM with PLL)

源時鐘輸入DCM之前,可先驅動PLL以減少時鐘抖動,再由PLL驅動DCM。此設定可減少源時鐘抖動,同時允許使用者訪問所有可用的DCM時鐘輸出。下圖顯示了PLL使用專用路由資源(無BUFG)驅動同一CMT塊內的DCM。

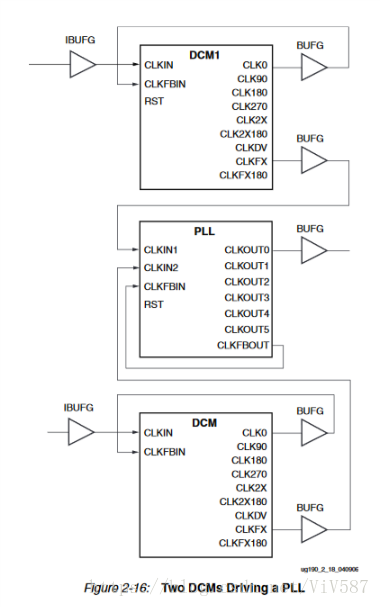

也可以使用DCM來驅動PLL,此設定可降低源時鐘和DCM時鐘輸出的總抖動。但在這種情況下,最多隻有兩個DCM輸出時鐘可以驅動PLL,因此,最多隻有兩個DCM時鐘可以訪問PLL,並從減少的抖動中受益。

下圖說明了CMT中DCM和PLL之間的直接連線,只有一個DCM輸出可以使用CMT內的專用連線驅動PLL,而無需使用BUFG。 DCM和PLL可以在相同或不同的CMT內,但在不同CMT內需要使用BUFG。

下圖顯示了兩個DCM驅動PLL,在這種情況下,必須在插入BUFGD。CM和PLL可以在相同或不同的CMT內。

8. DCM時序模型

以下時序圖描述了在四種不同條件下DCM時鐘輸出行為。四種條件分別為:復位/鎖定(Reset/Lock)、固定相移(Fixed-Phase Shifting)、可變相移(Variable-Phase Shifting)、狀態標誌(Status Flags)。

8.1 復位/鎖定(Reset/Lock)

下圖中,DCM已被鎖定,在復位後,所有輸出時鐘都穩定到指定值,並且LOCKED訊號被置位。

時鐘事件1之前:

在時鐘事件1之前,DCM已被鎖定,所有時鐘輸出都處於正確的行為下。

時鐘事件1:

在時鐘事件1之後的某個時間,復位訊號被置位,此時,所有時鐘輸出都變為邏輯0。復位訊號是非同步復位。為使DCM正常工作,必須將復位訊號置位至少三個CLKIN週期。

時鐘事件2:

時鐘事件2發生在復位訊號置位又解除置位之後的幾個週期,在時鐘事件2處,鎖定過程開始。

8.2 固定相移(Fixed-Phase Shifting)

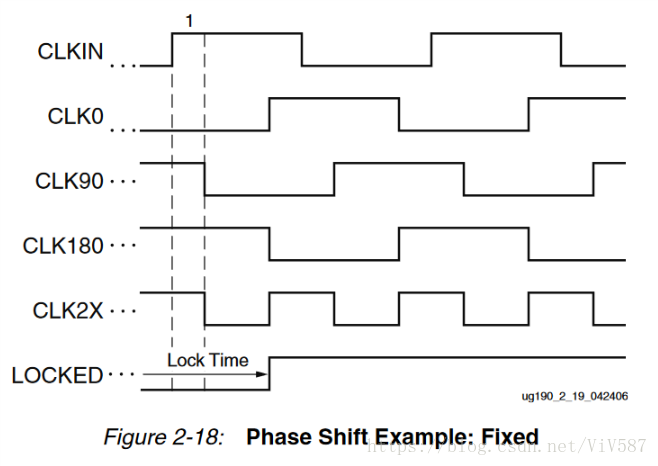

下圖中,時鐘輸出被相移,因而在輸入時鐘之後的某個時間出現,並且LOCKED訊號置位。

時鐘事件1:

時鐘事件1出現在相移應用到DCM上之後,此處相移為正相移。CLK0和CLK2X不再與CLKIN對齊,但輸出時鐘之間對齊。一旦輸出就緒,LOCKED訊號就會置位。

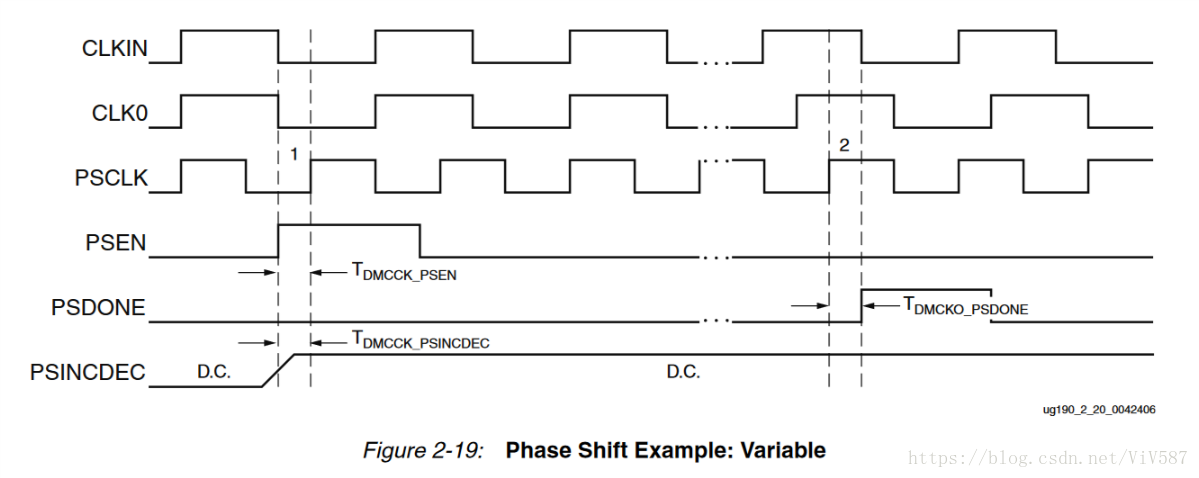

8.3 可變相移(Variable-Phase Shifting)

下圖為動態相移調整示例,當DCM完成一個相位調整時,PSDONE訊號被置位一個週期,在PSDONE置為無效後,PSEN可以再次置位。

時鐘事件1:

在時鐘事件1之前的TDMCCK_PSEN處,置位PSEN。PSEN必須在一個PSCLK週期內有效,否則就不能保證完成相移調整。此外,在時鐘事件1之前的TDMCCK_PSINCDEC處,確定PSINCDEC值來確定是遞增還是遞減。

時鐘事件2:

在時鐘事件2之後的TDMCKO_PSDONE處,PSDONE被置位一個PSCLK週期。完成相移調整的時間不確定,因而需要監視PSDONE來了解相移調整狀態。

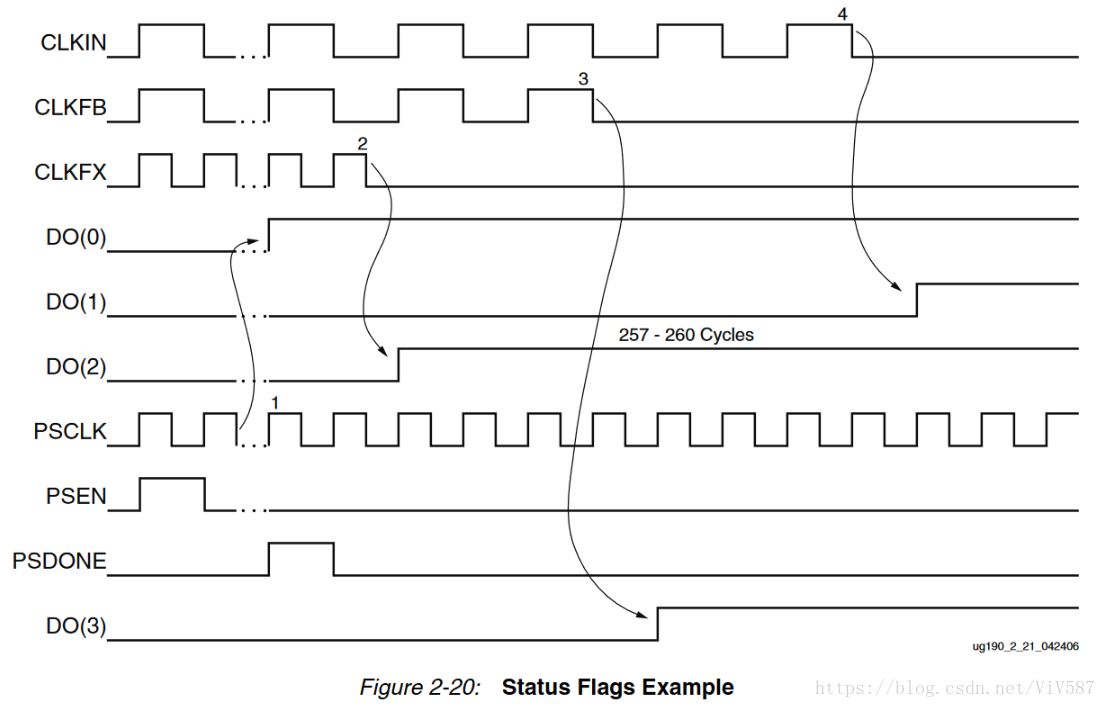

8.4 狀態標誌(Status Flags)

下圖顯示了發生相移溢位以及CLKIN / CLKFB / CLKFX故障時狀態標誌的行為。

時鐘事件1:

在時序圖開始之前,已經相移到最大值處,在時鐘事件1處,PSDONE被置位,然而DCM已達到最大相移,因而不執行相位調整,置位相位溢位狀態DO[0]引腳來指示這種情況。

時鐘事件2:

CLKFX輸出停止翻轉,在此事件發生後的257到260個時鐘週期內,CLKFX停止狀態DO[2]被置位以指示CLKFX輸出停止翻轉。

時鐘事件3:

CLKFB輸入停止翻轉,在此事件發生後的257到260個時鐘週期內,CLKFB停止狀態DO[3]被置位以指示CLKFB輸停入止翻轉。

時鐘事件4:

CLKIN輸入停止翻轉,在此事件發生後的9個時鐘週期內,CLKIN停止狀態DO[1]被置位以指示CLKIN輸入停止翻轉。