vivado2018 中使用modelsim聯合模擬

vivado 中使用modelsim聯合模擬

安裝環境:WIN10 64位

軟體版本:Vivado 2018.2 + Modelsim_win64_SE_10.5-se

modelsim-win64-10.4-se+Vivado 2014.2 相關設定,請移步:https://blog.csdn.net/weixin_41967965/article/details/82688391

在Vivado設定時還有一些不同地方。

1.安裝ModelSim SE 10.4及破解

相關安裝檔案連結:連結:https://pan.baidu.com/s/19o3WX7lrD2slRLTnTCx1Vg

提取碼:jitj

其中10.6c為pe版本的,試裝了一下,可以進行安裝和破解,但是Vivado沒辦法進行編譯,具體原因不明。10.4c也進行了安裝和破解,但是Vivado2018對其不支援了,最低的版本貌似就是10.5了,所以本次教程使用10.5c進行安裝和聯合模擬。

各個版本之間的區別如下:

ModelSim分幾種不同的版本:SE、PE、LE和OEM,其中SE是最高階的版本。而整合在 Actel、Atmel、Altera、Xilinx以及Lattice等FPGA廠商設計工具中的均是其OEM版本。MODELSIM SE是主要版本號,也是功能最強大的版本,支援對Verilog和VHDL語言的混合模擬。除了主要版本外,Mentor公司還為各大FPGA廠商提供 OEM版本: XE是為Xilinx公司提供的OEM版,包括Xilinx公司的庫檔案;AE是為Altera公司提供的OEM版,包含Altera公司的庫檔案;在用特定公司的OEM版進行模擬時不需要編譯該公司的庫檔案,但是模擬速度等效能指標都要落後於SE的版本。

SE版和OEM版在功能和效能方面有較大差別,比如對於大家都關心的模擬速度問題,以Xilinx公司提供的OEM版本ModelSim XE為例,對於程式碼少於40000行的設計,ModelSim SE 比ModelSim XE要快10倍;對於程式碼超過40000行的設計,ModelSim SE要比ModelSim XE快近40倍。

ModelSim SE支援PC、UNIX和LINUX混合平臺;提供全面完善以及高效能的驗證功能;全面支援業界廣泛的標準;Mentor Graphics公司提供業界最好的技術支援與服務。

- ModelSim PE (Personal Edition) is the industry-leading, Windows-based simulator for VHDL, Verilog, or mixed-language simulation environments offering a very cost effective solution for

RTL and gate level simulation; - ModelSim DE (Deluxe Edition) includes full PE functionality plus PSL & System Verilog assertions, Code Coverage, Enhanced Dataflow, Waveform Compare, and support for Xilinx SecureIP as standard;

- ModelSim SE (System Edition) combines high performance and high capacity with the code coverage and debugging capabilities required to simulate larger blocks and systems and attain ASIC gate-level

sign-off. ModelSim SE offers the ability to simulate very large

designs.

安裝破解:

- (1). 安裝軟體,注意:安裝目錄避免出現中文或空格,安裝過程一直點選 Yes 即可。

- (2). 把 MentorKG.exe、mgls.dll以及patch64_dll.bat

一起拷貝到modelsim安裝目錄的win32或win64下,例如【D:\Software\Modelsim_10.5\win64】。 - (3). 進入安裝目錄下的win64 資料夾找到mgls.dll mgls64.dll兩個檔案,去掉只讀屬性。

- (4). 執行patch64_dll.bat,產生license後,放到任意目錄下,例如【D:\Software\Modelsim_10.5\】。

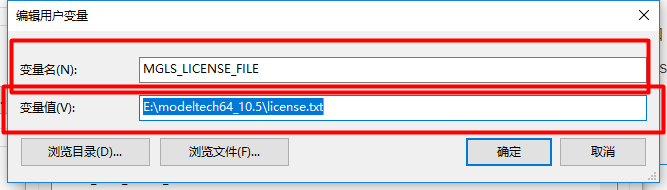

(5). 新建使用者環境變數【MGLS_LICENSE_FILE】,變數值為license放置的目錄,例如:【D:\Software\Modelsim_10.5\LICENSE.TXT】。在win10中,右鍵此電腦,選屬性,再選高階系統設定,選環境變數即可

2.vivado與modelsim的聯合模擬

一、器件庫編譯。首先,在modelsim安裝路徑中新建一個名為vivado2018_lib的資料夾(路徑和檔名可改),如圖下圖所示。

接著選擇vivado選單“Tools”——>“Compile Simulation Libraries…”命令,如下圖所示。

在彈出的對話方塊中設定器件庫編譯引數,模擬工具“Simulator”選為ModelSim,語言“Language”、庫“Library”、器件家族“Family”都為預設設定All(當然也可以根據自己的需求進行設定),然後在“Compiled library location”欄設定編譯器件庫的路徑,這裡選前面新建的vivado2018_lib資料夾,此外在“Simulator executable path”欄設定modelsim執行檔案的路徑,注意箭頭部分不要勾選,如下圖所示。

這一步使用TCL命令如下:

compile_simlib -directory <library_output_directory> -simulator <agr>

-simulator_exec_path<sim_install_location>

例如:a)模擬庫編譯到D:/xilinx_sim_lib;

b)模擬工具使用Modelsim;

c)ModelSim安裝在C:/modeltech64_10.2/win64;

那麼完整的tcl命令就是:

compile_simlib -directory E:/modeltech64_10.4/vivado2018_lib -simulator modelsim -simulator_exec_path E:/modeltech64_10.4/win64

設定好引數後點擊“Compile”按鈕開始器件庫的編譯。下圖所示為正在編譯器件庫的過程中。器件庫編譯結束後給出編譯報告,從報告中看出0個警告和0個錯誤,如圖所示。

開啟modelsim安裝路徑下的vivado2018_lib資料夾,便可以看到已經產生了器件庫,如圖所示。

生成如上圖所示檔案,要將modelsim設定為使用者全域性變數,那麼下一次就不需要在此編譯庫了。步驟如下圖所示,將變數名設定為MODELSIM,變數值為modelsim.ini的路徑。

二、在vivado中設定modelsim(即第三方模擬工具)的安裝路徑。在vivado選單中選擇“Tools”——>“Setting…”,選擇“Tool setting”——>“3rd Party Simulators”選項卡,在“ModelSim”欄中輸入或選擇modelsim工具的安裝路徑,如下圖所示。

三、在vivado中關聯了modelsim軟體和編譯器件庫之後,就可以在vivado中呼叫modelsim軟體對設計進行模擬了。不過,在對每一個新建的工程設計進行模擬時需要進行一些設定。選擇vivado選單“Flow”——>“Simulation Settings…”命令或點選流程嚮導中選擇“Simulation Settings…”命令,分別如圖所示。

在彈出的對話方塊中,設定模擬工具為modelsim、模擬語言為verilog或VHDL或混合,當設計中用到vivado中自帶的模擬工具時,還要指定器件庫的路徑,如圖10所示。關於模擬的其他引數在這裡就不作介紹了。

設定好模擬引數後,如果設計檔案和模擬檔案也準備好,那麼就可以開始對設計的功能進行模擬了。選擇選單“Flow”——>“Run Simulation”——>Run Behavioral Simulation選相應的模擬型別或點選流程嚮導中的“Run Simulation”——>選相應的模擬型別進行模擬,如圖所示。