NAND Flash

轉自https://blog.csdn.net/shanghaiqianlun/article/details/6992915

NAND Flash

以Micron公司的MT29F2G08為例介紹NAND Flash原理和使用。

1. 概述

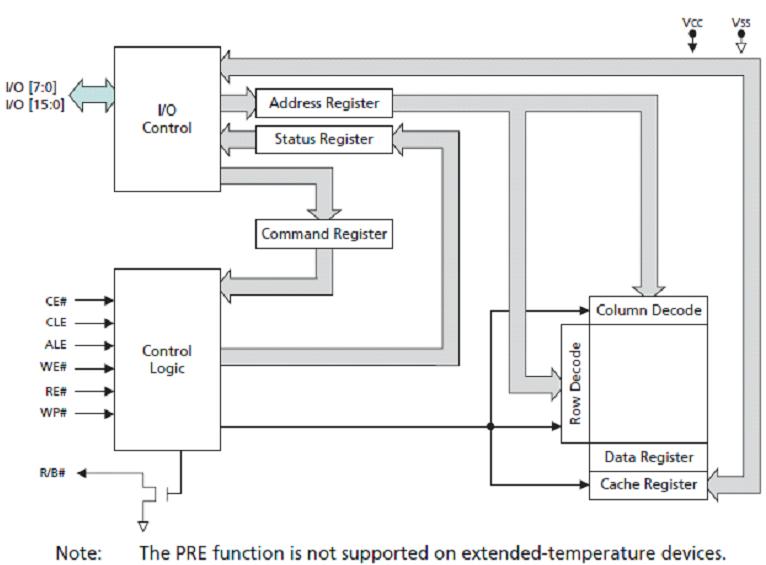

MT29F2G08使用一個高度複用的8-bit匯流排(I/O[7:0])來傳輸資料、地址、指令。5個命令腳(CLE、ALE、CE#、WE#)實現NAND命令匯流排介面規程。3個附加的腳用作: 控制硬體防寫(WP#)、監視晶片狀態(R/B#),和發起上電自動讀特徵(PRE-僅3V晶片支援)。注意, PRE功能不支援寬溫晶片。

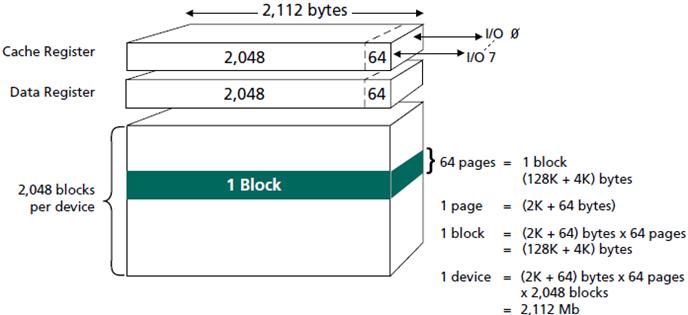

MT29F2G08內部有2048個可擦除的塊,每個塊分為64個可程式設計的頁,每個頁包含2112位元組(2048個位元組作為資料儲存區,64個備用位元組一般作為錯誤管理使用)。

每個2112個位元組的頁可以在300us內程式設計,每個塊(64x2112=132K)可以在2ms內被擦除。片上控制邏輯自動進行PROGRAM和ERASE操作。

NAND的內部儲存陣列是以頁為基本單位進行存取的。讀的時候,一頁資料從內部儲存陣列copy到資料暫存器,之後從資料暫存器按位元組依次輸出。寫(程式設計)的時候,也是以頁為基本單位的:起始地址裝載到內部地址暫存器之後,資料被依次寫入到內部資料暫存器,在頁資料寫入之後,陣列程式設計過程啟動。

為了增加程式設計的速度,晶片有一個CACHE暫存器。在CACHE程式設計模式,資料先寫入到CACHE暫存器,然後再寫入到資料暫存器,一旦資料copy進資料暫存器後,程式設計就開始。在資料暫存器被裝載及程式設計開始之後,CACHE暫存器變為空,可以繼續裝載下一個資料,這樣內部的程式設計和資料的裝載並行進行,提高了程式設計速度。

內部資料搬移命令(INTERNAL DATA MOVE)也使用內部CAHCE暫存器,通常搬移資料需要很長時間,通過使用內部CACHE暫存器和資料暫存器,資料的搬移速度大大增加,且不需要使用外部記憶體。

2. 功能框圖

3. 管腳

| 名稱 | 型別 | 描述 |

| ALE | I | 地址鎖存使能。ALE為高時,在WE#下降沿,地址資訊通過I/O[7:0]鎖存片內的地址暫存器。如果傳輸的不是地址資訊,ALE應該為低。 |

| CE# | I | 片選。一旦器件進入PROGRAM或ERASE操作,CE#可以變無效。 |

| CLE | I | 命令鎖存使能。CLE為高時,在WE#上升沿,命令通過I/O[7:0]鎖存到命令暫存器,當不傳輸命令時,CLE應該為低。 |

| PRE | I | 上電讀使能。 |

| RE# | I | 讀使能。 |

| WE# | I | 寫使能。 |

| WP# | I | 防寫。當為低時候,所有的PROGRAM和ERASE都被禁止。 |

| I/O[7:0] | I/O | 資料輸入/輸出。傳輸命令、資料、地址。僅在讀操作時,資料是輸出。 |

| R/B#, R/B2 | O | 準備好/忙。集電極開路輸出。外部需要接上拉電阻,這個腳表示晶片正在進行PROGRAM或ERASE操作。在讀操作期間,表示資料正從陣列中傳輸到序列資料暫存器中,一旦這些操作完成,R/B#回到High-Z狀態。 |

| Vcc | 電源 | 電源 |

| Vss | 地 | 地 |

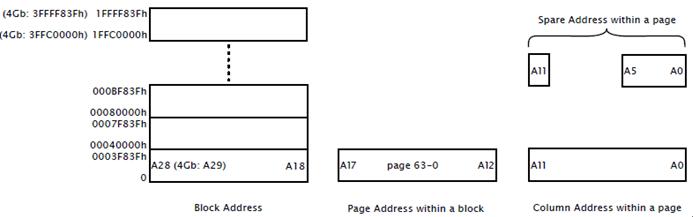

4. 定址

Block地址和頁地址 = 實際的頁地址,希望通過這個圖,我們能理解塊、頁、塊地址,頁地址,列地址,備份空間,備份地址

| Cycle | I/O7 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |

| 1 | CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

| 2 | LOW | LOW | LOW | LOW | CA11 | CA10 | CA9 | CA8 |

| 3 | RA19 | RA18 | RA17 | RA16 | RA15 | RA14 | RA13 | RA12 |

| 4 | RA27 | RA26 | RA25 | RA24 | RA23 | RA22 | RA21 | RA20 |

| 5 | LOW | LOW | LOW | LOW | LOW | LOW | LOW | RA28 |

CAx:列地址;RAx=行地址

5. 匯流排操作

| CLE | ALE | CE# | WE# | RE# | WP# | PRE# | MODE | |

| H | L | L | 上升沿 | H | X | X | 讀模式 | 命令輸入 |

| L | H | L | 上升沿 | H | X | X | 地址輸入 | |

| H | L | L | 上升沿 | H | H | X | 寫模式 | 命令輸入 |

| L | H | L | 上升沿 | H | H | X | 地址輸入 | |

| L | L | L | 上升沿 | H | H | X | 資料輸入 | |

| L | L | L | H | 下降沿 | X | X | 依次讀和資料輸出 | |

| L | L | L | H | H | X | X | 在讀期間(忙) | |

| X | X | X | X | X | H | X | 在程式設計期間(忙) | |

| X | X | X | X | X | H | X | 在擦除期間(忙) | |

| X | X | X | X | X | L | X | 防寫 | |

| X | X | H | X | X | 0V/Vcc | 0V/Vcc | 待機 | |

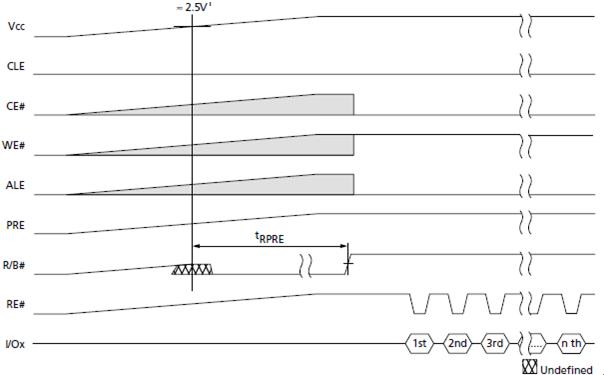

上電自動讀:在上電期間,PRE為VCC,3V VCC器件自動傳輸第一頁到資料暫存器,而無需要釋出一個命令或地址鎖存序列。在VCC達到大約2.5V的時候,內部電壓檢測器觸發上電自動讀功能。在第一頁資料copy到資料暫存器過程中,R/B#為低,當copy結束後,R/B#變高,在RE#脈衝的作用下第一頁資料可以依次輸出。

6. 命令表

| 操作 | 週期1 | 週期2 | 在忙期間有效 |

| PAGE READ | 0x00 | 0x30 | NO |

| PAGE READ CACHE MODE START | 0x31 | - | NO |

| PAGE READ CACHE MODE START LAST | 0x3F | - | NO |

| READ for INTERNAL DATA MOVE | 0x00 | 0x35 | NO |

| RANDOM DATA READ | 0x05 | 0xE0 | NO |

| READ ID | 0x90 | - | NO |

| READ STATUS | 0x70 | - | NO |

| PROGRAM PAGE | 0x80 | 0x10 | NO |

| PROGRAM PAGE CACHE | 0x80 | 0x15 | NO |

| PROGRAM for INTERNAL DATA MOVE | 0x85 | 0x10 | NO |

| RANDOM DATA INPUT for PROGRAM | 0x85 | - | NO |

| BLOCK ERASE | 0x60 | 0xD0 | NO |

| RESET | 0xFF | - | YES |

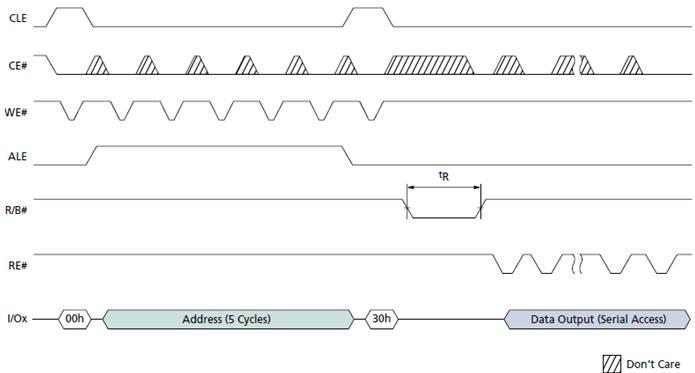

7. PAGE READ,0x00-0x30

5個地址週期,確定了讀出的起始地址,資料才RE#脈衝的作用下,從這個起始地址開始依次輸出,直到這一頁的結束。

8. RANDOM DATA READ,0x05-0xE0

隨機資料讀,是為了使用者能夠設定新的列地址,增加資料讀出的靈活性,隨即讀模式在頁讀(0x00-0x30序列)後使能。這個命令的釋出次數是不受限制的。但僅僅是當前頁資料的讀出。

9. PAGE READ CACHE MODE START,0x31;PAGE READ CACHE MODE START LAST,0x3F

釋出PAGE READ命令後,在R/B#變高後,在傳送0x31命令,這時啟動將資料暫存器的內容傳給CACHE暫存器,然後就可以順序從CACHE裡讀第一個PAGE READ命令獲得資料,由於這是資料暫存器是沒有用的,因此,晶片自動啟動讀下一頁的PAGE READ命令,將下一頁讀到資料暫存器,可以看出這麼做提高的讀出的速度,除了第一個PAGE READ命令外,其他PAGE READ命令都是後臺自動進行的。再最後一次使用0x3F命令,以便禁止晶片再次自動釋出PAGE READ命令。

10. READ ID,0x90

讀出廠家的晶片標識。

11. READ STATUS,0x70

讀出晶片的8bit狀態。可以通過RE#脈衝,反覆讀。

12. 程式設計操作

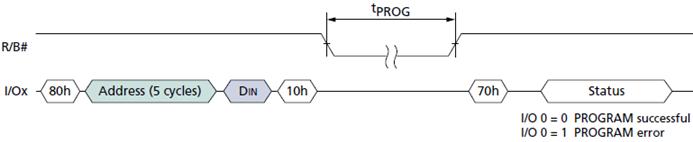

PROGRAM PAGE 0x80-0x10:

Micron NAND FLASH僅支援頁的程式設計,在一個塊以內,頁必須從一個塊的頁最低位到這個塊的頁的最高位連續程式設計,禁止隨機頁地址的程式設計。

晶片也支援頁的部分程式設計操作,這意味著任何單個位在需要一個擦除之前僅可以被程式設計一次,然而,這種頁能被劃分成在需要一個擦除之前允許最大8個程式設計操作。

SERIAL DATA INPUT 0x80:

PAGE PROGRAM操作要求載入SERAIL DATA INPUT(0x80)命令進入命令暫存器,隨著5個地址週期之後,序列資料通過連續的WE#週期載入到值得的起始地址,PROGRAM(0x10)命令在資料輸入完成之後被寫入,內部寫狀態週期自動執行合適的程式設計演算法,並控制所有必要的定時程式設計和比較操作。寫比較僅僅檢測“1”是否被成功地程式設計為“0”了。

R/B#在陣列程式設計期間(tPROG)為低,在程式設計操作期間,僅READ STATUS和RESET命令有效,狀態暫存器的Bit6反映R/B#的狀態,當晶片準備好時,讀Bit0的狀態確定程式設計操作是否成功或失敗,命令暫存器在新的有效命令寫入之前,一直停留在讀狀態暫存器模式。

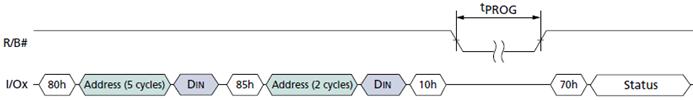

RANDOM DATA INPUT 0x85:

在發起資料集輸入之後,可以通過RANDOM DATA INPUT命令向新的列地址寫入資料。在釋出0x10命令之前,可以對同一頁多次使用0x85命令。

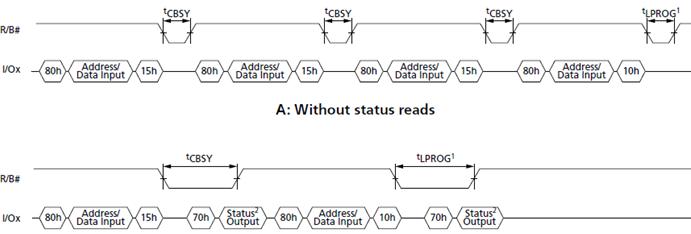

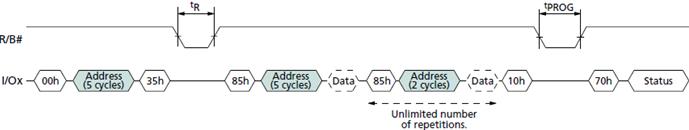

PROGRAM PAGE CACHE MODE 0x80-0x15:

CACHE程式設計實際上是標準的頁程式設計命令的帶緩衝程式設計模式,程式設計開始是釋出SERIAL DATA INPUT(0x80)命令,隨後是5個地址週期,以及頁的全部或部分資料,資料copy到CACHE暫存器,然後釋出CACHE WRITE(0x15)命令。資料在WE#的上升沿鎖存到資料暫存器,在這個鎖存期間,R/B#為低,鎖存結束之後,R/B#變高,程式設計開始。

當R/B#變高之後,新的資料可以通過釋出另一個CACHE PROGRAM命令來寫入,R/B#保持低的時候由實際的程式設計時間來控制,第一次等於資料從CACHE暫存器寫入到資料暫存器需要的時間,之後,只有資料暫存器的內容被程式設計進陣列之後,CACHE暫存器才能鎖存到資料暫存器,所有,以後的R/B#為低的實際應該更長一些。

狀態暫存器中反映CACHE R/B#的Bit6可以通過READ STATUS命令讀出,以便確定什麼時候,CACHE暫存器準備好接受新的資料了。

狀態暫存器中反映R/B#的Bit5可以被查詢,以確定什麼時候當前程式設計週期的實際陣列程式設計完成。

如果僅使用R/B#來確定程式設計是否完成,那麼程式設計序列的最後一頁必須使用PROGRAM PAGE(0x10)來替代CACHE PROGRAM(0x15)。如果CACHE PROGRAM命令每次都使用,狀態暫存器的Bit5必須用來確定程式設計是否結束。

當狀態暫存器的bit6為1時,狀態暫存器Bit0返回前一頁的程式設計是否成功,當前PROGRAM操作的成功與否的狀態是:Bit5為“1”(準備好狀態)時的Bit0狀態

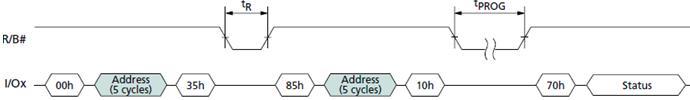

13. 內部資料搬移

內部資料搬移需要兩個命令序列,先發佈一個READ FOR INTERNAL DATA MOVE(0x00-0x35),然後釋出一個INTERNAL DATA MOVE(0x85-0x10)命令,資料搬移僅僅支援被讀資料die範圍。

READ FOR DATA MOVE 0x00-0x35:先將00寫到命令暫存器,然後是內部源地址(5個週期),之後,將0x35寫到命令暫存器,這將起動從記憶體傳輸一頁到CACHE暫存器。儘管5個週期的地址被髮布,但是列地址是被忽略的。現在晶片準備接受INTERNAL DATA MOVE(0x85-0x00)命令。

INTERNAL DATA MOVE 0x85-0x10:在READ FOR INTERNAL DATA MOVE命令釋出之後,以及R/B#變高,就可以釋出INTERNAL DATA MOVE命令了,這個命令將CACEH暫存器內容傳輸到資料暫存器,然後程式設計到新的目標地址,再INTERNAL DATA MOVE命令以及地址序列之後,R/B#變低,同時內部控制邏輯自動將資料程式設計到新的頁,READ STATUS命令和狀態暫存器的bit6能代替R/B#,以確定程式設計什麼時候完成。狀態暫存器Bit0指示操作是否成功。在INTERNAL DATA MOVE命令序列期間,RANDOM DATA INPUT(0x85)用來修改原始資料的一個或多個字:首先,使用0x00-0x35命令序列將資料copy到CACHE暫存器,然後,使用帶要修改的資料地址的命令RANDOM DATA INTPUT(0x85),新的資料輸入呈現在外部資料腳,這將copy新的資料進入CACHE暫存器。當0x10寫入命令暫存器時候,原始資料+修改的資料被傳輸到資料暫存器。程式設計新的一頁將開始,如果有必要RANDOM DATA INPUT命令可以在啟動程式設計序列(0x10)之前釋出多次。因為INTERNAL DATA MOVE操作並不使用外部記憶體,所以ECC不可能在程式設計之前用來檢查錯誤,這將可能或導致資料錯誤。在這種情況下,執行多次INTERNAL DATA MOVE操作,這些位錯誤可能會因沒有校正而積累。由於這個原因,我們強烈推薦利用INTERNAL DATA MOVE的系統使用魯棒ECC方案。這將可以對每個SECTOR校正2個或多個錯誤。

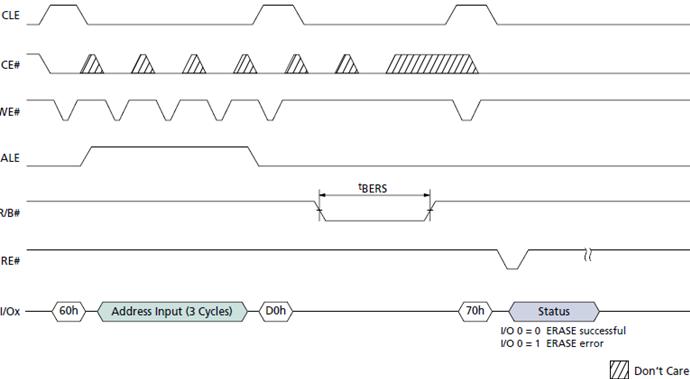

14. 塊擦除操作,0x60-0xD0

一次擦除一個塊。三個週期的地址A[28:18]被要求,先發布ERASE SETUP(0x60)命令,然後是三個地址週期,之後是ERASE CONFIRM(0xD0)命令。通過READ STATUS RESGISTER命令讀擦除操作的狀態,當bit6=1時,操作完成,Bit0指示通過/失敗條件,0表示通過。

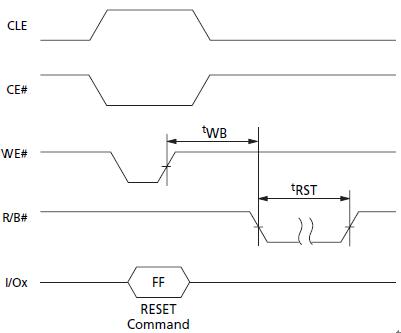

15. 復位操作,0xFF

復位操作使晶片進入一個已知的狀態,中斷正在處理的命令序列。RANDOM READ、PROGRAM、ERASE命令在晶片忙狀態可以被中斷,正在被程式設計的位置或正在擦除的塊的內容變無效,資料有可能會部分地被擦除或程式設計。命令暫存器被清除,準備好進入下一個命令。

復位後狀態暫存器內容:

| 條件 | 狀態 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Hex |

| WP#高 | 準備好 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0xE0 |

| WP#低 | 準備好和防寫 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0x60 |

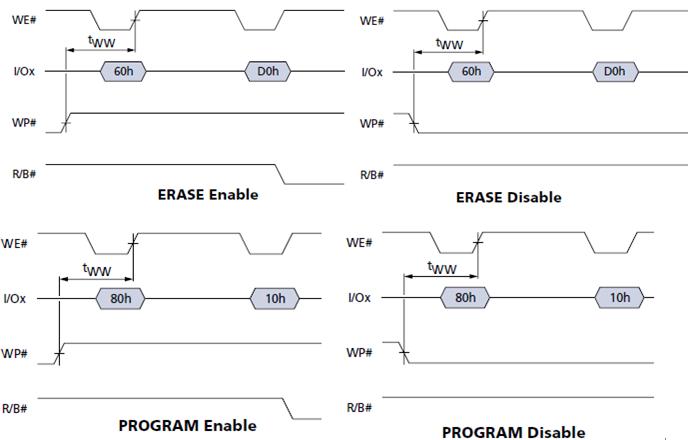

16. 防寫操作

防寫是為了防止不小心的程式設計和擦除操作。當WP#為低時候,所有的程式設計和擦除操作都會被禁止。

17. 錯誤管理

Micron NAND晶片出廠時並不保證晶片中所有的塊都是好的,只要2048個塊中有不少於2008個完好塊就認為是合格品可以出廠。但是壞的塊的存在,並不影響好的塊的操作。在應用系統中應該提供壞塊影射、替代、錯誤校正等演算法就可以保證資料具有很高的可靠性和完整性。

每個CE#的第一個塊(物理塊地址是0)絕對是經過測試,是完好無缺的。這就提供了存放BOOT程式碼和重要資訊的儲存位置。

在晶片出廠之前,廠家會在每個壞塊的第一或第二頁的第一個備份位置(列地址是2048)用非0xFF程式設計來標識壞塊。

系統軟體在進行任何擦除或程式設計操作之前應該檢查每個塊的第一或第二頁的第一個備份地址資料。這樣建立一個壞塊表。

經過一定時間的使用,記憶體的某些位置可能會不能正確地程式設計和擦除,為了確保資料的可靠性,應該採取一些預防措施,比如:

l 在寫、擦除、或資料搬移操作之後,總是檢查狀態。

l 使用某些型別的錯誤檢測糾正演算法,以便能恢復某些輕微iede1錯誤。

l 使用壞塊替代演算法。