FPGA設計-時序約束(理論篇)(轉載)

1. FPGA時序約束以及高速ADC約束例項

2. TDC進位延時鏈設計以及研究

3. TDC的精度以及自動校正演算法的實現

STA:Static Timing Analysis

STA(Static Timing Analysis,即靜態時序分析)在實際FPGA設計過程中的重要性是不言而喻的,其作用是:

1. 幫助分析和驗證一個FPGA設計的時序是否符合要求;

2. 指導fitter(佈線綜合器)佈局佈線出符合要求的結果;

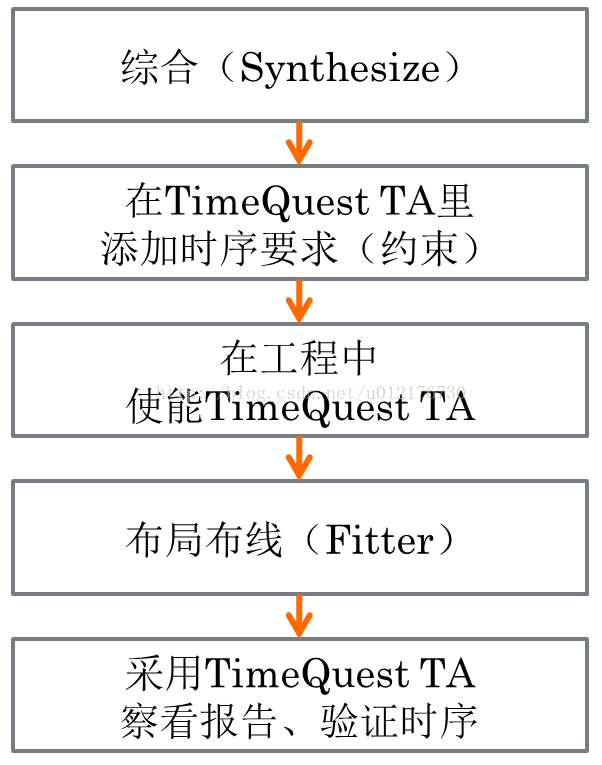

簡單地說,靜態時序分析(STA)告訴我們電路的實際表現如何,而提供約束(SDC檔案,即上面的要求)來告訴分析工具我們希望電路的表現應該是怎樣。Quartus II自帶的STA工具TimeQuest TA在整個FPGA設計過程中的使用流程如下圖所示:

圖 1 TimeQuest TA使用流程

簡而言之,我們需要學會:

A. 正確理解時序,看背景知識介紹

B. 正確編寫SDC檔案,以及利用TimeQuest TA生成SDC約束命令,SDC介紹

C. 利用TimeQuest TA來檢視和驗證時序

一、 背景知識介紹:

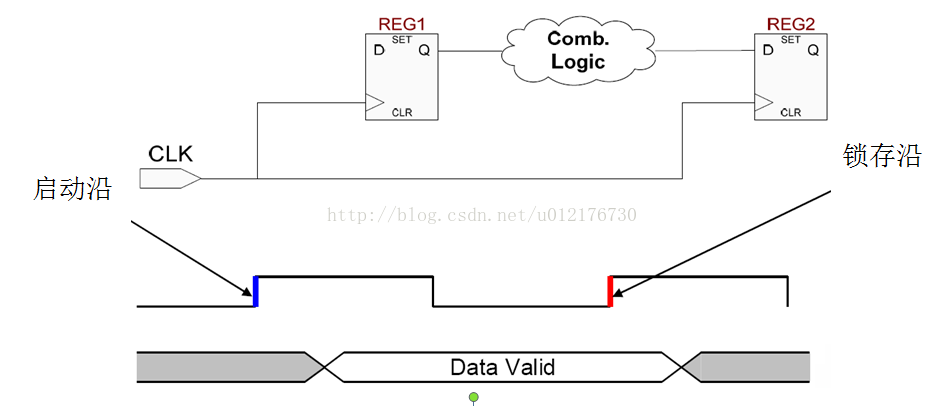

1.1 啟動沿(launch)和鎖存沿(latch):

圖 2 啟動沿和鎖存沿

啟動沿:資料被launch的時鐘邊沿;也就是說,每一個啟動沿,一般都會產生一個新的資料!

鎖存沿:資料被latch的時鐘邊沿;也就是說,每一個鎖存沿,都會有一個新的資料被儲存!

對於如上圖所示的級聯的暫存器電路而言(忽略上一級觸發器輸出到下一級觸發器輸入之間的邏輯關係),一般藍色的上升沿作為第一個觸發器的啟動沿,而紅色的上升沿(一般都是緊跟著啟動沿後的有效邊沿)。所以說:藍色的啟動沿之後由REG1輸出有效資料,並在紅色的邊沿被鎖存進REG2並輸出到下級。

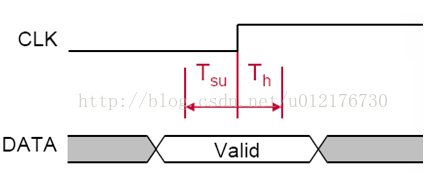

1.2 建立(setup)和保持(hold)時間

圖 3 建立和保持時間

上述的鎖存沿會將資料儲存下來,但是必須要滿足一定的條件:

建立時間Tsu:在時鐘有效沿之前,資料必須保持穩定的最小時間;

保持時間Th:在時鐘有效沿之後,資料必須保持穩定的最小時間;

這就相當於一個視窗時間,在有效邊沿的視窗時間內,資料必須保持穩定;這裡的時鐘訊號時序和資料訊號時序,都是暫存器實際感受到的時序;什麼事實際感受到的,下面會繼續分析;

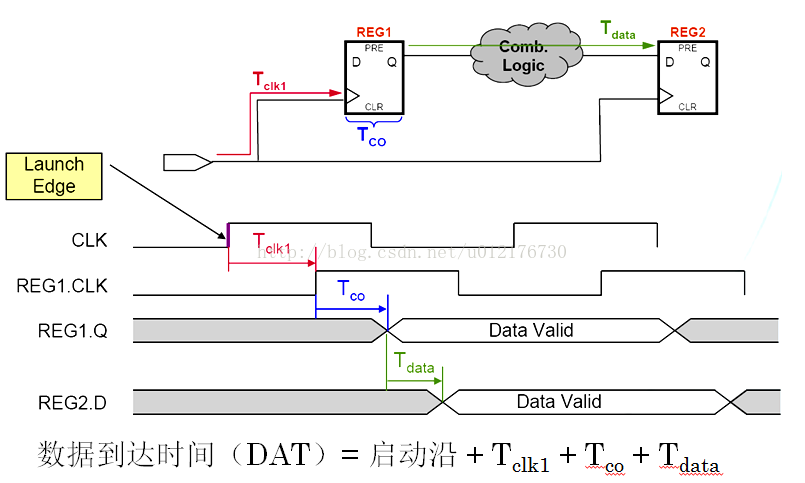

1.3 資料到達時間(DAT:data arrival time)

所有的訊號在FPGA內部傳播都會有延時,包括時鐘訊號、資料訊號(實際上不該如此可以的區分這兩種訊號,在一定條件下,這兩個訊號可能可以相互轉換,這個是題外話了),也就是說,從訊號的發出點到訊號的接收點,會存在一個延時,這個延時可能是因為FPGA內部空間分佈所致,也有可能是因為組合邏輯造成,這裡不再深究;

圖 4 資料到達時間示意圖

正如上圖所示,在計算資料到達時間時,一般都會存在3個延時:

1. Tclk1:時鐘訊號從起點(一般是PLL輸出或者時鐘輸入引腳)到達啟動暫存器(或說啟動觸發器)的相應clk埠所耗的時間;假如CLK是由PLL發出的時鐘訊號(稱之為源時鐘),這個訊號經過FPGA內部的“連線”最終來到了REG1(啟動觸發器)的clk端,所以此時在REG的clk1處也會有周期性的時鐘訊號REG1.CLK(如圖所示);可以看到,此時的CLK(源時鐘)和REG1.CLK實際上有個(相位差)時間差,這個時間差就是Tclk1;

2. Tco:啟動暫存器內部延時,是暫存器REG1感受到有效的上升沿後,到資料真正從從REG1的Q輸出之間延時;請注意:上述所謂的有效的上升沿,就是REG1.CLK,而不是CLK;所以實際的有效資料輸出的時序如上圖的REG1.Q;

3. Tdata:資料從上級暫存器輸出Q(經過所有其他組合邏輯以及FPGA內部走線)到下級暫存器的資料輸入D之間的延時;如圖所示,資料從從REG1的Q流向了REG2的D,所以REG2.D實際感受到的資料時序是REG2.D;

假如將上圖中的launch Edge作為時間0點,將一些列的延時累加,所得結果稱之為資料到達時間,DAT:

DAT=啟動沿+Tclk1+Tco+Tdata;

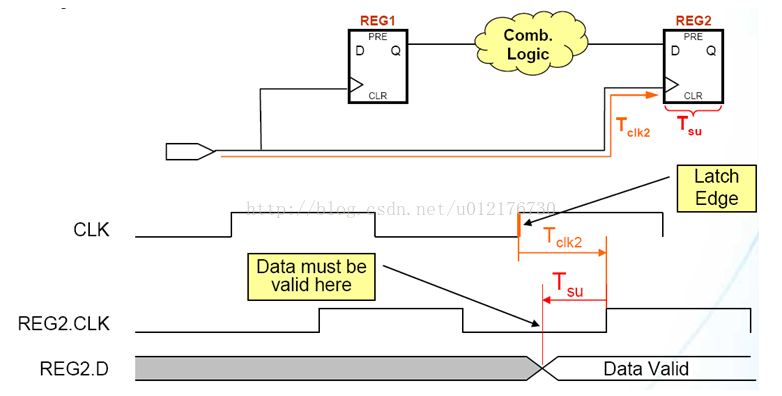

1.4 資料建立需要時間(DRTsu:data require time (setup))

圖 5 資料建立需要時間

分析方法同上,需要計算資料建立時間,也需要兩個延時:

1. Tclk2,不同於上述的Tclk1,這個延時是時鐘從起點(一般是PLL或者時鐘輸入引腳)到鎖存觸發器之間的延時;如上圖所示,REG2實際感受到的時鐘來自於其本身的clk引腳,而不是源時鐘CLK,他們之間存在一個延時,即Tclk2;所以REG2實際感受到的時鐘,實際上是上圖的REG2.CLK;

2. Tsu:上面分析過了,每一個數據被鎖存都要滿足建立時間和保持時間,Tsu就是建立時間,也就是在REG2實際感受到Latch Edge時,資料如果需要被正確鎖存,就必須提前Tsu的時間來到REG2的D;

綜合時鐘走線延時Tclk2以及Tsu,我們得到了資料建立時間DRTsu:

DRTsu=鎖存沿+Tclk2-Tsu。

也就是說在DRTsu時刻之前,資料必須已經有效且穩定

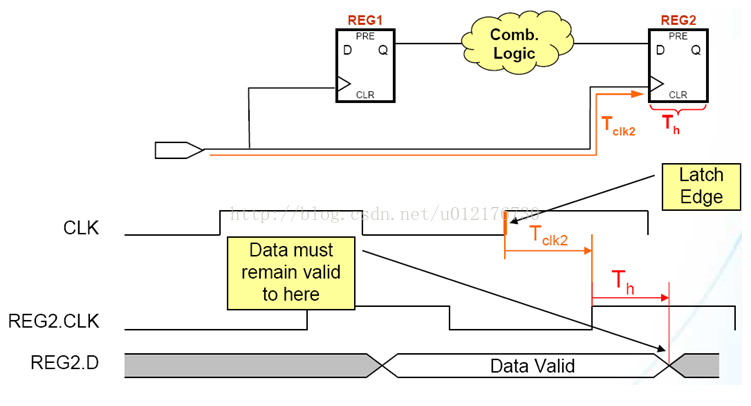

1.5 資料保持需要時間(DRTh:data require time (hold))

圖 6 資料保持需要時間

即DRTh=鎖存沿+Tclk2+Th;

也就是說,資料在DRTh時間之前必須保持住不變;

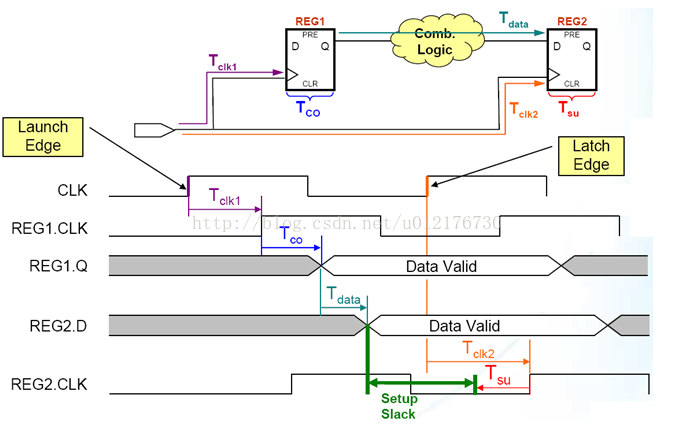

1.6 建立時間裕量(Setup Slack)

建立時間裕量指的是資料到達時間和資料建立需要時間之間的關係:

圖 7 建立時間裕量

如上圖所示,在0時刻(Launch edge),源時鐘CLK說,“啊,我要產生一個新的資料”,但是這個命令(啟動沿)並沒有馬上傳達到REG1,而是有個延時Tclk1。所以在Tclk1時刻,REG1終於聽到了(感受到了有效的時鐘上升沿,就是啟動沿)老大的命令,就開始準備,他憋了一會兒,又延時了Tco,終於產生了資料(REG1.Q上有了valid data);這個有效資料也是慢吞吞的來到了他的終點,又浪費了Tdata。最終在Tclk1+Tco+Tdata時間後,REG2得到了這個資料;別以為REG2得到這個資料就完事了,REG2也是個傲嬌的娃,怎麼個傲嬌法,下面繼續分析;老大CLK在0時刻傳送了啟動沿之後,休息了一個時鐘週期,在Latch edge時突然想起來,剛才讓REG1發出的資料,REG2要接受啊,不然就浪費了,於是乎他又對REG2下達了命令,新資料要來了,準備好接受!但是這個命令也不是馬上就到了REG2的耳中,而是經過了Tclk2的時間。等到REG2接收到命令後(實際感受到了有效的Latch Edge),他就看看自己家門口沒有資料已經來了(檢查REG2.D是否有資料),同時要看看這個資料是不是符合他的胃口的(滿足鎖存的條件),他要求資料必須在他接收到老大命令的時候已經等了Tsu時間(資料建立時間),由要求這個資料在他家門口不能早退,必要再保持Th時間(資料保持),如果都滿足了,REG2就開心的接受了這個資料,反之,他就會覺得,REG1準備的資料太懶惰了(沒有提前Tsu時間到達),又或者性子太急(沒有多逗留th),一概不收!

所以這裡涉及到兩個要求,第一個就是建立時間裕量:

正如上圖所示Setup Slack=DRTsu-DAT。

如果Setup Slack為正,則說明資料在規定的時間內達到了目標。反之,則認為資料並沒有在規定的時間達到目標,此時REG2鎖存的資料很有可能是亞穩態;

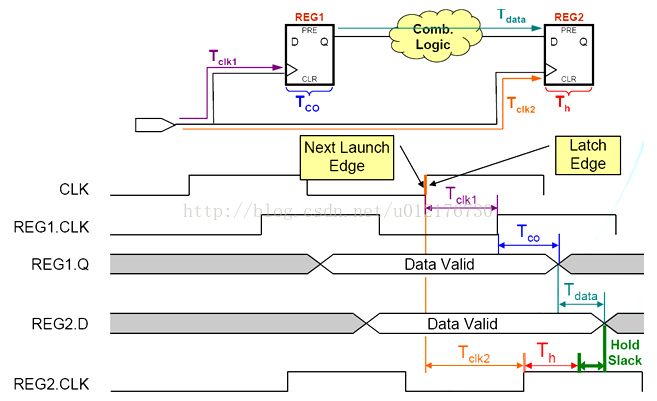

1.7 保持時間裕量(hold slack)

圖 8保持時間裕量

如上所述,hold slack = DAT – DRTh

如果為正,則認為資料在被鎖存的時候有足夠多的穩定時間,是有效的。反之則認為資料有誤或者資料可能是亞穩態;

小結:

理解了上面的7個概念,就明白了:如果時鐘頻率過快或者資料延時太大,都會導致錯誤的時序。在FPGA內部暫存器到內部暫存器之間,所有的延時都是建立在時序模型上的,如slow和fast,這些模型從兩個極端工作情況來分析FPGA能否正常工作;只要滿足這兩個工況,則FPGA在其他環境下都能滿足時序!