RISC-V雙週簡報0x15:第八屆Workshop會以議程公佈(2018-04-13)

RISC-V 雙週簡報 (2018-04-13)

要點新聞:

- 第八屆Workshop議程公佈

- AndesTech的64-bit CPU細節

- SiFive融資5000萬美元

RV新聞

第八屆RISC-V Workshop議程公佈

第八屆RISC-V Workshop的議程公佈了。這次有許多有趣的Topic,像是google的工程師在《Use of RISC-V on Pixel Visual Core》中將介紹他們使用RISC-V的情況。

關於RISC-V指令集擴充套件標準化過程的官方解釋

3月初,Alex Bradbury向RISC-V提出疑問,希望基金會能夠進一步說明RISC-V各工作小組制定RISC-V擴充套件指令集以及擴充套件指令集被標準化的流程。現在RISC-V基金會的Rick O’Connor正式做出了

- RISC-V的工作空間給出了工作小組在45天草案意見徵集期的責任:

5.5 COMMITTEE REPORTS

Committee Reports shall be made publicly available online via the RISC-V website (www.riscv.org) for external comments and discussion for at least forty-five (45) days before the Board votes on the Committee Reports. The Committee Reports forwarded to the Board shall include a document with the Committee’s response to issues raised by Committee members who voted against such Committee Report and by any dissenting public comments.

(解釋:RISC-V董事會針對某一個RISC-V擴充套件指令集草案投票之前,該草案的修訂工作小組必須針對該草案經行45天的公開意見收集。在蒐集期後,工作小組需要提交對小組內部的反對意見和公眾的反對意見的回覆,以供董事會參考。)

- 工作小組需要由RISC-V的技術或市場委員會提出請求,並交與董事會同意。

As per the Foundation Bylaws the BoD approves Committees and Sub-Committees (Task Groups). Tech Comm and Mktg Comm Chairs bring forward recommendations from their member rosters.

- 45天公示期至董事會投票之間的時間取決於公示期收到的意見。工作小組可能選擇繼續修訂從而重新公示。無論如何,工作小組必須對公示期內意見作出迴應。

Depending on the scope of the feedback and how the comments are dispositioned by the Task Group, the spec in question can be recommended for approval or go back into the editing process. All feedback / comments received must be addressed by the TG.

- 董事會將每月開會一次。不過遇到緊急情況,董事會可以臨時開會。

The BoD meets monthly, but we can always convene an ad-hoc BoD mtg for any spec release that is considered urgent. At this stage the BoD is primarily reviewing to ensure our process as published in the Bylaws has been followed properly with all commentary being addressed as well as reviewing the source of contributed content in the spec.

技術討論

為什麼RISC-V定義4KB為頁的大小

頁的大小其實和應用程式的執行效能相關。在不改變實際程式碼的情況下,改變頁的大小有可能就可以明顯提升執行效能。那麼,RISC-V為什麼要預設定義頁的大小為4KB呢?其原意看起來是軟體的可移植性。mmap()和mproptect()函式將頁大小這個體系結構細節暴露給了軟體,而很多軟體都是基於4KB大小的頁設計的。如果改變頁的大小,很多使用上述函式的程式都可能發生錯誤。RISC-V對大頁的支援,某種程度上也緩解了多非預設頁大小的需求。

- David Chisnall的解釋:hw-dev

如何形式化驗證 Implementation-defined 的性質?

Formal Spec Task Group的 Rishiyur 最近在isa-dev中提出了它們對於如何形式化驗證 Implementation-defined 性質的看法。他們希望使用針對不同的實現,使用不同的 “opaque but deterministic function” 來改變狀態。並避免 non-deterministic transform。

這個問題在系統引數有所變化時特別嚴重,像是改變MISA.C、關掉並再開浮點數暫存器、改變 MISA.MXL都是。MISA.C的問題經過上次的討論後,已經比較architecture-defined,但在其他情況下,還是 Implementation-defined。舉例來說,關掉浮點數暫存器後再開時,裡面的值應該被重設呢?還是要儲存關掉前的值?關於這個問題,目前在討論中還沒有結論,但可以確定的是,每個實現都應該選擇一個情況,來避免 Non-deterministic transform。

程式碼更新

Chisel和FIRRTL更新

生態系統

RISC-V Debian移植的最新進展

Manuel A. Fernandez Montecelo最近在其debian個人主頁上發表他在RISC-V移植上的最新進展。

We have a new port for RISC-V, flavour riscv64 (64-bits little-endian) in Debian Ports.

And it’s doing well.

去年的時候,這位愛好者就曾經嘗試過一次移植。而隨著軟體生態系統越來越成熟。這次,在qemu-system-riscv64上,移植的過程更加順利。

RISC-V OpenWrt的移植

群頭(xfguo)曾在2016年成功移植了一版OpenWrt,當時受限與virtio驅動的一些問題而停止。今年開春,隨著各類工具鏈、linux、qemu都進入了主線。群頭開始了一輪新的移植工作,目前已經能夠成功在qemu上boot起OpenWrt,網路通訊也沒有問題。

下一步群頭希望能夠整理並提交到OpenWrt主線,有興趣的同學可以clone https://github.com/xfguo/riscv-openwrt-port這個repo,然後按照指示來一步步構建並在qemu上執行。

感謝周有鬆同學的幫助!同時歡迎有興趣的同學加入!

實用資料

被關閉的RISC-V B擴充套件指令集草案

RISC-V的擴充套件指令集需要由一個RISC-V工作小組制定並提交RISC-V基金會投票通過才能成為正式指令級擴充套件。RISC-V工作小組的成員必須是RISC-V基金會會員(會員公司的職員),同時小組的組長必須是一個黃金級別的RISC-V會員。在2017年,RISC-V有一個工作小組專門制定位操作指令集擴充套件(B extension)。但是在工作小組能正式提出草案之前,小組組長所在的公司退出了RISC-V基金會,而其他的小組成員都不是黃金會員,導致工作小組被迫關閉。現在,曾經的小組成員,Clifford Wolf,將工作小組原有的草案歸納整理,放在了GitHub上,提供給所有人。

市場相關

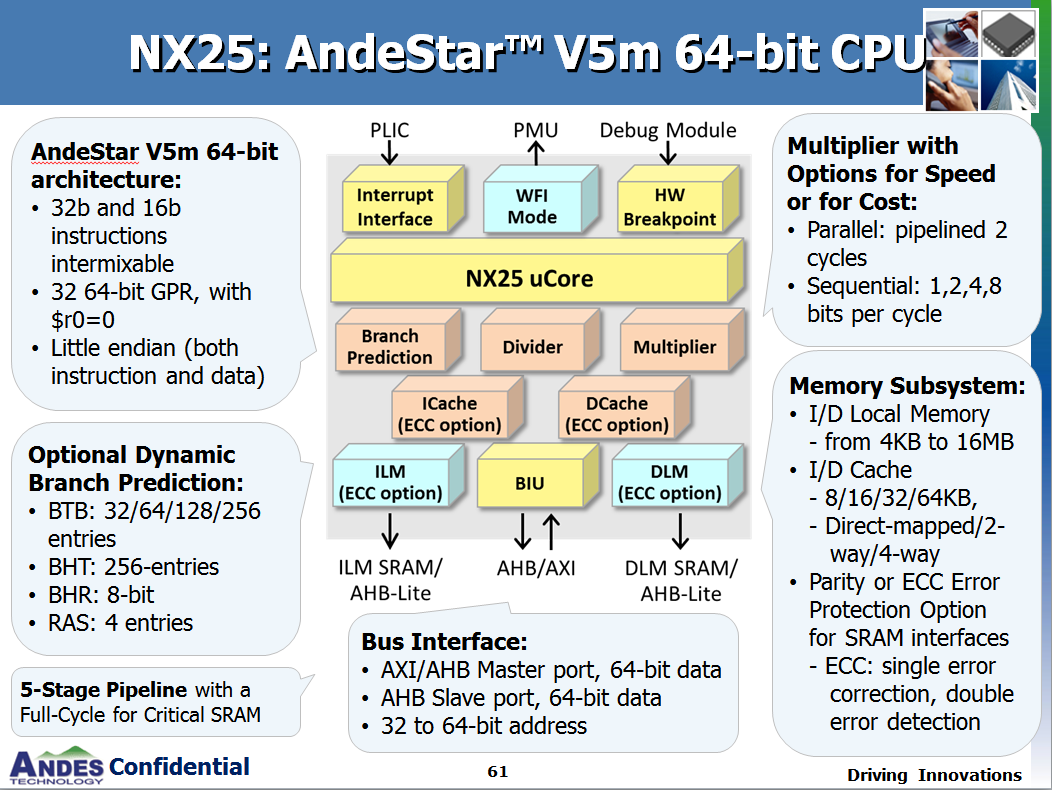

晶心科技(AndesTech)釋出其64-bit RISC-V CPU

晶心科技最近將其32-bit RISC-V CPU升級為了64-bit,也就是NX25。我們可以來看看這個CPU的引數。

- AndesStar V5m 64位架構

- 設計哲學:面向大資料的高速且緊湊的核心

- 5級流水線架構

- 動態分支預測

- 支援本地儲存和Cache

- 支援AMBA AXI/AHB協議

- JTAG除錯模組,支援Exception Redirection

- 一些AndesTech特有的技術:CoDense, StackSafe和PowerBrake

- PLIC中斷控制器

效能指標:

- NX25 (64-bit)

- 3.20 DMIPS/MHz

- 3.45 Coremark/MHz

- 63K Gates

- Freq: 1GHz

- 0.043mm2 @ T28HPC

- N25 (32-bit)

- 2.86 DMIPS/MHz

- 3.48 Coremark/MHz

- 37K Gates

- Freq: 1GHz

- 0.026mm2 @ T28HPC

(圖片已獲AndesTech授權)

他們最近在國內會舉辦蹭吃蹭喝會,歡迎參加。

SiFive成功融資C輪5000萬美元

SiFive的U540晶片流片成功,這對投資人來說應該是最好的證明,其最近成功的融資了5000萬美元,相關的新聞可以說是鋪天蓋地了。

值得注意的是,SiFive的新投資人中,還包含兩家中國投資機構。

投資人列表:

- Sutter Hill Ventures

- Spark Capital

- Osage University Partners

- Chengwei Capital(成為資本)

戰略投資者:

- Huami(華米)

- SK Telecom

- Western Digital

Links:

SiFive加入Automotive Grade Linux (AGL) Project

Automotive Grade Linux (AGL) 是一個Linux基金會下屬的專案,短期內希望提供一個開放的用於車內娛樂系統的作業系統,而長期內希望能夠成為面向車聯網和無人駕駛的作業系統。豐田、本田、馬自達、日產、富士、三菱、福特和捷豹路虎都參與了專案。

SiFive最近也加入了這個專案,這不得不讓我們期待RISC-V能在汽車領域大顯伸手。

據稱三星在其5G RF晶片中使用RISC-V CPU

一位三星員工似乎在Linkedin上洩漏了三星正在開發中的專案,當中包含為其下一代5G RF晶片中使用的RISC-V處理器的驗證工作(目前已經刪除)。

一些外行可能會認為三星會用RISC-V代替其手機晶片中的應用處理器(AP)。小編的看法是做AP不是那麼容易的事情,至少在這顆5G RF Chip中的RISC-V處理器更有可能是一個MCU級別的CPU,而不是一個能夠替代ARM Cortex-A系列的CPU。

PS: 這個故事告訴我們,在Linkedin上炫耀自己做了什麼是要付出代價的。

Link: 截圖連結

行業視角

《連線:用開源設計構建更加專用的晶片》

連線雜誌的最新文章《Using Open Source Designs to Create More Specialized Chips》講到了RISC-V所帶來的一些變革。

David Patterson提到: RISC-V能夠讓幾乎所有人來共同參與去解決那些棘手的問題(比如Specture)。另外,那些私有的ISA的問題之一是,如果你想改進設計,你面對的是一家公司。Spectre問題對於計算機體系結構來說一個高難度的挑戰,我們需要每個人的參與。

David Patterson, a computer architecture pioneer and vice chair of the board of the RISC-V Foundation, hopes RISC-V will lead to the creation of faster, more efficient, and more secure chips. Chip makers could, for example, collaborate to solve sticky problems like Spectre, the nightmarish security flaw that affects virtually all computer and smartphone chips. “The problem with proprietary architectures is that you have to work for the company, whether that’s Intel, AMD, or Arm, if you want to improve on the designs,” Patterson says. “The Spectre problem is a difficult challenge in computer architecture, what we need is everyone working on it.”

同時,Dave也提到了當前隨著AI的興起,定製話硬體的趨勢。

Patterson thinks RISC-V will be useful in creating more specialized types of chips, as opposed to the one-size-fits-all central processing units made by companies like Intel. Specialized chips aren’t new—Nvidia has been selling specialized graphics chips since the 1990s—but the idea has taken off in recent years as companies explore artificial intelligence and try to pack more computational power into everything from cars to barbecue grills. For example, Google uses its “Tensor Processing Units” (TPUs) in its data centers, and its Pixel 2 phone contains a custom chip called the Visual Core that powers the gadget’s camera.

Embedded Computing Design: RISC-V Arrives

Embedded Computing Design的最新文章《RISC-V Arrives》,作者非常深刻的剖析了這個行業!

A year or two ago it might have been easy to pass over RISC-V as an academic project with little real-world relevance, but this is no longer the case. While some industry analysts caution that there is still a long road with a lot of remaining work ahead, the question of the day is not whether RISC-V will take its place alongside the likes of ARM and x86, but rather how thoroughly the ISA will shake-up the processor market.

一兩年前,RISC-V可能很容易被認為是一個與沒什麼實用價值的學術專案,但現在情況已經不同了。或許一些業內分析師表示其仍然有很長的路要走,但當前大家關注的問題已經不再是RISC-V是否會取代ARM和x86之類的地位,而是RISC-V將會以何種方式徹底的改變處理器市場。

There is good reason to believe that the shake-up will be fairly thorough. Core tenets of the RISC-V value proposition include the notions that (1) the art of instruction set design has matured, with diminishing returns from minor differentiation, and (2) industry players have more to gain leveraging a common ISA with proven implementations and robust tools than they do pursuing custom designs for which they must do all the heavy lifting themselves. From embedded controllers to multi-core server processors, every successful RISC-V implementation strengthens that underlying value proposition. As vendors continue to face increasing complexity demands coupled with increasing design costs, it appears that an open ISA is an idea whose time has come.

有充分的理由讓我們相信這次的變革(shake-up)會相當徹底。 RISC-V的核心價值主張包括:(1)指令集設計方法已經成熟,微小的差異帶來的收益遞減;(2)行業參與者會更多地利用通用的ISA和經過驗證的強大的工具,而非追求從頭開始做定製設計,因為那樣的話他們會面臨巨大的工作量。從MCU到資料中心中的多核處理器,每一個成功的RISC-V案例都可以強化潛在的價值主張。隨著供應商不斷面臨越來越複雜的需求以及不斷增加的設計成本,開放ISA似乎是一個水到渠成想法。

暴走事件

五月

- 8th RISC-V workshop 第八次RISC-V workshop將在5月7-10日在西班牙舉辦。

六月

-

CNRV的成員和愛好者們正在RISC-V基金會的支援下籌備一場線下活動,時間暫定為2018年6月30日,目前暫定在復旦大學舉行。有任何建議、意見和想法,都可以發郵件給群頭 [email protected]。

-

2nd CARRV 第二次CARRV workshop(Computer Architecture Research with RISC-V ) 將在6月2日和ISCA 2018共同舉辦。

招聘簡訊

CNRV提供為行業公司提供公益性質的一句話的招聘資訊釋出,若有任何體系結構、IC設計、軟體開發的招聘資訊,歡迎聯絡我們!

整理編集: 宋威、黃柏瑋、郭雄飛

歡迎關注微信公眾號CNRV,接收最新最時尚的RISC-V訊息!