Xilinx Altera FPGA中的邏輯資源(Slices VS LE)比較

經常有朋友會問我,“我這個方案是用A家的FPGA還是X家的FPGA呢?他們的容量夠不夠呢?他們的容量怎麼比較呢?”當然,在大部分時候,我在給客戶做設計的時候,直接會用到最高容量的產品,因為我們的產品對成本不敏感。不過,在此還是比較一下兩家的產品,簡單寫寫一些自己的想法,供大家參考,如有不對的地方,還請指正!

進入正題

要比較Xilinx和Altera的FPGA,就要清楚兩個大廠FPGA的結構,由於各自設計的不同,兩家的FPGA結構各不相同,引數也各不相同,但可以統一到LUT(Look-Up-Table)查詢表上。

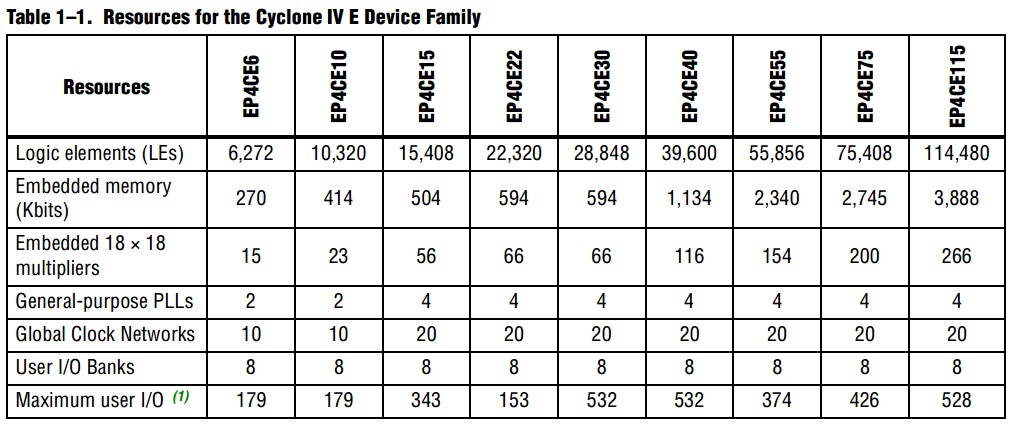

下圖就是A家的Cyclone IV系列片子的引數:

可以看到,A家的片子,用的是LE這個術語。

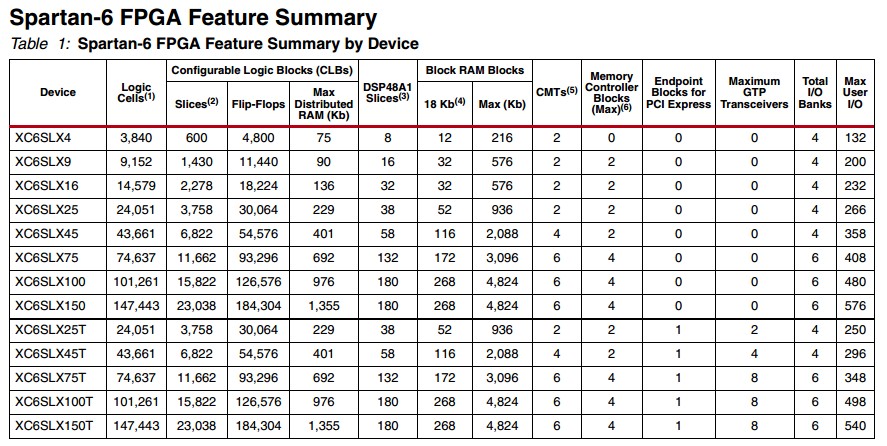

而下圖是X家的Spartan-6 片子資料:

X家用的是CLB這個術語作為基本單元。

再看看兩家的基本單元有何不同:

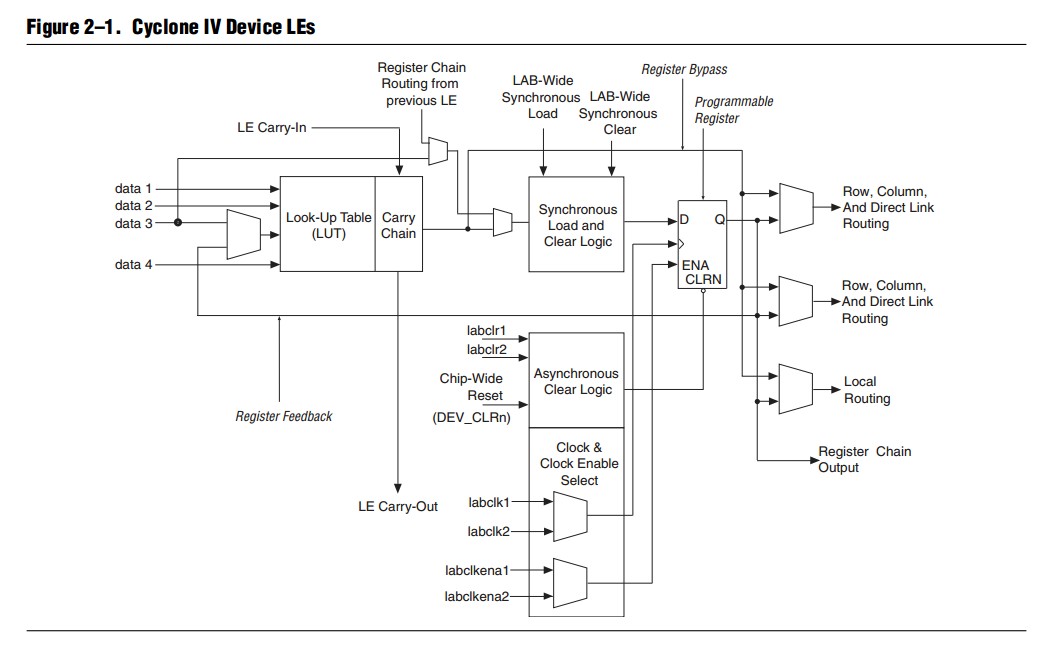

A家的LE如下圖:

就是一個4輸入LUT+FF構成

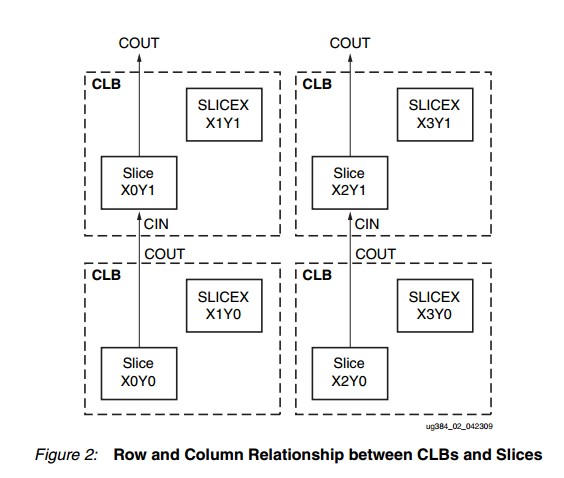

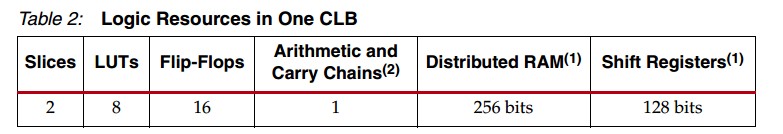

而X家的CLB如下:

一個CLB由2個SLICE構成,一個SLICE含有4個6輸入LUT,所以LUT=8*CLB。

這樣的話,可以較比一下。EP4CE6基本就和XC6SLX9一個級別。。。。當然A家的片子是4輸入LUT遠比不上X家的6輸入LUT。而X家的S-6片子,一個Slice內部有4個lut,8個FF。簡而言之,一個Slice=四個LE。要注意的是A家C5以下的片子是4輸入LUT而X家的是6輸入LUT,差別也較大。如果不考慮FF,那麼一個X家的slice=4個A家的LE。例如XC6SLX16含有2278個slices=EP4CE10(9000LE)的樣子。當然,S-6的FF多一倍,達到了18224個。

在Virtex-5中(我們的設計大部分是Virtex,V5V6V7),一個Slice包含了4個LUT和4個FF。所以單純從邏輯資源來看,S-6一個Slice比V-5的Slice強。當然V5的GTPGTX等等還有IO數量是S-6趕不上的。當然,A家的Cyclone V系列的片子,內部和前幾代完全不同,採用了從高階的Stratix系列下放的技術,在新設計時,值得推薦~!