FPGA基礎知識26(xilinx 高速收發器系列:Xilinx 7 系列的時鐘資源(3))

阿新 • • 發佈:2019-02-13

隨著高速互聯應用增多,FPGA的高速介面提供了很多互聯介面,如DP、SRIO、PCI-E等。這些協議實現的基礎都是FPGA底層的高速硬核,GTP、GTX、GTH等。本小結關注一下xilinx為高速IO提供的時鐘資源有哪些。

提到高速IO的時鐘,我們首先看一下參考時鐘,大家都知道參考時鐘的抖動指標對HSIO的可靠性影響很大,請看一下手冊對時鐘的要求:

GTX的時鐘結構,xilinx FPGA每個Q都包含4對收發器;每個Q共用一個QPLL,每兩對收發器都包含一個CPLL。這裡需要注意,如果是Aritx 7 ,則沒有Qpll。7系列的參考時鐘引入還是比較靈活的,好處在於可以使得收發工作在不同的線速率。

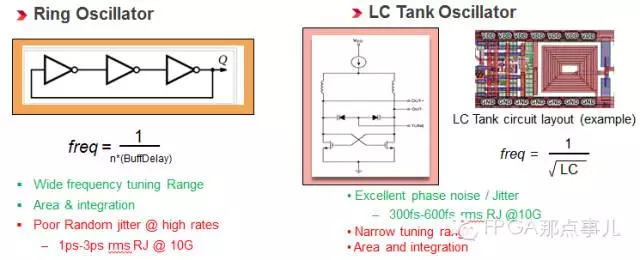

在時鐘拓撲結構上,Qpll是LC tank,而Cpll是ring;所以儘量使用Qpll,圖3是對比:

Vivado中時鐘頻率選擇:

- 參考時鐘可以選擇不同頻率;

- 可以使用不同的鎖相環;

- 可以獨立的開啟 or 關閉 RX TX;

- 可以選擇連線不同的參考時鐘管腳;

關於理解HSIO的時鐘域,下圖比較清晰的給出了TX端;

- 參考時鐘的從管腳引入;

- TXOUTCLK :這是比較重要的時鐘,用於驅動FPGA的邏輯,讀取data到高速模組中;

- PMA有獨立的時鐘域,這裡根據使用者是否使用TX buffer時鐘選擇不同;

- 參考時鐘源的mux,可以選擇上下Q的參考時鐘,根據應用不同;

另外很多工程師發現還有個DRP時鐘,這個時鐘主要用於線上配置更改屬性的;

舉例:GTX可以工作在不同線速率,使用者可能需要通過更改內部屬性來實現,這就需要DRP時鐘了。

所以在手冊最後面會看到DRP對應的地址,位寬,值等;