RS485晶片介紹及典型應用電路

一、RS485基本知識

RS-485介面晶片已廣泛應用於工業控制、儀器、儀表、多媒體網路、機電一體化產品等諸多領域。可用於RS-485介面的晶片種類也越來越多。如何在種類繁多的介面晶片中找到最合適的晶片,是擺在每一個使用者面前的一個問題。RS-485介面在不同的使用場合,對晶片的要求和使用方法也有所不同。使用者在晶片的選型和電路的設計上應考慮哪些因素,由於某些晶片的固有特性,通訊中有些故障甚至還需要在軟體上作相應調整,如此等等。希望本文對解決RS-485介面的某些常見問題有所幫助。

傳輸方式:差分

傳輸介質:雙絞線

標準節點數:32

最遠通訊距離:1200m 共模電壓最大、最小值:+12V;-7V

差分輸入範圍:-7V~+12V

接收器輸入靈敏度:±200mV

接收器輸入阻抗:≥12kΩ

2 節點數及半雙工和全雙工通訊

2.1 節點數

所謂節點數,即每個RS-485介面晶片的驅動器能驅動多少個標準RS-485負載。根據規定,標準RS-485介面的輸入阻抗為≥12kΩ,相應的標準驅動節點數為32。為適應更多節點的通訊場合,有些晶片的輸入阻抗設計成1/2負載(≥24kΩ)、1/4負載(≥48kΩ)甚至1/8負載(≥96kΩ),相應的節點數可增加到64、128和256。表1為一些常見晶片的節點數。

表1

節點數 型 號

2.2 半雙工和全雙工

(a)半雙工通訊電路

(b)全雙工通訊電路

3 應用中的常見問題

3.1 抗雷擊和抗靜電衝擊

RS-485介面晶片在使用、焊接或裝置的運輸途中都有可能受到靜電的衝擊而損壞。在傳輸線架設於戶外的使用場合,介面晶片乃至整個系統還有可能遭致雷電的襲擊。選用抗靜電或抗雷擊的晶片可有效避免此類損失,常見的晶片有MAX485E、MAX487E、MAX1487E等。特別值得一提的是SN75LBC184,它不但能抗雷電的衝擊而且能承受高達8kV的靜電放電衝擊,是目前市場上不可多得的一款產品。

3.2 限斜率驅動

由於訊號在傳輸過程中會產生電磁干擾和終端反射,使有效訊號和無效訊號在傳輸線上相互迭加,嚴重時會使通訊無法正常進行。為解決這一問題,某些晶片的驅動器設計成限斜率方式,使輸出訊號邊沿不要過陡,以不致於在傳輸線上產生過多的高頻分量,從而有效地扼制干擾的產生。如MAX487、SN75LBC184等都具有此功能。

3.3 故障保護

故障保護技術是近兩年產生的,一些新的RS-485晶片都採用了此項技術,如SN75276、MAX3080~MAX3089。什麼是故障保護,為什麼要有故障保護,如果沒有故障保護會產生什麼後果?

眾所周知,RS-485介面採用的是一種差分傳輸方式,各節點之間的通訊都是通過一對(半雙工)或兩對(全雙工)雙絞線作為傳輸介質。根據RS-485的標準規定,接收器的接收靈敏度為±200mV,即接收端的差分電壓大於、等於+200 mV時,接收器輸出為高電平;小於、等於-200mV時,接收器輸出為低電平;介於±200mV之間時,接收器輸出為不確定狀態。在匯流排空閒即傳輸線上所有節點都為接收狀態以及在傳輸線開路或短路故障時,若不採取特殊措施,則接收器可能輸出高電平也可能輸出低電平。一旦某個節點的接收器產生低電平就會使序列接收器(UART)找不到起始位,從而引起通訊異常,解決此類問題的方法有兩種:

(1)使用帶故障保護的晶片,它會在匯流排開路、短路和空閒情況下,使接收器的輸出為高電平。確保匯流排空閒、短路時接收器輸出高電平是由改變接收器輸入門限來實現的。例如,MAX3080~MAX 3089輸入靈敏度為-50mV/-200mV,即差分接收器輸入電壓UA-B≥-50mV時,接收器輸出邏輯高電平;如果UA-B≤-200mV,則輸出邏輯低電平。當接收器輸入端匯流排短路或總線上所有傳送器被禁止時,接收器差分輸入端為0V,從而使接收器輸出高電平。同理,SN75276的靈敏度為0mV/-300mV,因而達到故障保護的目的。

(2)若使用不帶故障保護的晶片,如SN75176、MAX1487等時,可在軟體上作一些處理,從而避免通訊異常。即在進入正常的資料通訊之前,由主機預先將匯流排驅動為大於+200mV,並保持一段時間,使所有節點的接收器產生高電平輸出。這樣,在發出有效資料時,所有接收器能夠正確地接收到起始位,進而接收到完整的資料。

3.4 光電隔離

在某些工業控制領域,由於現場情況十分複雜,充分考慮現場的複雜環境,在電路設計中注意了以下三個問題。 二、RS485應用設計 1 SN75176 485晶片DE控制端的設計 由於應用系統中,主機與分機相隔較遠,通訊線路的總長度往往超過400米,而分機系 統上電或復位又常常不在同一個時刻完成。如果在此時某個75176的DE端電位為“1”,那 麼它的485匯流排輸出將會處於傳送狀態,也就是佔用了通訊匯流排,這樣其它的分機就無法與 主機進行通訊。這種情況尤其表現在某個分機出現異常情況下(宕機),會使整個系統通訊 崩潰。因此在電路設計時,應保證系統上電覆位時75176的DE端電位為“0”。由於8031在復 位期間,I/O口輸出高電平,故圖2電路的接法有效地解決復位期間分機“咬”匯流排的問題。 2 隔離光耦電路的引數選取 在應用系統中,由於要對現場情況進行實時監控及響應,通訊資料的波特率往往做得較 高(通常都在4800波特以上)。限制通訊波特率提高的“瓶頸”,並不是現場的導線(現場 施工一般使用5類非遮蔽的雙絞線),而是在與微控制器系統進行訊號隔離的光耦電路上。此 處採用TIL117。電路設計中可以考慮採用高速光耦,如6N137、6N136等晶片,也可以優化普 通光耦電路引數的設計,使之能工作在最佳狀態。例如:電阻R2、R3如果選取得較大,將會 使光耦的發光管由截止進入飽和變得較慢;如果選取得過小,退出飽和也會很慢,所以這兩 只電阻的數值要精心選取,不同型號的光耦及驅動電路使得這兩個電阻的數值略有差異,這 一點在電路設計中要特別慎重,不能隨意,通常可以由實驗來定。 3 485匯流排輸出電路部分的設計 輸出電路的設計要充分考慮到線路上的各種干擾及線路特性阻抗的匹配。由於工程環境 比較複雜,現場常有各種形式的干擾源,所以485匯流排的傳輸端一定要加有保護措施。在電 路設計中採用穩壓管D1、D2組成的吸收回路,也可以選用能夠抗浪湧的TVS瞬態雜波抑制器 件,或者直接選用能抗雷擊的485晶片(如SN75LBC184等)。 考慮到線路的特殊情況(如某一臺分機的485晶片被擊穿短路),為防止匯流排中其它分 機的通訊受到影響,在75176的485訊號輸出端串聯了兩個20Ω的電阻R10、R11。這樣本機的 硬體故障就不會使整個匯流排的通訊受到影響。 在應用系統工程的現場施工中,由於通訊載體是雙絞線,它的特性阻抗為120Ω左右, 所以線路設計時,在RS-485網路傳輸線的始端和末端各應接1只120Ω的匹配電阻(如圖1中 R8),以減少線路上傳輸訊號的反射。 由於RS-485晶片的特性,接收器的檢測靈敏度為± 200mV,即差分輸入端VA-VB ≥ +200mV,輸出邏輯1,VA-VB ≤-200mV,輸出邏輯0;而A、B端電位差的絕對值小於200mV 時,輸出為不確定。如果在總線上所有傳送器被禁止時,接收器輸出邏輯0,這會誤認為通 信幀的起始引起工作不正常。解決這個問題的辦法是人為地使A端電位高於B兩端電位,這樣 RXD的電平在485匯流排不傳送期間(匯流排懸浮時)呈現唯一的高電平,8031微控制器就不會被誤 中斷而收到亂字元。通過在485電路的A、B輸出端加接上拉、下拉電阻R7、R9,即可很好地 解決這個問題。

三、軟體的程式設計 485晶片的軟體程式設計對產品的可靠性也有很大影響。由於485匯流排是非同步半雙工的通訊總 線,在某一個時刻,匯流排只可能呈現一種狀態,所以這種方式一般適用於主機對分機的查詢 方式通訊,總線上必然有一臺始終處於主機地位的裝置在巡檢其它的分機,所以需要制定一 套合理的通訊協議來協調匯流排的分時共用。這裡採用的是資料包通訊方式。通訊資料是成幀 成包傳送的,每包資料都有引導碼、長度碼、地址碼、命令碼、內容、校驗碼等部分組成。 其中引導碼是用於同步每一包資料的引導頭;長度碼是這一包資料的總長度;命令碼是主機 對分機(或分機應答主機)的控制命令;地址碼是分機的本機地址號;“內容”是這一包數 據裡的各種資訊;校驗碼是這一包資料的校驗標誌,可以採用奇偶校驗、和校驗等不同的方 式。 在485晶片的通訊中,尤其要注意對485控制端DE的軟體程式設計。為了可靠的工作,在485 匯流排狀態切換時需要做適當延時,再進行資料的收發。具體的做法是在資料傳送狀態下,先 將控制端置“1”,延時1ms左右的時間,再發送有效的資料,一包資料傳送結束後再延時 1ms後,將控制端置“0”。這樣的處理會使匯流排在狀態切換時,有一個穩定的工作過程。

三種常用電路如下:

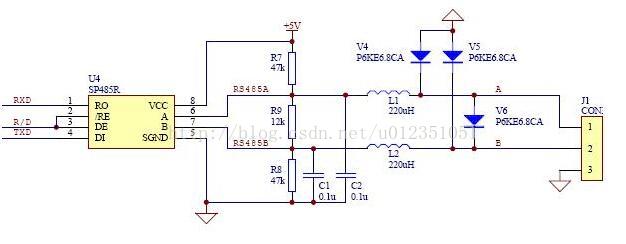

1、基本的RS485電路

上圖是最基本的RS485電路,R/D為低電平時,傳送禁止,接收有效,R/D為高電平時,則傳送有效,接收截止。上拉電阻R7和下拉電阻R8,用於保證無連線的SP485R晶片處於空閒狀態,提供網路失效保護,提高RS485節點與網路的可靠性,R7,R8,R9這三個電阻,需要根據實際應用改變大小,特別是使用120歐或更小的終端電阻時,R9就不需要了,此時R7,R8使用680歐電阻。正常情況下,一般R7=R8=4.7K,R9不要。

圖中鉗位於6.8V的管V4,V5,V6,都是為了保護RS485匯流排的,避免受外界干擾,也可以選擇整合的匯流排保護原件。另外圖中的L1,L2,C1,C2為可選安裝原件,用於提高電路的EMI效能.

2、帶隔離的RS485電路

根本原理與基本電路的原理相似。使用DC-DC器件可以產生1組與微處理器電路完全隔離的電源輸出,用於向RS485收發器提供+5V電源。電路中的光耦器件速率會影響RS485電路的通訊速率。上圖中選用了NEC的光耦PS2501,受其影響,該電路的通訊速率控制在19200bps下。

3、自動切換電路

上圖中,TX,RX引腳均需要上拉電阻,這一點特別重要。

接收:預設沒有資料時,TX為高電平,三極體導通,RE為低電平使能,RO收資料有效,MAX485為接收態。

傳送:傳送資料時,TX會先有一個下拉的電平(起始位-由高向低),表示開始傳送資料,此時三極體截止,DE為高電平傳送使能。當傳送資料“0”時,由於DI介面相當於接地,此時資料“0”就會傳輸到AB扣,A-B<0,則傳輸“0”,完成低電平傳輸,當傳送“1”時,此時三極體導通,按理說RO會使能,此時由於還處於傳送資料中,這種狀態下MAX485處於高阻太,此時的狀態通過A上來,B下拉電阻決定,此時A-B>0傳輸“1”,完成高電平的傳輸。

注意:這裡面有個疑惑,傳送資料“1”,三極體RE低電平有效,應該是接收使能,為什麼晶片是高阻態呢?這是因為UART傳送資料是有一定格式的,TX和RX資料均以“位”為最小單位進行傳輸,在傳送資料之前,UART之間要約定好資料傳輸速率,即波特率,資料傳輸格式(資料位,校驗,停止),平時資料線處於空閒狀態(1狀態),當傳送資料時,TX由“1”變為“0”維持1位的時間,這樣接收方檢測到開始位後,再等待1.5位時間就開始一位一位的進行資料傳輸了,也就是說,已經確定好傳送狀態,電路傳送“1”時RE雖然有效,但是由於它處於傳送階段,晶片也不會收,即晶片處於高阻狀態。