FPGA系統設計的模擬驗證

最近做專案卡住了,模擬已經通過了,可是將程式下載到板子除錯時,chipscope中獲取訊號時,所有訊號一直保持高或者低,沒有任何變化。後來查資料知道,我只做了功能模擬,沒有做時序模擬,可能還有沒有發現的問題。事實證明,每個模擬都需要做。

一、前言

FPGA設計驗證包括功能與時序模擬和電路驗證。

功能模擬是指僅對邏輯功能進行測試模擬,以瞭解其實現的功能是否滿足原設計的要求。模擬過程中沒有加入時序資訊,不涉及具體器件的硬體特性,如延時特性等,因此也叫前模擬。它是對HDL硬體設計語言的功能實現能力進行模擬,以確保HDL語言描述能夠滿足設計者的最初意圖。

時序模擬則是在HDL可以滿足設計者功能要求的基礎上,在佈局佈線後,提取有關的器件延遲、連線延時等時序引數,並在此基礎上進行的模擬,因此,也稱為後模擬,它是接近真實器件執行的模擬。

我使用的是ISE_14.7,整合MODELSIM_10.1a。模擬的方法分為直接和間接兩種。直接是指從ISE 上起動MODELSIM。間接是單獨起動MODELSIM,然後使用ISE 生成的用於模擬的資料夾netgen。

下面分別介紹功能模擬和時序模擬,本文只介紹直接從ISE上啟動MODELSIM。本文參考的例項為之前的博文《verilog實現中值濾波》。

二、功能模擬

1、建立工程

此步驟不再詳細描述,可參考檔案《黑金Sparten6開發板Verilog教程V1.5》第四部分 LED流水燈例程。該部分詳細介紹從新建一個專案, 建立模擬檔案,從ISE中啟動ModelSim進行功能模擬以及到最後下載到FPGA的全過程。像我這樣的小白可以通過學習這部分,對如何使用FPGA進行一個簡易專案的開發,有個直面的感性認識。

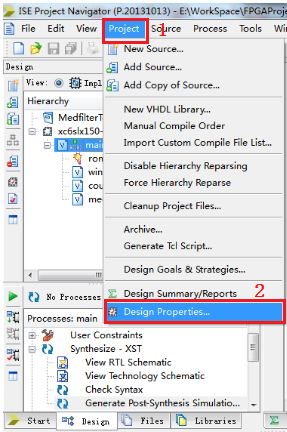

2、在用Modelsim模擬前,在ISE中需要確認一下設定,點選選單的“Project->Design Properties…”。

3、如下圖所示,確認這裡“Simulator”的選擇為“Modelsim-SE Mixed”,這在新建工程時我們已經設定好了,為保萬無一失,我們還是確認一下。

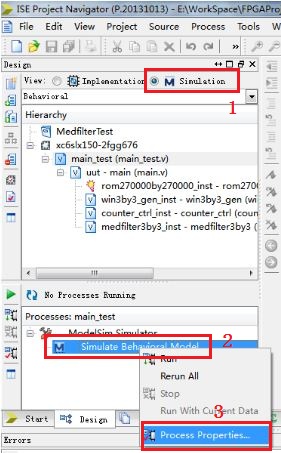

4、先切換到Simulation模式, 再選中main_test.v檔案, 最後右鍵選擇Simulate Behavioral Model後選擇Process Properties..。

5、彈出“Process Properties”設定視窗,在右邊的“Compiled Library Directory”後面填入之前編譯庫時設定的已編譯庫的路徑“C:\Xilinx\Xilinx_lib”。這個在Xilinx的安裝路徑下。其他選項預設設定即可,點選“OK” 完成設定。

6、接下去我們開始寫測試指令碼檔案,右擊main.v->New Source...

7、如圖所示,選擇新建原始檔型別是“Verilog Test Fixture”,再輸入測試指令碼檔案的名字和存放目錄。

8、這裡“Associate Source”是選擇測試指令碼對應的設計原始檔,如果工程中有多個設計原始檔,可以選擇任意一個設計原始檔進行模擬。這裡我選擇的是頂層模組的設計原始檔main.v,對整個工程進行模擬我們只有一個設計原始檔,然後點選“Next”。下一個介面點選“finish”,即完成模擬檔案的建立。

9、這裡的測試指令碼只是一個基本的模板,它把設計檔案mian_test的介面在這個模組裡面例化申明瞭,我們還需要自動動手新增復位和時鐘的激勵。完成後的指令碼檔案如下:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 16:45:09 10/17/2018

// Design Name: main

// Module Name: E:/WorkSpace/FPGAProject/ImageProcessingTest/main_test.v

// Project Name: ImageProcessingTest

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: main

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module main_test;

/***輸入埠Inputs在測試檔案中的資料型別為reg***/

// Inputs

reg CLK;

reg RSTn;

reg Start_sig;

/***定義計數器,記錄儲存的畫素個數100*100=10000=10,0000,0000,0000***/

reg [13:0] pix_cnt;

/***輸出埠Outputs在測試檔案中的資料型別為wire***/

// Outputs

wire Done_sig;

wire [7:0] Data_out;

/***定義整型變數fouti***/

integer fouti;

// Instantiate the Unit Under Test (UUT)

main uut (

.CLK(CLK),

.RSTn(RSTn),

.Start_sig(Start_sig),

.Done_sig(Done_sig),

.Data_out(Data_out)

);

initial begin

// Initialize Inputs

CLK = 0;

RSTn = 0;

Start_sig = 0;

fouti = $fopen("medfilter2_re.txt");//@@@

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

/***新增復位資訊***/

RSTn = 0;

Start_sig = 1;

pix_cnt = 0;

#100;

// To start the syste

RSTn = 1;

pix_cnt = 1;

end

/***新增時鐘激勵***/

always #10 CLK = ~CLK;

/***計數***/

[email protected](posedge CLK)

begin

if(Done_sig)

pix_cnt <= pix_cnt + 1;

end

/***通過計數停止模擬***/

[email protected](posedge CLK)

begin

if(pix_cnt == 14'd10001)

begin

Start_sig <= 0;

$display("Image Medfilter Completed!\n");

$display("The all time is %d \n",$time);

$stop;

end

end

/***將結果資料Data_out寫入txt文件中***/

[email protected](posedge CLK)

begin

if(Done_sig)

begin

$fwrite(fouti, "%d", Data_out, "\n");

$display("%d",pix_cnt);

end

end

endmodule10、儲存後main_test.v已經成了這個模擬的頂層了,它下面是設計檔案main.v。我們選擇模擬模式Behavioral(行為模擬),然後選中main_test.v檔案,隨後雙擊“Simulation Behavioral Model”,隨後Modelsim將被呼叫,啟動模擬。

11、彈出Modelsim後,我們可以開啟Wave檢視。如果想新增訊號到Wave中檢視,點選uut,在Name視窗下選擇要新增的訊號,例如rom_data,右擊選擇Add Wave,隨後就可以在Wave視窗中觀察rom_data訊號。

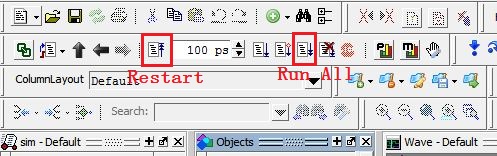

12、點選Restart按鈕復位一下,再點選Run All按鈕。Modelsim會執行到$stop的地方。

補充:每次新增訊號比較麻煩,可以點選“save Format”, 將新增好的訊號儲存,方便下次使用。

點選"File",選擇"Open",開啟檔案“wave.do”。如下圖所示。

在“wave.do”檔案中,複製下圖藍色部分的語句,在命令列視窗執行這些語句,即可將之前儲存的訊號新增到wave視窗中。

三、時序模擬

時序模擬一共有四類:

第一類:綜合(Synthesize),綜合後可生成綜合後模擬模型(Generate Post-Synthesis Simulation Model)。

在Implementation狀態下,點選Synthesize-XST下Generate Post-Synthesis Simulation Model。

第二類:實現(Implement)中的翻譯(Translate),生成Generate Post-Translate Simulation Model。

第三類:實現(Implement)中的對映(Map),生成Generate Post-Map Simulation Model。

第四類:實現(Implement)中的佈局佈線(Place&Route),生成Generate Post-Place&Route Simulation Model。

綜合後,進行ISE的實現(Implement),包括翻譯、對映、佈局佈線。在這三個過程中都可以生成一個模擬模型,翻譯和對映不會產生延時,因此常用佈局佈線後產生的模擬模型進行時序模擬。下面講解如何使用佈局佈線後產生的模擬模型進行時序模擬。

1、啟動Modelsim模擬

生成模擬模型之後,切換到"Simulation"模式,選擇“Post-Route”,然後雙擊ModelSim Simulator下Simulate Post-Place & Route Model,隨後Modelsim啟動。

2、如何編寫模擬檔案及如何使用Modelsim觀察訊號變化,同功能模擬。

四、參考資料

1、《黑金Sparten6開發板Verilog教程V1.5》

連結:https://pan.baidu.com/s/17Ubnroqc3oNEXt_W2XkXgg

提取碼:1m7m

2、《用ISE 與Modelsim 進行FPGA 後模擬(時序模擬)的兩種方法》

連結:https://pan.baidu.com/s/1w3msgwOHQX0LIkg1nk4yqg

提取碼:bv41

3、《FPGA應用開發入門與典型案例》