ISE中chipscope的使用教程

參考文章連結:

https://blog.csdn.net/rill_zhen/article/details/8115756

http://www.cnblogs.com/liujinggang/p/9813863.html

http://www.eefocus.com/guoke1993102/blog/15-12/375730_3a621.html

一、軟體平臺

作業系統:windows 7

開發套件:ISE 14.7 ModelSim SE-64 10.1a

二、ChipScope Pro介紹

ChipScope Pro是一款線上除錯工具,片上邏輯分析儀。她的主要功能是通過JTAG口,線上實時讀取FPGA的內部訊號。

ChipScope Pro的基本原理是利用FPGA中未使用的BlockRam,根據使用者設定的觸發條件將訊號實時地儲存到這些BlockRam中,然後通過JTAG口傳送到計算機,最後在計算機螢幕上顯示出時序波形。

ChipScope Pro工作時一般需要使用者設計中例項化兩種核:一是整合邏輯分析儀核(ILA core,Integrate Logic Analyzer core),該核主要用於提供觸發核捕獲的功能;二是整合控制核(ICON core,Integrated Contorller core),負責ILA core核便捷掃描埠(JTAG)的通訊。一個ICON core可以連線1~15個ILA core。ChipScope Pro工作時,ILA core根據使用者設定的觸發條件捕獲資料,然後在ICON core控制下,通過邊界掃描埠上傳到計算機,最後用ChipScope Pro Analyzerx顯示訊號波形。

ChipScope Pro有兩種使用方法。第一種是由ChipScope Pro Core Generator根據設定條件生成線上邏輯分析儀IP核,包括ICON core、ILA core、ILA/ATC core 和IBA/OPB core等,之後在原HDL程式碼中例項化這些核,然後進行綜合、佈局佈線、下載配置檔案,就可以利用ChipScope Pro Analyzer設定的觸發條件,觀察訊號波形。

第二種是原始碼完成綜合後,由ChipScope Pro Inserter工具插入ICON core和ILA core等核,它能自動完成在設計網表中插入這些核的工作,而不用手動在HDL程式碼中例項化這些核。本文主要講解第二種方法。

三、方法二的使用流程

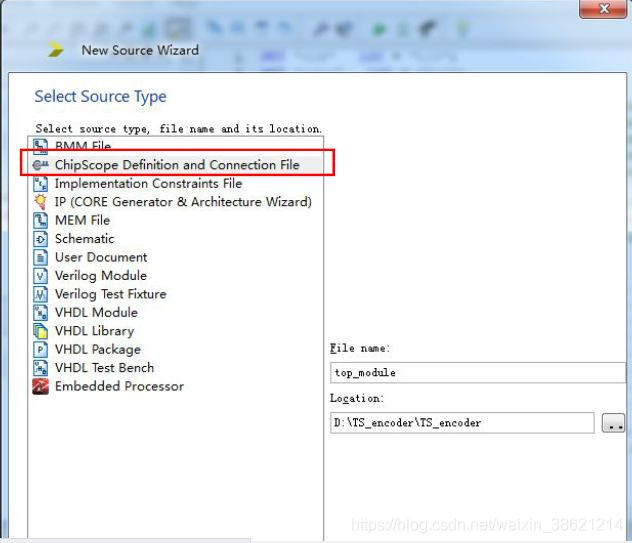

step1:new source->選擇新建一個chipscope的核

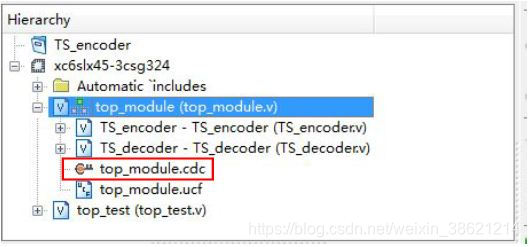

然後,可以看到在工程中有了chipscope的核.

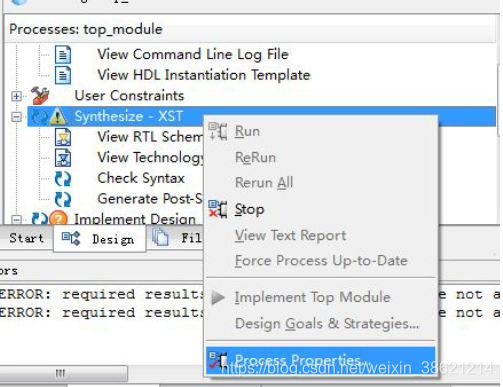

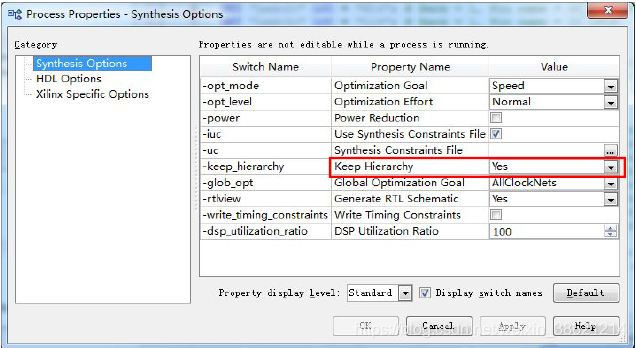

step2:開啟.cdc檔案。但在開啟它之前,有一個很重要的操作,右鍵synthesize-XST,選擇process properties.

在keep hierarchy 中選擇yes. 即設定綜合時保持層次,這樣在綜合後的電路中會保持模組化,方便我們找到所想觀察的訊號。否則,很多訊號會被優化掉,chipscope找不到想要的訊號來觀察。

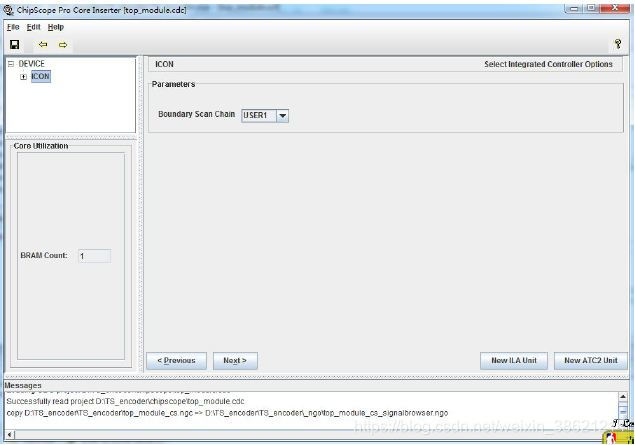

step3:設定chipscope,雙擊chipscope,會進入chipscope的操作介面,這個介面設定預設,點選next。

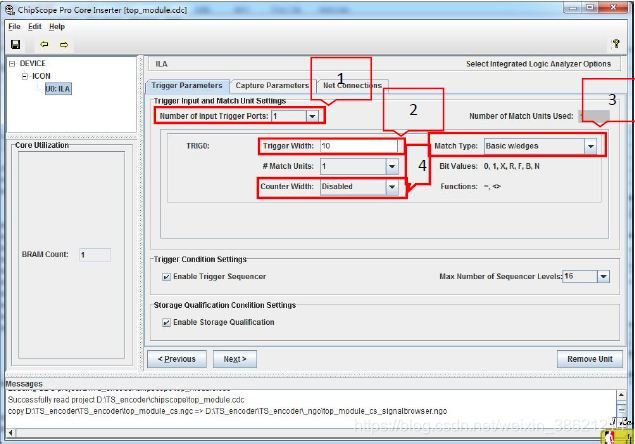

進入ILA的設定:

首先是trigger parameters:

標號1處表示觸發埠個數,而每個觸發埠又最大可以容納下256位的資料(標號2處),也就是說大部分時候,只需要1個觸發埠就夠了。但是把需要觀察的訊號分佈在幾個觸發端口裡最好,不僅僅方便新增和刪除。而且尤其對於一組匯流排訊號來說,把他們單獨放在一起,有利於觀察訊號時觸發訊號的設定(後面會提到)。

標號2處即該埠的訊號寬度,最大為256位,這裡設定的位數與後面的連結的訊號數必須相符合,因此這裡先填大一點,我一般直接寫個32位,然後根據後面連線的訊號數返回這裡修改,不然當連線訊號時發現位數不夠又要先返回這裡修改,再回去連線訊號,比較麻煩。

標號3處設定觸發條件,一般設定basic w/edges,這樣可以設定當訊號處於0,或1,或者上升,下降沿時觸發。這裡R代表上升沿,F代表下降沿,B應該代表只要發生變化就觸發,N就不太清楚了,希望知道的可以告訴我,謝謝。

標號4處是計數器的設定,即同一觸發條件發生多少次後,才開始觸發,也可以設定為disable.

之後點選next.

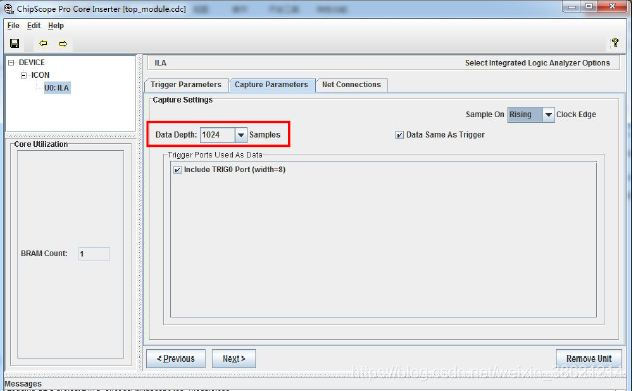

之後進入capture parameter, 這裡主要設定的是取樣深度,如果你需要一下取樣到更多的訊號,則將深度設定得大一點,當然,也更消耗資源就是。設定過多會造成FPGA的BRAM資源不足,提示錯誤。點選next。

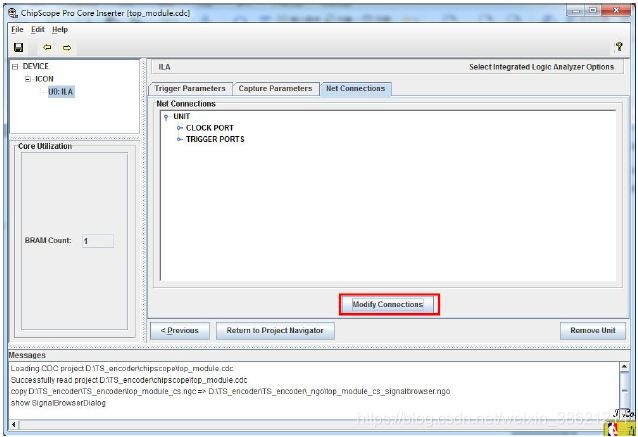

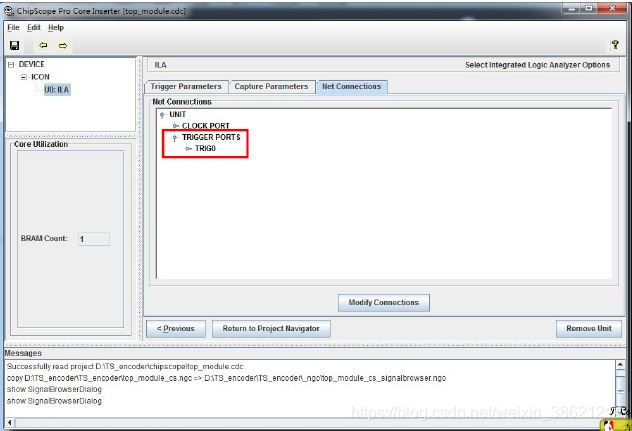

最後進入到net connections, 點選modify connections 來新增需要觀察的訊號。

進入到訊號連線介面。

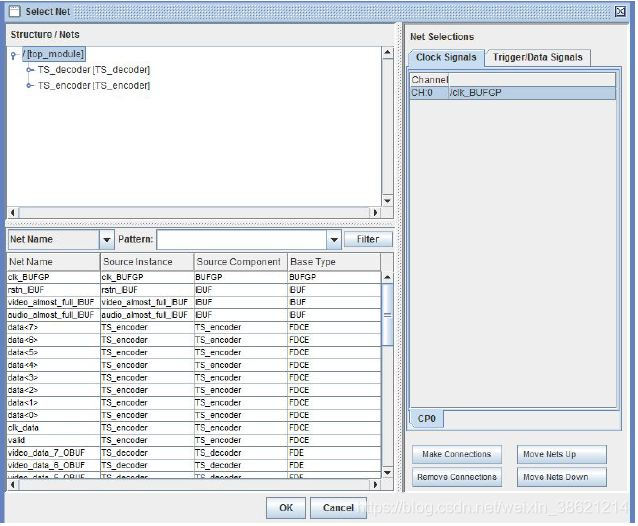

首要任務是新增取樣時鐘訊號,一般是系統時鐘,點選通道->選擇訊號->點選make connections即可。注意,這裡連線的時鐘輸入都必須是帶有buffer的訊號,否則會報錯。

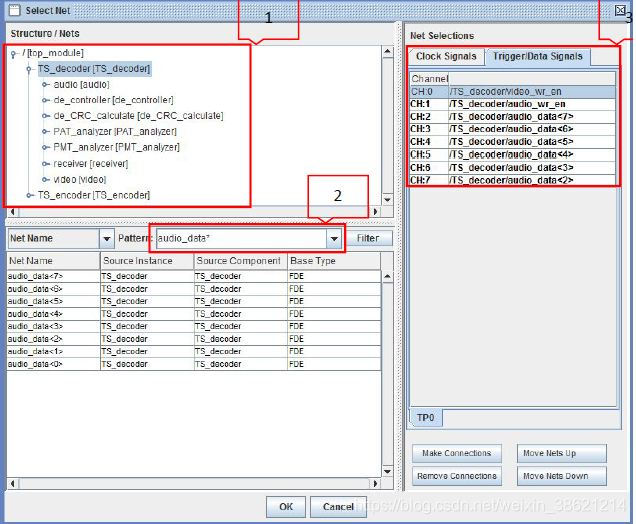

然後就是其他訊號的連線,但是這麼多訊號,如何找到自己需要的訊號呢? 一就是可以在1處選擇相應的模組,再尋找其中的訊號,這就是為什麼之前要設定保持層次的原因。

二就是可以使用的搜尋功能,在2處輸入訊號名,後面需要帶有*號!需有*號!需有*號!(重要的事說三遍),就可以找到選定模組裡的對應訊號了。

三處即為連線好的訊號。點選OK。

回到net connections. 如果連線的訊號數與之前在trigger parameters中設定的寬度相同,則trigger port是黑色的。否則為紅色,這時到trigger parameters中修改一下寬度即可。

儲存後退出。

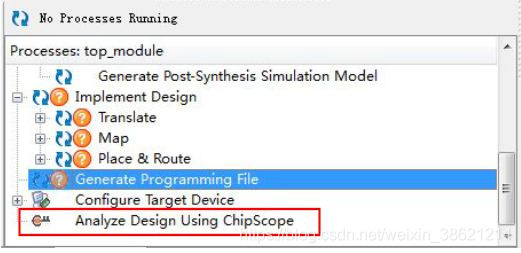

step4:生成bit檔案。等待生成完畢後,點選下面的analyze design using chipscope.

step5:點選左上角按鈕,以跟開發板建立連線:

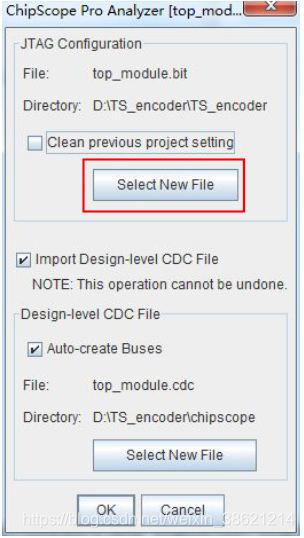

step6:連線好後,右鍵裝置名稱,點選configure……

點選select new file,選擇需要下載的bit檔案。

點選OK後,開始下載,右下角有進度條,就不貼圖了。

然後有提示的話點選確認就好。

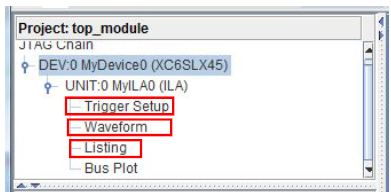

下載成功之後,軟體會自動更新下面的視窗,這時可以看到下面出現觸發埠,以及資料埠

step7:下面介紹下圖視窗

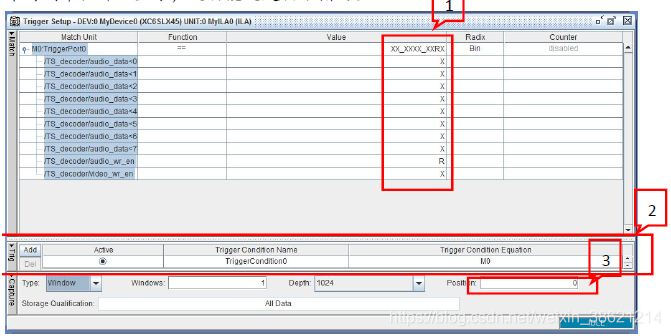

1,trigger setup, 即觸發條件設定,點開右側會出現如下視窗:

在1處設定高電平觸發,低電平觸發,上升沿觸發,下降沿觸發等,比如這裡設定的就是在audio_wr_en上升沿的時候觸發。另外,還可以設定整個觸發埠為一個值時觸發,這個對一組匯流排來說很有用,比如這裡的audio_data, 這也就是為什麼之前說把一組匯流排放在一個單獨的觸發埠比較好(這裡沒有單獨放),就是為了這裡更容易設定觸發條件。

觸發條件最好一次只設置一個,選擇自己想觀察的訊號。

一般情況下,工程較大,需要檢視的訊號過多,但是取樣深度設定的較小,這樣會導致一次觸發無法檢視所有的訊號。此時,可以選擇不同的觸發訊號,只儲存從觸發訊號開始的資料。

2處可以設定多組觸發條件,方便改變觸發條件

3處可以設定波形顯示的位置,比如設定為100,則波形從觸發條件的前100個時間單位開始顯示,這功能還是挺不錯的。

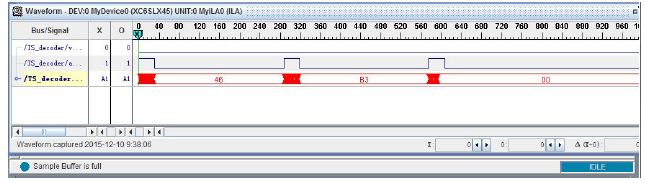

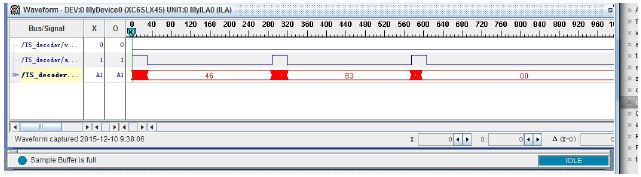

2, waveform, 波形視窗沒什麼好說的,大家應該都會用,提醒一下就是,右鍵訊號可以選擇訊號顏色,這樣方便突出重點訊號,作為一個視覺動物,我覺得這個功能還是很nice的,畢竟chipscope實在太醜了,做專案有時候也挺枯燥的。

3,listing 這是一個和waveform同等的視窗,只不過它是通過表格來顯示資料而已,因為有些資料用表格來看方便點。右鍵訊號,是可以選擇把它們新增到waveform或者listing的。而且listing中的資料還支援匯出功能,在選單欄的file中有匯出選項,支援多種格式,這個就自己慢慢去玩了。

還有一個是bus plot,就是一個座標圖,看資料與時間的關係,以及資料與資料的關係,這裡就不討論了。

瞭解到了這些東西后,設定好觸發條件,在trigger setup開啟後,上面會有一個取樣的控制檯。可以選擇單次觸發,連續觸發,實時觸發。

點選觸發開始後,一旦觸發條件滿足,就可以看到取樣到的訊號了:

四、如何防止訊號被優化

在一個複雜的設計中,我們往往會抓大量的訊號,而ISE14.7編譯程式碼的時候會把一些有相同邏輯的訊號給優化掉,這會導致我們在選擇訊號的時候找不到想要抓取的訊號,針對這種情況給大家提供兩個解決辦法。

方法一:

1、在你想要抓取的所有訊號前面加上(*KEEP = “TRUE”*)

(*KEEP = "TRUE"*)reg [3:0] R_cnt;

方法二:

上面一種方法根據我的經驗並不能100%的保證訊號不被綜合掉,所以還有另外一種方法是寫一段冗餘邏輯把訊號進行運算然後賦值給一個輸出,並把輸出引到頂層繫結一個空閒的管腳,這種情況我的處理方法是:

假設要抓取的訊號是(*KEEP = "TRUE"*)reg [3:0] R_cnt;

1、定義1個輸出訊號O_test;

Output O_test;

2、把要抓取的訊號各位相或然後賦值給O_test

assign O_test = | R_cnt ;

R_cnt前面的“|”表示把R_cnt的每一bit按位相或,這行程式碼和

assign O_test = R_cnt[0] | R_cnt[1] | R_cnt[2] ;

綜合出來的邏輯是一模一樣的

3、把O_test引到頂層並在約束檔案中分配一個空餘管腳

通過這種增加冗餘邏輯的方式,R_cnt訊號一般不會被綜合掉,我自己在平時的使用中會先使用第一種方法,如果發現第一種方法還是把我想看的關鍵訊號綜合掉了的話就採用第二種方法。