計算機系統結構考試重點:Chapter3 :ISA

什麼是指令集架構?他是如何一種方式展示的? ISA是指令的集合,直接執行於CPU的硬體上。 顯示方式:二進位制格式,因為計算機只支援二進位制的格式。 為指令、暫存器、常量、儲存器而串接的二進位制編碼。 RISC VS CISC CISC(Complex Instruction Set Computers,複雜指令集計算集)和RISC(Reduced Instruction Set Computers)是兩大類主流的CPU指令集型別,其中CISC以Intel,AMD的X86 CPU為代表,而RISC以ARM,IBM Power為代表。RISC的設計初衷針對CISC CPU複雜的弊端,選擇一些可以在單個CPU週期完成的指令,以降低CPU的複雜度,將複雜性交給編譯器。舉一個例子,CISC提供的乘法指令,呼叫時可完成記憶體a和記憶體b中的兩個數相乘,結果存入記憶體a,需要多個CPU週期才可以完成;而RISC不提供“一站式”的乘法指令,需呼叫四條單CPU週期指令完成兩數相乘:記憶體a載入到暫存器,記憶體b載入到暫存器,兩個暫存器中數相乘,暫存器結果存入記憶體a。按照此思路,早期的設計出的RISC指令集,指令數是比CISC少些,單後來,很多RISC的指令集中指令數反超了CISC,因此,引用指令的複雜度而非數量來區分兩種指令集。

當然,CISC也是要通過操作記憶體、暫存器、運算器來完成複雜指令的。它在實現時,是將複雜指令轉換成了一個微程式,微程式在製造CPU時就已儲存於微服務儲存器。一個微程式包含若干條微指令(也稱微碼),執行復雜指令時,實際上是在執行一個微程式。這也帶來兩種指令集的一個差別,微程式的執行是不可被打斷的,而RISC指令之間可以被打斷,所以理論上RISC可更快響應中斷。

在此,總結一下CISC和RISC的主要區別:

CISC的指令能力強,單多數指令使用率低卻增加了CPU的複雜度,指令是可變長格式;RISC的指令大部分為單週期指令,指令長度固定,操作暫存器,只有Load/Store操作記憶體 CISC支援多種定址方式;RISC支援方式少 CISC通過微程式控制技術實現;RISC增加了通用暫存器,硬佈線邏輯控制為主,是和採用流水線 CISC的研製週期長 RISC優化編譯,有效支援高階語言

處理器內部儲存型別(CLassifying Instrument Set Architectures by the type of internal storage in a processor)

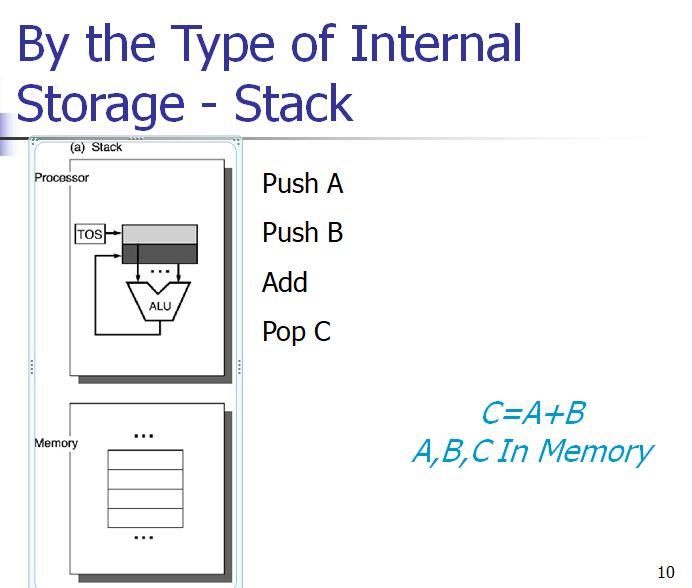

1、指令集結構型別——堆疊型

運算元A,B,C都在記憶體中。 優點:是一種表示計算的簡單模型,指令短小。 缺點:堆疊不能被隨機訪問,很難生成有效程式碼。同時,由於堆疊是瓶頸,很難被有效的實現。

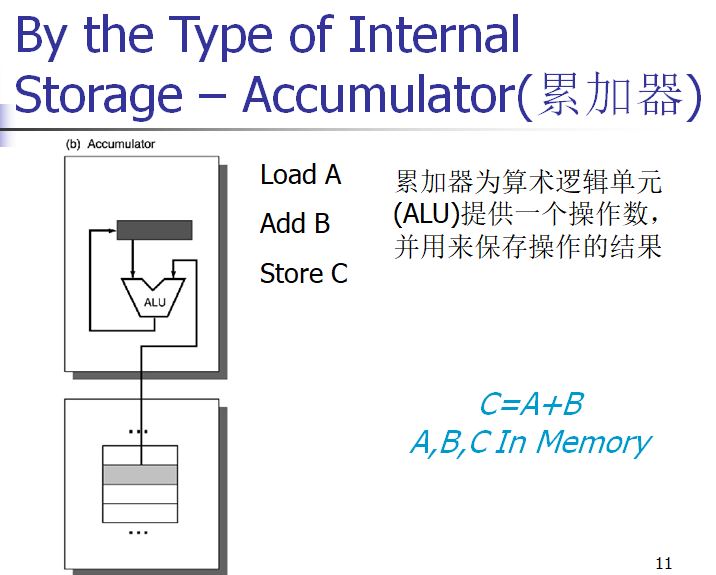

2、指令集結構型別——累加器型

運算元A,B,C都在記憶體中。把數從地址A置於累加器數存於累加器中。 優點:減小了機器的內部狀態;指令短小。 缺點:由於累加器是唯一的暫存器,這種機器的儲存器通訊開銷最大。

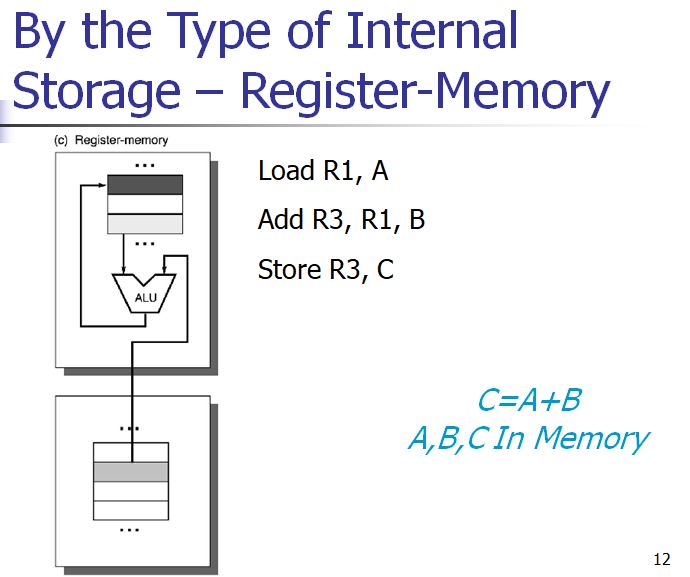

3、指令集結構型別——暫存器——記憶體型

優點:可以直接對儲存器運算元進行訪問,容易對指令進行編碼,且其目的碼較小。

缺點:指令中的運算元型別不同。在一條指令中同時對一個暫存器運算元和儲存器運算元進行編碼,將限制指令所能夠表示的暫存器個數。由於指令的運算元可以儲存在不同型別的儲存器單元,所以每條指令的執行時鐘週期數也不盡相同。

優點:可以直接對儲存器運算元進行訪問,容易對指令進行編碼,且其目的碼較小。

缺點:指令中的運算元型別不同。在一條指令中同時對一個暫存器運算元和儲存器運算元進行編碼,將限制指令所能夠表示的暫存器個數。由於指令的運算元可以儲存在不同型別的儲存器單元,所以每條指令的執行時鐘週期數也不盡相同。

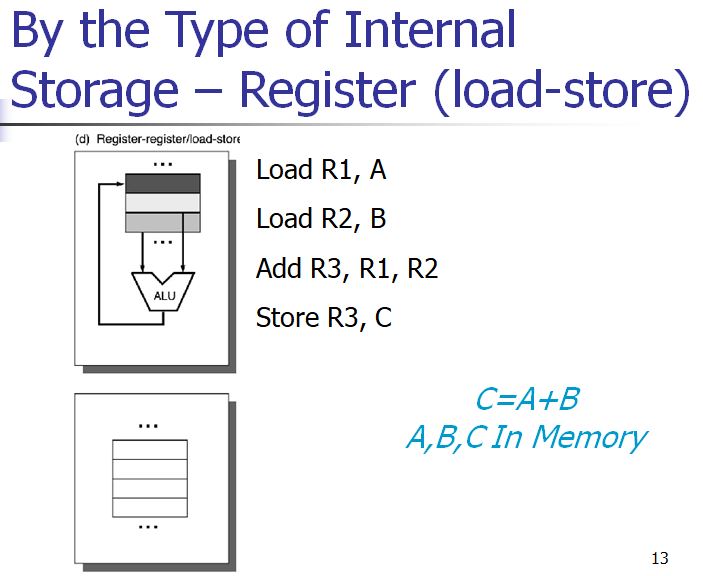

4、指令集結構型別——暫存器——暫存器型

優點:簡單,指令字長固定,是一種簡單的程式碼生成模型,各種指令的執行時鐘週期數相近。

缺點:和指令中含有對儲存器運算元訪問的結構相比,指令條數多,因而其目的碼較大。

Instruction Characteristic

Endian Order 段序/位元組序

“大端對齊/小端對齊”

定址型別

Strucuture of Recent Compilers:Multi-pass structure 多遍掃描結構

優點:簡單,指令字長固定,是一種簡單的程式碼生成模型,各種指令的執行時鐘週期數相近。

缺點:和指令中含有對儲存器運算元訪問的結構相比,指令條數多,因而其目的碼較大。

Instruction Characteristic

Endian Order 段序/位元組序

“大端對齊/小端對齊”

定址型別

Strucuture of Recent Compilers:Multi-pass structure 多遍掃描結構