【 FPGA 】設定偽路徑

阿新 • • 發佈:2018-12-22

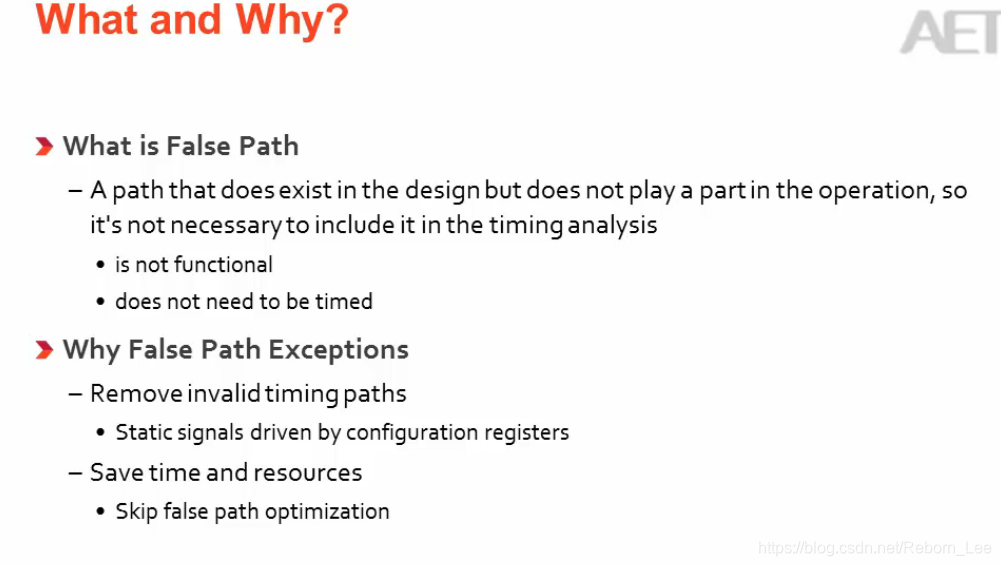

什麼是偽路徑?

偽路徑就是存在,但是不起作用的路徑,因此沒有必要對它進行時序分析。

為什麼要排除偽路徑?

這樣可以移除無效的時序路徑;

跳過路徑優化,因此可以節省時間和資源。

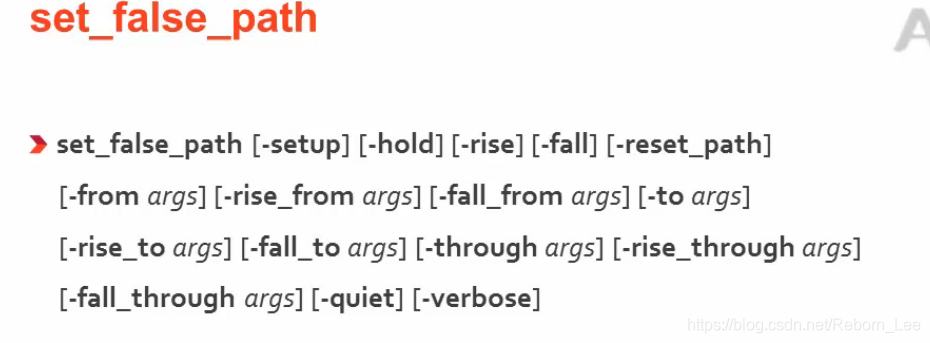

設定偽路徑需要用到的Tcl命令語法?

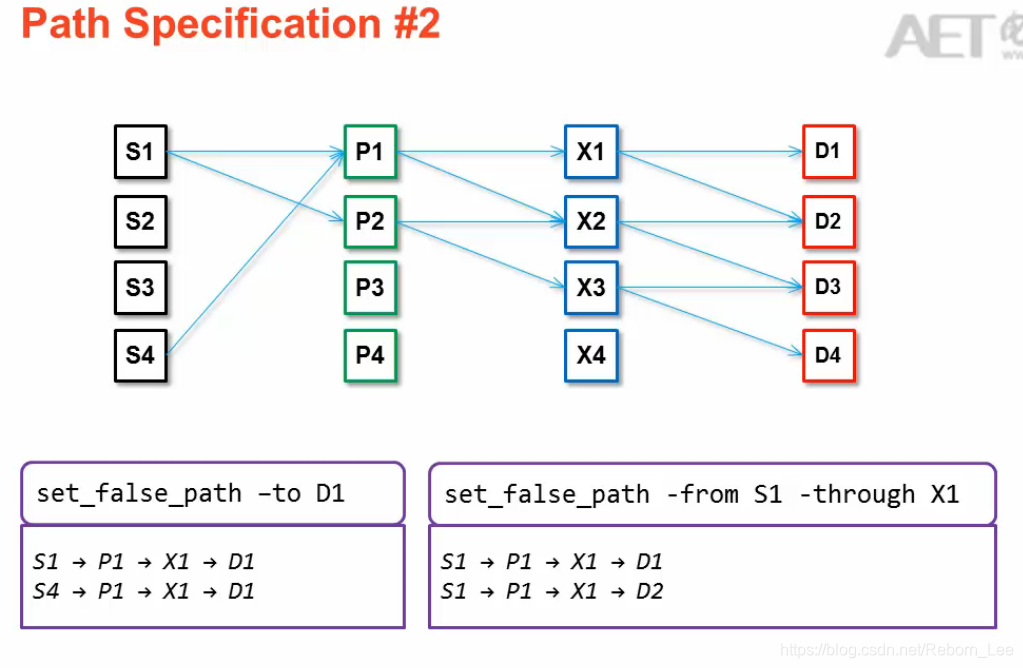

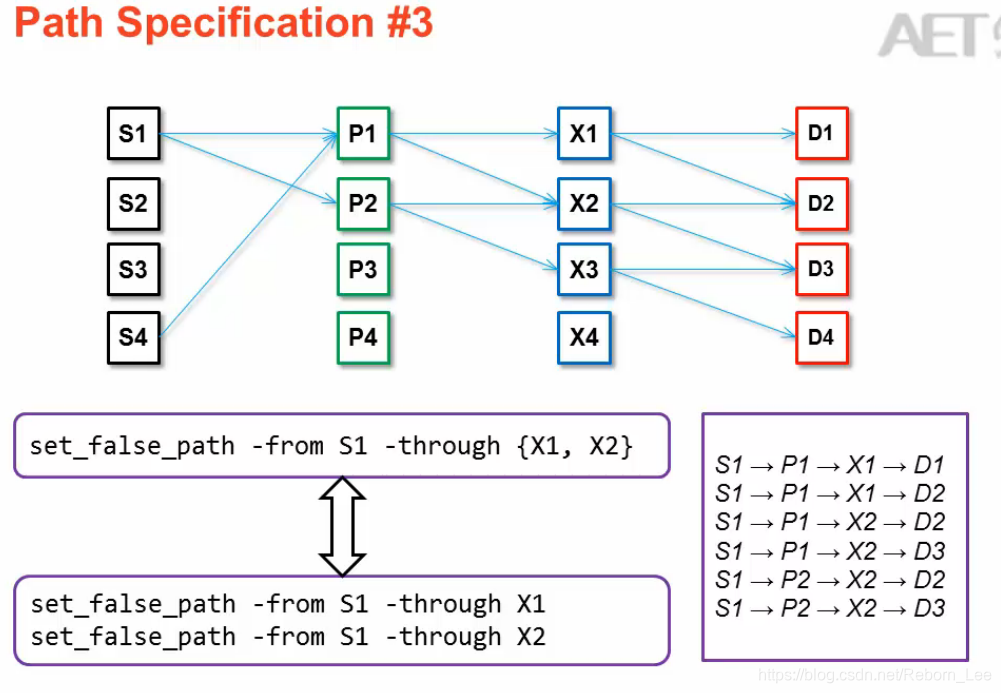

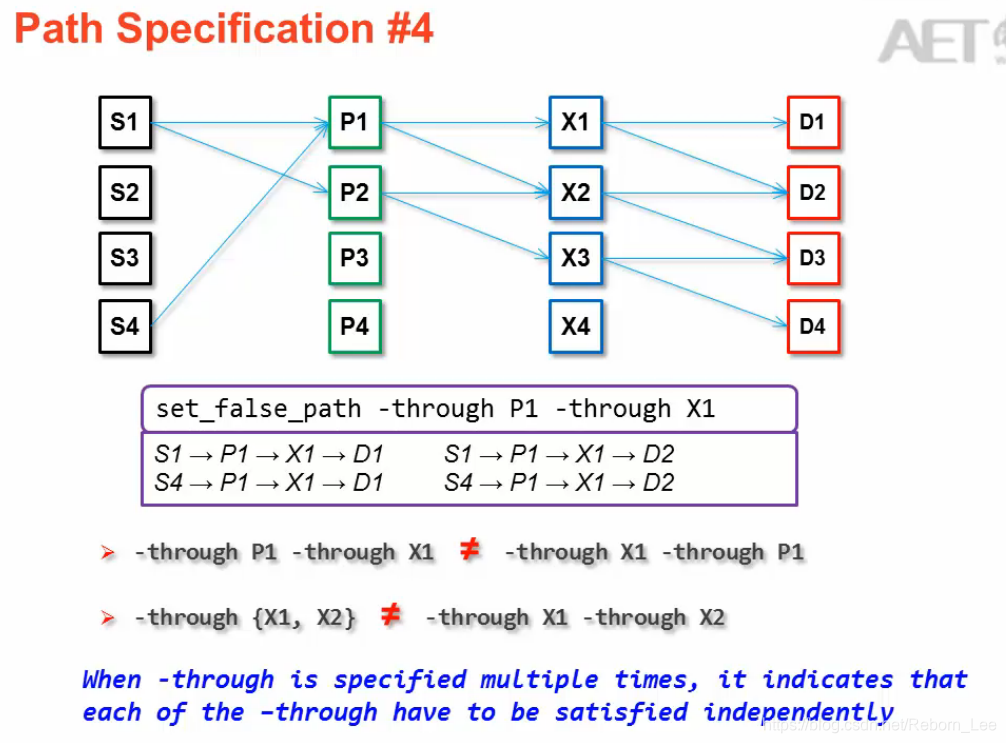

如下圖所示,比較常用的引數是-from -through - to等。

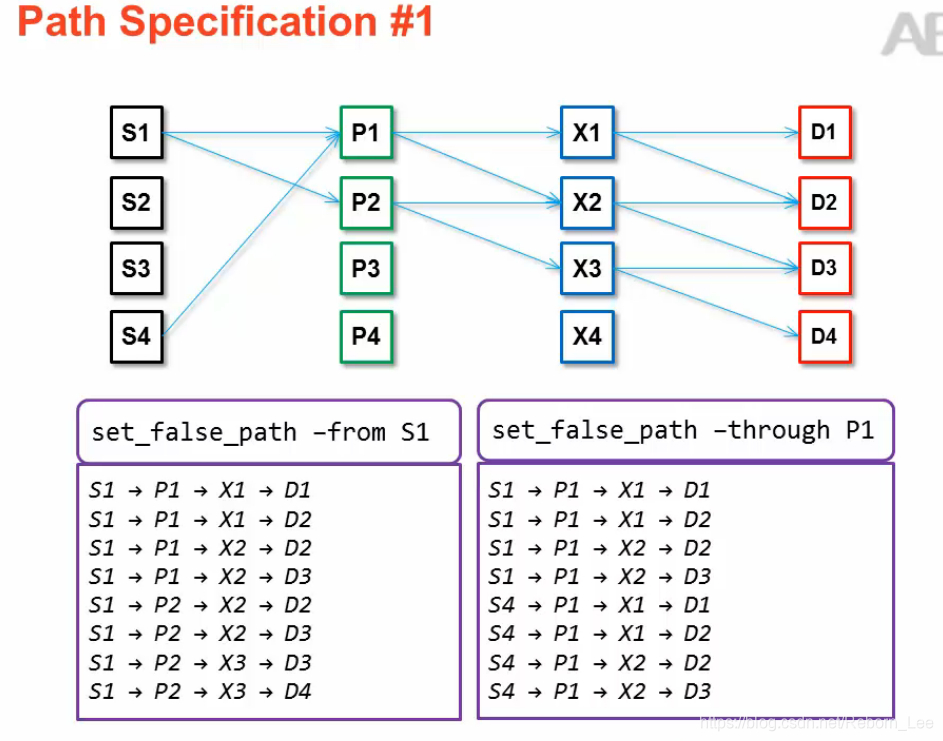

舉例說明各引數的含義:

典型偽路徑的含義:

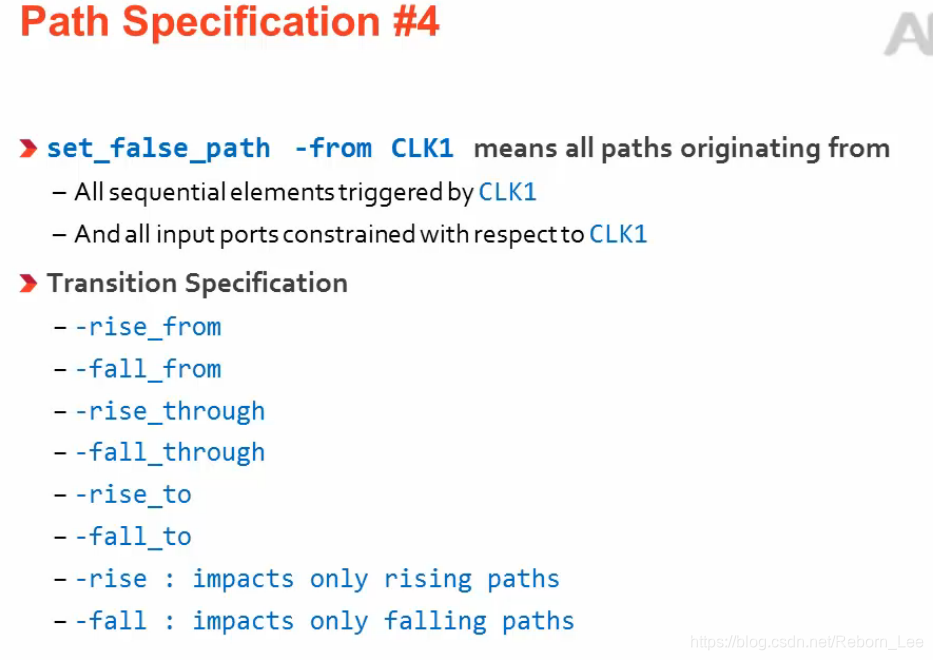

set_false_path -from CLK1,這條Tcl命令意味著這樣的路徑被設定為偽路徑:

路徑源於有CLK1驅動的所有時序元件;

源於被CLK1約束的輸入埠。

偽路徑的型別?

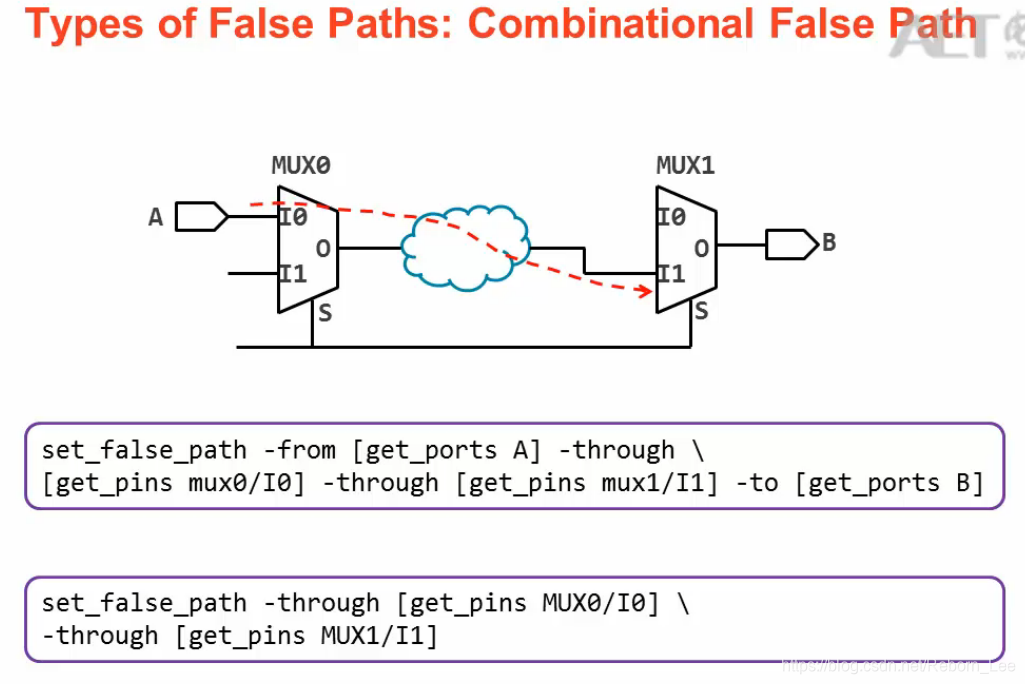

組合邏輯路徑:如下圖的組合路徑,由兩個多路選擇器構成,且控制端由同一控制訊號驅動,明顯這條路徑根本沒有存在的必要,因為它沒有作用,因為控制訊號一致,mux選擇的埠也一致,但是二者之間的連線卻不是一致的,這樣的話,路徑的存在就沒有意義。

下圖給出了兩種設定這個偽路徑的方式,第一種過於繁瑣,推薦第二種。

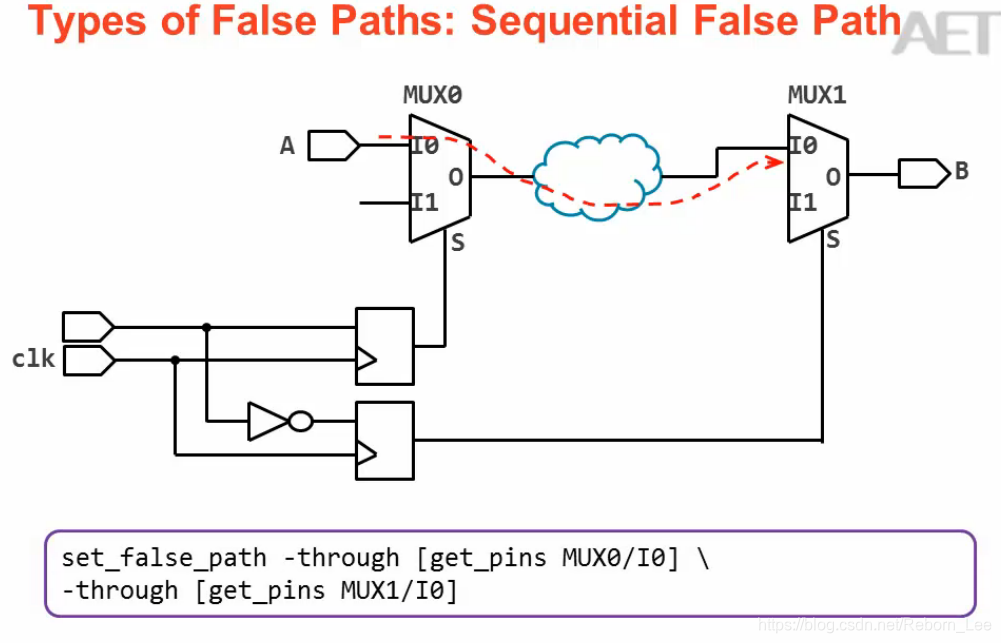

再給出一種偽路徑的型別,這個型別是上一個型別的進化版,加上了時序元件而已,但是這條路徑同樣沒有什麼意義?

因為儘管二者的mux選中的埠連線到了一起,但是控制訊號卻是相反的,例如,mux1選中I0的時候,Mux0選中I1。搞笑?

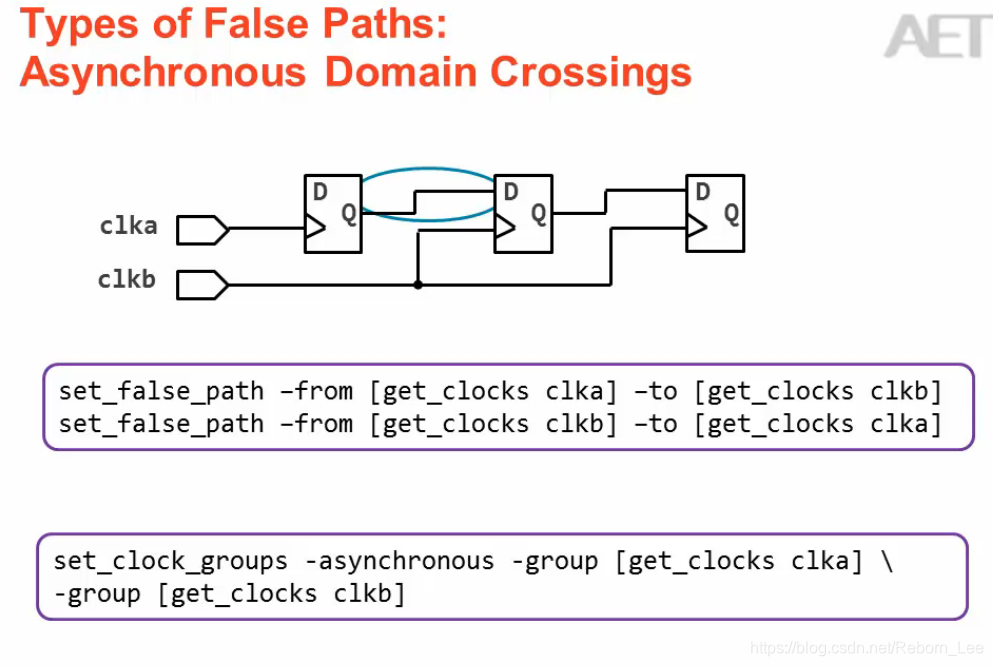

下圖這種偽路徑的型別比較常見,為跨時鐘域的偽路徑。

為了不對其進行時序分析,所以可以設定偽路徑,功能與設定非同步時鐘組一致。

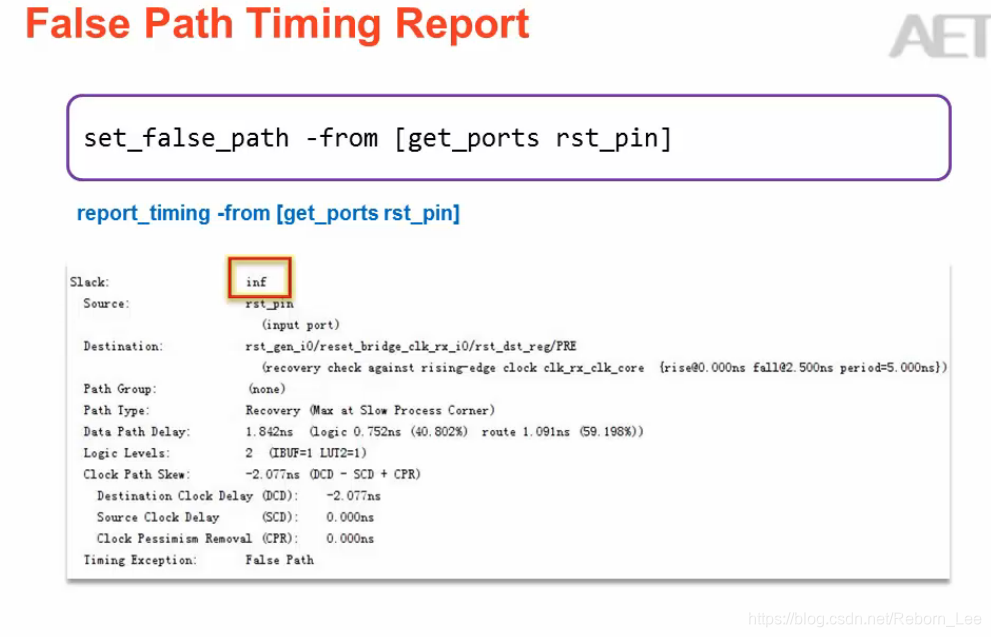

最後給出一個偽路徑的時序報告案例: