stm32 中斷架構

阿新 • • 發佈:2018-12-23

1. 初步瞭解

- stm32F4有兩種CPU模式:特權模式和使用者模式。當發生異常或中斷時會進入到特權模式中

- stm32F4有兩個系統棧,一個是MSP,一個是PSP。CPU在使用者模式中使用PSP作為棧,當發生異常時,會從異常向量表的起始位置讀取4byte (MSP),作為特權模式的棧

- stm32F4的中斷架構分為:不可遮蔽異常和可遮蔽異常(將中斷看作是一種特殊的異常),不可遮蔽異常是stm32F4的cpu core(cortex M4)決定,該core是ARM-V7M架構,在該架構中定義了NVIC(可巢狀的中斷向量控制器),通過該控制器來分配其他的中斷。

- 關於NVIC:有91個可遮蔽的中斷通道,16級可程式設計優先順序

- EXTI:外部中斷控制器,可以trigger電平和邊沿

2. 問題:

- 異常發生時,NVIC是否有一些狀態暫存器?NVIC具體是什麼樣的?

- 在cortexM4中介紹:能夠降低中斷延時,電源管理控制

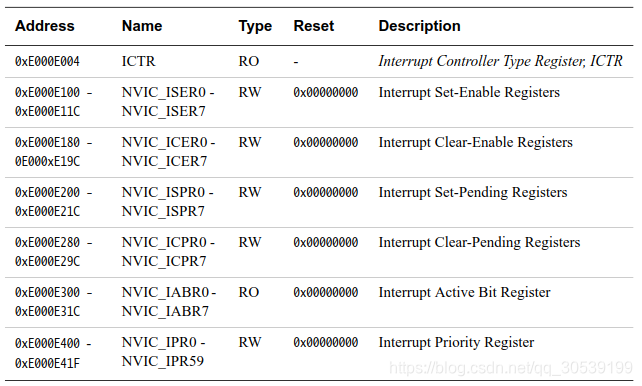

- 暫存器:

- 檢視Active Bit register:在ARMV7 B3.4.1中可以看到,當中斷髮生時該暫存器對應位置會active

- NVIC作為ARMV7-M架構的一部分,主要用來管理中斷(遮蔽,使能,狀態,優先順序等)

- ICTR暫存器主要可以看到CPU一共包含多少中斷(cortex M4 Table 6-2可以看到)

3. 如何使用

- 中斷優先順序的機制是什麼樣的?

- 分成兩組:搶佔優先順序和響應優先順序。搶佔優先順序有搶佔的特權,共四組。響應優先順序只能決定中斷優先順序,不能搶佔。

- 預設全部是槍戰優先順序0,即不具備搶佔優先順序能力。只具備響應優先順序。那麼預設的響應優先順序如何確認?即中斷向量表是怎麼確認的?由硬體通道連結確認的嗎?

- 中斷巢狀如何處理?相關機制是什麼樣的?[留待後面進行補充]