電源設計中的電容應用例項

電源往往是我們在電路設計過程中最容易忽略的環節。其實,作為一款優秀的設計,電源設計應當是很重要的,它很大程度影響了整個系統的效能和成本。

這裡,只介紹一下電路板電源設計中的電容使用情況。這往往又是電源設計中最容易被忽略的地方。很多人搞ARM,搞DSP,搞FPGA,乍一看似乎搞的很高深,但未必有能力為自己的系統提供一套廉價可靠的電源方案。這也是我們國產電子產品功能豐富而效能差的一個主要原因,根源是研發風氣吧,大多研發工程師毛燥、不踏實;而公司為求短期效益也只求功能豐富,只管今天殺雞飽餐一頓,不管明天還有沒有蛋,“路有餓死骨”也不值得可惜。

言歸正轉,先跟大家介紹一下電容。

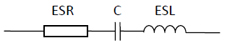

大家對電容的概念大多還停留在理想的電容階段,一般認為電容就是一個C。卻不知道電容還有很多重要的引數,也不知道一個1uF的瓷片電容和一個1uF的鋁電解電容有什麼不同。實際的電容可以等效成下面的電路形式:

C:電容容值。一般是指在1kHz,1V 等效AC電壓,直流偏壓為0V情況下測到的,不過也可有很多電容測量的環境不同。但有一點需注意,電容值C本身是會隨環境發生改變的。

ESL:電容等效串聯電感。電容的管腳是存在電感的。在低頻應用時感抗較小,所以可以不考慮。當頻率較高時,就要考慮這個電感了。舉個例子,一個0805封裝的0.1uF貼片電容,每管腳電感1.2nH,那麼ESL是2.4nH,可以算一下C和ESL的諧振頻率為10MHz左右,當頻率高於10MHz,則電容體現為電感特性。

ESR:電容等效串聯電阻。無論哪種電容都會有一個等效串聯電阻,當電容工作在諧振點頻率時,電容的容抗和感抗大小相等,於是等效成一個電阻,這個電阻就是ESR。因電容結構不同而有很大差異。鋁電解電容ESR一般由幾百毫歐到幾歐,瓷片電容一般為幾十毫歐,鉭電容介於鋁電解電容和瓷片電容之間。

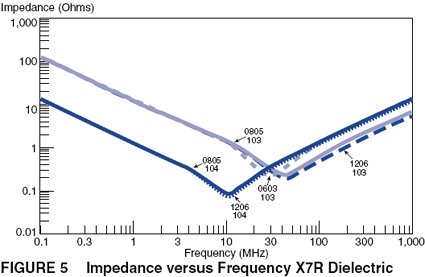

下面我們看一些X7R材質瓷片電容的頻率特性:

當然,電容相關的引數還有很多,不過,設計中最重要的還是C和ESR。

下面簡單介紹一下我們常用到的三種電容:鋁電解電容,瓷片電容和鉭電容。

1)鋁電容是由鋁箔刻槽氧化後再夾絕緣層卷制,然後再浸電解質液製成的,其原理是化學原理,電容充放電靠的是化學反應,電容對訊號的響應速度受電解質中帶電離子的移動速

度限制,一般都應用在頻率較低(1M 以下)的濾波場合,ESR主要為鋁萡電阻和電解液等效電阻的和,值比較大。鋁電容的電解液會逐漸揮發而導致電容減小甚至失效,隨溫度升高揮發速度加快。溫度每升高10度,電解電容的壽命會減半。如果電容在室溫27 度時能使用10000小時的話,57度的環境下只能使用1250小時。所以鋁電解電容儘量不要太靠近熱源。

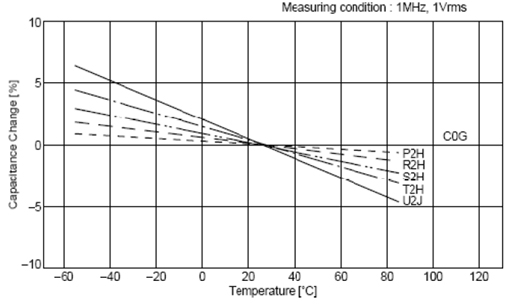

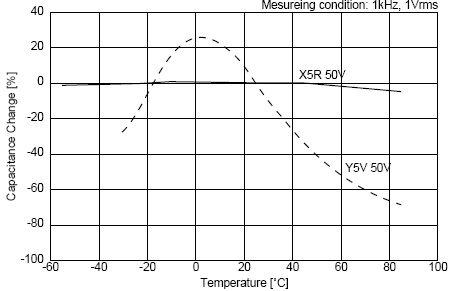

2)瓷片電容存放電靠的是物理反應,因而具有很高的響應速度,可以應用到上G的場合。不過,瓷片電容因為介質不同,也呈現很大的差異。效能最好的是C0G材質的電容,溫度係數小,不過材質介電常數小,所以容值不可能做太大。而效能最差的是Z5U/Y5V材質,這種材質介電常數大,所以容值能做到幾十微法。但是這種材質受溫度影響和直流偏壓(直流電壓會致使材質極化,使電容量減小)影響很嚴重。下面我們看一下C0G、X5R、Y5V三種材質電容受環境溫度和直流工作電壓的影響。

可以看到C0G的容值基本不隨溫度變化,X5R穩定性稍差些,而Y5V材質在60度時,容量變為標稱值的50%。

可以看到50V 耐壓的Y5V 瓷片電容在應用在30V 時,容量只有標稱值的30%。陶瓷電容有一個很大的缺點,就是易碎。所以需要避免磕碰,儘量遠離電路板易發生形變的地方。

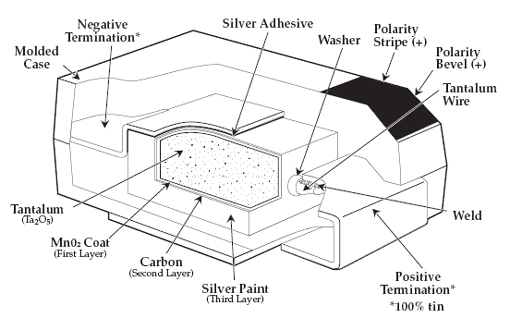

3)鉭電容無論是原理和結構都像一個電池。下面是鉭電容的內部結構示意圖:

鉭電容擁有體積小、容量大、速度快、ESR低等優勢,價格也比較高。決定鉭電容容量和耐壓的是原材料鉭粉顆粒的大小。顆粒越細可以得到越大的電容,而如果想得到較大的耐壓就需要較厚的Ta2O5,這就要求使用顆粒大些的鉭粉。所以體積相同要想獲得耐壓高而又容量大的鉭電容難度很大。鉭電容需引起注意的另一個地方是:鉭電容比較容易擊穿而呈短路特性,抗浪湧能力差。很可能由於一個大的瞬間電流導致電容燒燬而形成短路。這在使用超大容量鉭電容時需考慮(比如1000uF 鉭電容)。

從上面可以瞭解到不同的電容有不同的應用場合,並不是價格越高越好。

下面講一下電源設計中電容的作用。

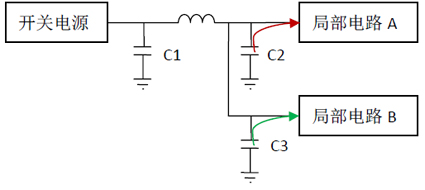

在電源設計應用中,電容主要用於濾波(filter)和退耦/旁路(decoupling/bypass)。濾波主要指濾除外來噪聲,而退耦/旁路(一種,以旁路的形式達到退耦效果,以後用“退耦”代替)是減小區域性電路對外的噪聲干擾。很多人容易把兩者搞混。下面我們看一個電路結構:

圖中開關電源為A和B供電。電流經C1 後再經過一段PCB 走線(暫等效為一個電感,實際用電磁波理論分析這種等效是有誤的,但為方便理解,仍採用這種等效方式。)分開兩路分別供給A 和B。開關電源出來的紋波比較大,於是我們使用C1對電源進行濾波,為A和B提供穩定的電壓。C1需要儘可能的靠近電源放置。C2和C3均為旁路電容,起退耦作用。當A在某一瞬間需要一個很大的電流時,如果沒有C2 和C3,那麼會因為線路電感的原因A端的電壓會變低,而B端電壓同樣受A端電壓影響而降低,於是區域性電路A的電流變化引起了區域性電路B的電源電壓,從而對B電路的訊號產生影響。同樣,B的電流變化也會對A 形成干擾。這就是“共路耦合干擾”。

增加了C2後,區域性電路再需要一個瞬間的大電流的時候,電容C2可以為A暫時提供電流,即使共路部分電感存在,A端電壓不會下降太多。對B的影響也會減小很多。於是通過電流旁路起到了退耦的作用。

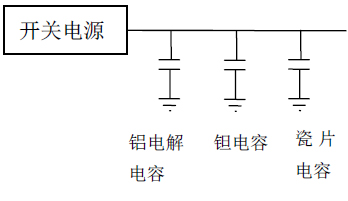

一般濾波主要使用大容量電容,對速度要求不是很快,但對電容值要求較大。一般使用鋁電解電容。浪湧電流較小的情況下,使用鉭電容代替鋁電解電容效果會更好一些。從上面的例子我們可以知道,作為退耦的電容,必需有很快的響應速度才能達到效果。如果圖中的區域性電路A 是指一個晶片的話,那麼退耦電容要用瓷片電容,而且電容儘可能靠近晶片的電源引腳。而如果“區域性電路A”是指一個功能模組的話,可以使用瓷片電容,如果容量不夠也可以使用鉭電容或鋁電解電容(前提是功能模組中各晶片都有了退耦電容—瓷片電容)。濾波電容的容量往往都可以從開關電源晶片的資料手冊裡找到計算公式。如果濾波電路同時使用電解電容、鉭電容和瓷片電容的話,把電解電容放的離開關電源最近,這樣能保護鉭電容。瓷片電容放在鉭電容後面。這樣可以獲得最好的濾波效果。

退耦電容需要滿足兩個要求,一個是容量需求,另一個是ESR需求。也就是說一個0.1uF的電容退耦效果也許不如兩個0.01uF電容效果好。而且,0.01uF電容在較高頻段有更低的阻抗,在這些頻段內如果一個0.01uF電容能達到容量需求,那麼它將比0.1uF電容擁有更好的退耦效果。

很多管腳較多的高速晶片設計指導手冊會給出電源設計對退耦電容的要求,比如一款500多腳的BGA封裝要求3.3V電源至少有30個瓷片電容,還要有幾個大電容,總容量要200uF以上

FROM: http://www.21ic.com/app/power/201106/87140.htm