關於設計抗混疊濾波器的三個指導原則

我們知道,在高精度ADC應用中使用抗混疊濾波器是有益的,不過,設計合適的抗混疊濾波器也同樣重要—如果你不小心的話,就像把有害誤差從系統中消除一樣,很容易將有害誤差引入到你的系統中。在為你的應用設計抗混疊濾波器時,請考慮以下3個通用指導原則。

1.選擇你的濾波器截止頻率

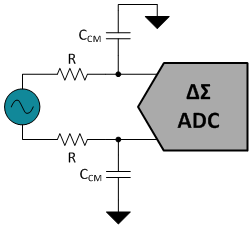

最簡單的抗混疊濾波器是一個單極、低通濾波器,如圖1所示,它使用一個串聯電阻器 (R) 和共模電容器 (CCM)。設計這個濾波器的第一步就是選擇所需的截止頻率,fC。在fC上,濾波器的響應滾降至-3dB,並且在頻率域範圍內繼續以-20dB/十倍頻的速度減少。

選擇一個比ADC調製器取樣頻率,fMOD,至少低十倍頻的截止頻率,其目的在於,在這些頻率上以10倍或更高倍數打壓帶外噪聲。對於增加的衰減,通過增加R和CCM的值來進一步減少截止頻率。你的數字抽取濾波器的用途就是提供幫助,所以就沒有必要在所需訊號頻寬之後立即設定你的抗混疊濾波器截止頻率。

方程式1計算出單極、低通濾波器的截止頻率為-3dB:

圖1.ADC輸入上的單極、低通濾波器

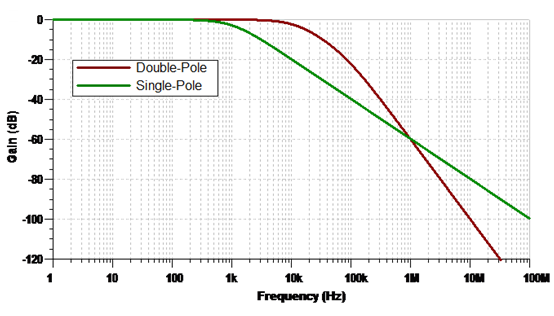

有時候,一個單極、低通濾波器也許還不夠。諸如振動感測等應用也許是用更少的過取樣來分析更寬頻寬上的訊號。這就使數字抽取濾波器的通帶更加靠近fMOD,並且使得抗混疊濾波器的滾降空間更小。在這些情況下,你可以新增一個包含額外RC對的第二極或第三極,以實現一個更加靈敏的濾波器響應。

圖2中顯示的是,設計用於ADC的單極和雙極濾波器的響應;這個ADC在fMOD= 1MHz上對輸入進行取樣。雙極濾波器扁平通帶向外擴充套件至大約20kHz,並且仍然能夠在1MHz上實現-60dB的衰減。

圖2.單極和雙極低通濾波器的頻率響應

2.考慮差分與共模濾波器之間的關係

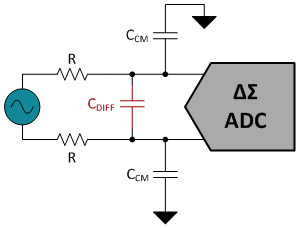

很多ADC轉換兩個獨立輸入之間(例如INP與INN)的電壓,所以,設計人員經常在每個輸入上放一個共模濾波器,以保持系統共模抑制 (CMR)。然而,元件容差將使任意兩個濾波器不匹配,並且會降低頻率範圍內的CMR效能,這是因為對共同訊號的濾波操作不同。這就通過人們已知的共模至差分轉換產生一個差分訊號誤差。

方程式2使用電阻器容差,RTOL,和電容器容差,CTOL,計算出共模抗混疊濾波器在指定頻率下的CMR:

對於需要高CMR的應用,如圖3中所示,可以考慮新增一個差分濾波器,以便為2個共模濾波器提供補充。通過將差分電容器CDIFF增加到比CCM大10倍,將差分截止頻率設定為比共模截止頻率低10倍頻。這樣可以減輕由共模元件不匹配所引入的誤差,並且生成一個更加靈敏的總體濾波器響應。方程式3計算出差分低通濾波器的截止頻率。需要注意的是,分母中有一個額外的因子2。

圖3.添加了一個差分濾波器的共模濾波器

3.選擇合適的元件值

將電阻器新增到訊號路徑中將在測量中引入有害噪聲和誤差,所以,不論何時都有必要將它們控制在合理的範圍內。

電阻器噪聲—也被稱為Johnson或熱噪聲—可被建模為電壓源與你的理想“無噪聲”電阻器相串聯。總的說來,你不希望電阻器熱噪聲佔據整條訊號鏈,那麼,將其保持在ADC的噪底以下就非常重要。方程式4計算出電阻器熱噪聲的噪聲密度,vn:

![]()

在這裡,k = 玻爾茲曼常量 (1.38E-23 J/K),而T是溫度值,單位為開爾文。

串聯電阻也會在輸入偏置電流出現時引入小的偏移電壓。雖然你也許能夠在之後校準這個值,不過還是要儘可能地限制電阻器尺寸,特別是在偏置電流有可能變得很大時更應如此。

與濾波器電阻器不同,你能夠使用的電容器的值越高,效果就越好。如需瞭解其中的原因,就必須知道ADC是如何對輸入進行取樣的。

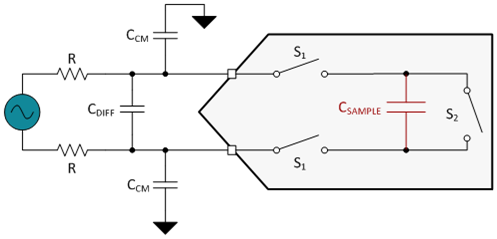

不包含整合緩衝器的增量-累加ADC的輸入直接與ADC調製器的開關電容器取樣結構相連。這個取樣結構包含一個開關網路,以及電容值大約為10pF或20pF的取樣電容器。圖4顯示的是一個經簡化示例。

圖4.一個ADC中的經簡化開關電容器取樣結構

取樣期間,這個開關電容器電路在外部電路上放置了一個瞬態負載。這個濾波電容器幫助減少來自調製器的取樣電荷注入,並且提供為取樣電容器,CSAMPLE,充電所需的某些瞬時電流。濾波電容器越大,可用的電荷就越多。由於其高Q因子、低溫度係數、以及穩定的電氣特性,請使用NP0/C0G型別的陶瓷電容器。較大的電容器值也會改進總諧波失真 (THD) 等AC技術規格,不過,需牢記的是,這就增加了濾波器的RC時間常量,並且需要一個更長的穩定時間。

優於其它ADC架構。