(學習筆記) SPI通訊協議

概念

SPI, Serial Perripheral Interface, 序列外圍裝置介面, 是 Motorola 公司推出的一種通訊介面技術。

SPI,是一種高速的,全雙工,同步序列通訊匯流排,並且在晶片的管腳上只佔用四根線(MISO,MOSI,NSS,SCK)。

主要應用在 EEPROM,FLASH,實時時鐘,AD轉換器,還有數字訊號處理器和數字訊號解碼器之間。

引腳

SPI介面經常被稱為4線序列匯流排,以主/從方式工作,資料傳輸過程由主機初始化。4條訊號線分別為:

1) SCK:序列時鐘,用來控制資料交換的時機和速率,由主機提供;

//serial clock output for masters and input for slaves

2) MOSI:主機輸出從機輸入資料線;

3) MISO:主機輸入從機輸出資料線;

4) NSS:從機選擇線,低電平有效,由主機控制。

在SPI總線上,某一時刻可以出現多個從機,但只能存在一個主機,主機通過片選線來確定要通訊的從機(也就是任何時刻只能有一對主從機在通訊)。這就要求從機的MISO口具有三態特性,使得該口線在器件未被選通時表現為高阻抗。

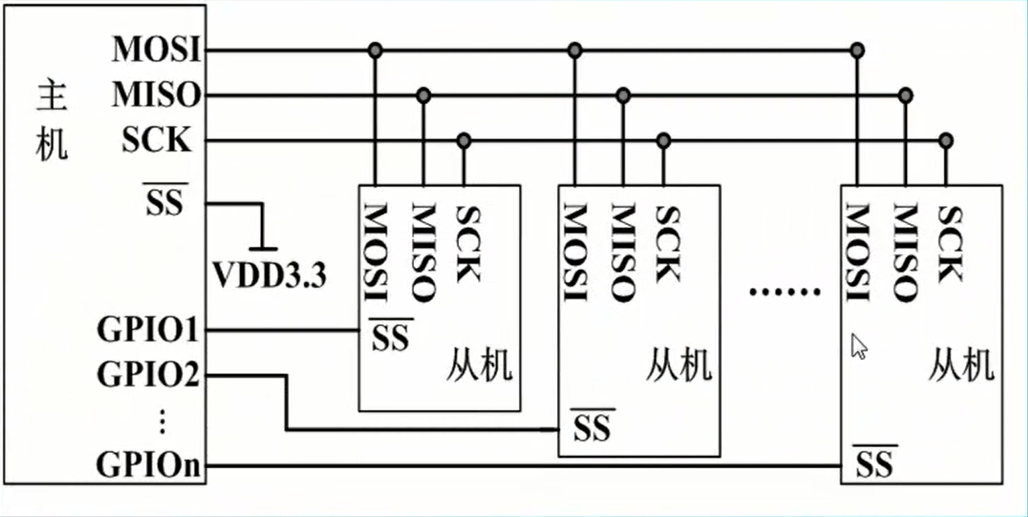

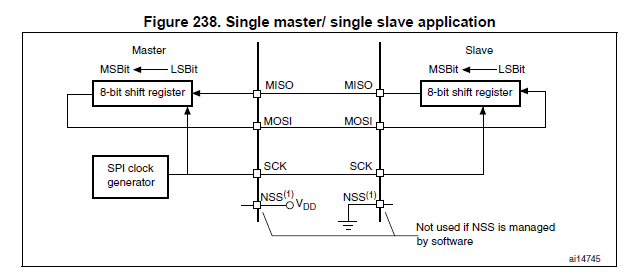

引腳連線

從圖中看到,主機的NSS訊號為高電平,從機的NSS訊號被主機片選。

原理

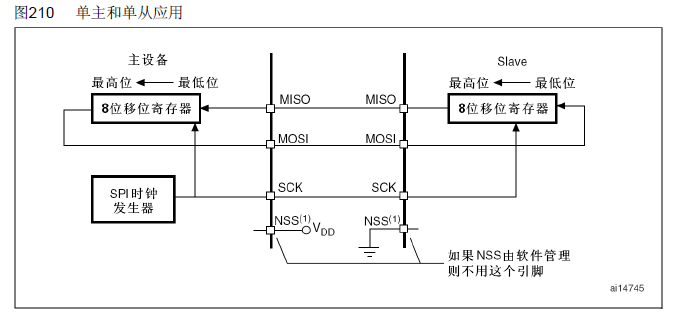

如圖:

1.MISO引腳相連線,MOSI引腳相互連線。這樣,主從裝置之間序列地傳輸且通訊總是由主裝置發起。

2.主裝置通過MOSI腳把資料發給從裝置的同時,從裝置通過MISO腳傳回資料給主裝置。這個全雙工的過程是由時鐘訊號SCK控制同步的。

3.時鐘訊號由主裝置通過SCK腳提供。

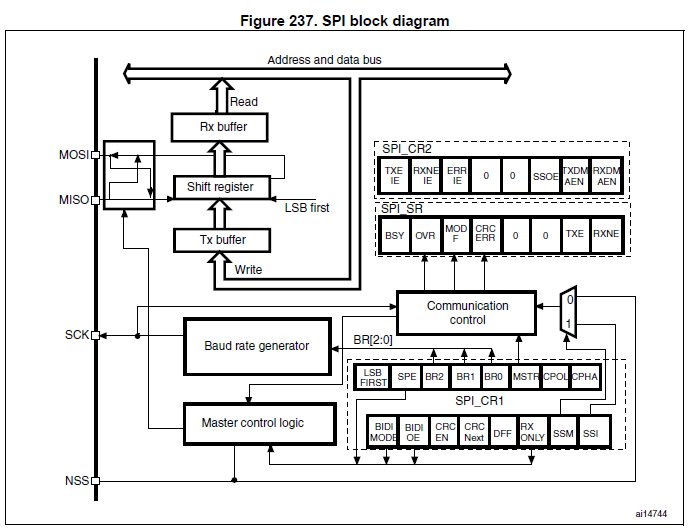

框圖

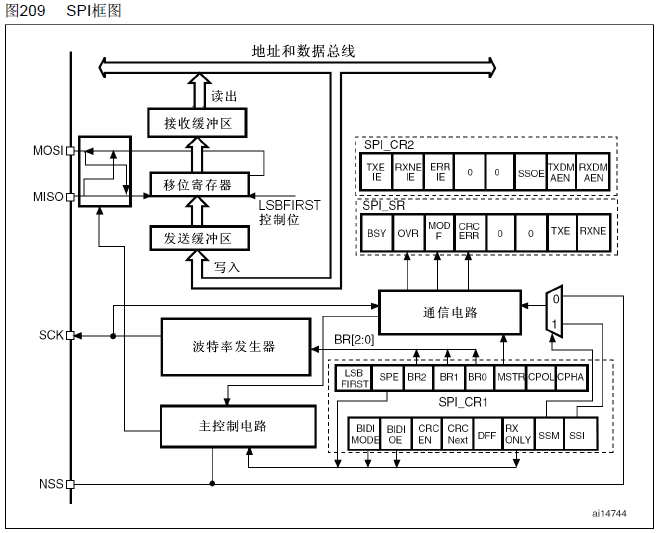

簡析:

1. 從圖中可以具體的看出SCK訊號,由波特率發生器產生,傳給從機和自己的通訊控制暫存器中。

2. 波特率的大小由SPL_CR1暫存器的BR2,BR1,BR0三個位決定。

3. 通訊控制由SPL_CR1暫存器的MSTR,SSM,SSI三個位和NSS控制,通訊控制控制通訊過程中的錯誤如CRC校驗錯誤,模式錯誤,溢位。

4. 主控制電路控制,輸入輸出的邏輯閘電路開啟與關閉。

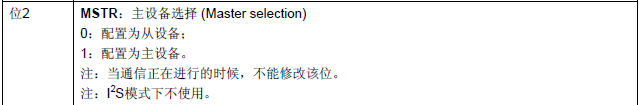

主從選擇

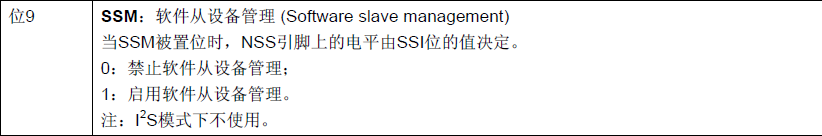

NSS模式可以由硬體或軟體設定。

軟體設定(內部至高或低):

主機設定:

從機設定:

即SSM至為1時,外部NSS引腳置為它用,內部NSS引腳可以通過SSI位來驅動。

時鐘訊號的相位和極性

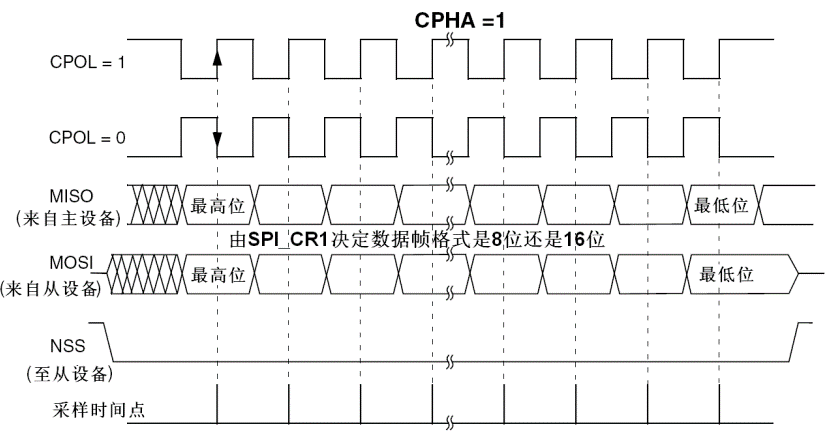

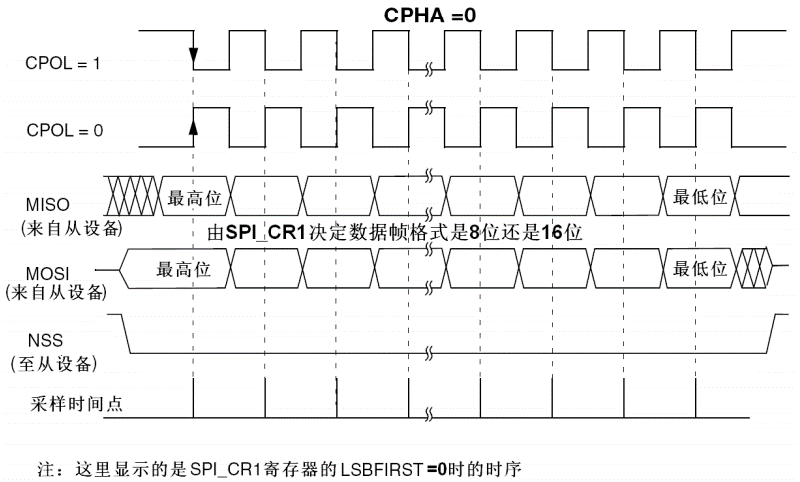

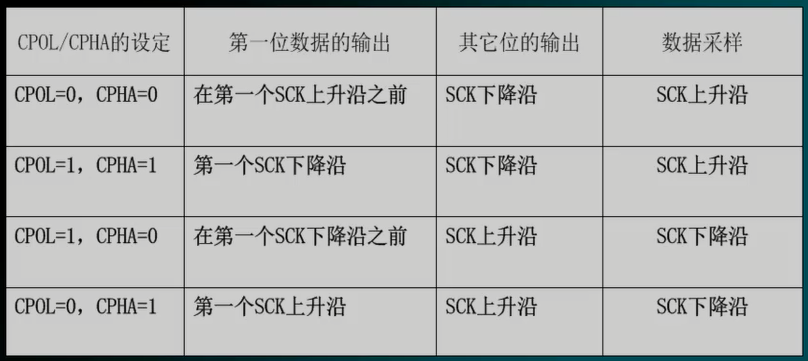

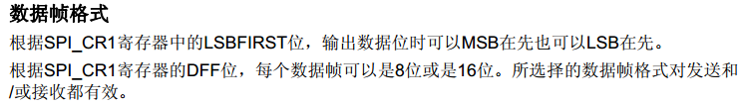

1.SPI介面可由CPOL和CPHA設定4種不同傳輸格式時序

2.SCK的空閒狀態必須和SPI_CR1暫存器指定的極性一致(CPOL為’1’時,空閒時應上拉SCK為高電平;CPOL為’0’時,空閒時應下拉SCK為低電平)。

3.CPHA=0時,資料出現快於時鐘的第一個邊沿。CPHA=1時,資料出現與時鐘的第一個邊沿同步。

如果CPHA(時鐘相位)位被置’1’,SCK時鐘的第二個邊沿(CPOL位為0時就是下降沿,CPOL位為’1’時就是上升沿)進行資料位的取樣,資料在第二個時鐘邊沿被鎖存。

如果CPHA位被清’0’,SCK時鐘的第一邊沿(CPOL位為’0’時就是下降沿,CPOL位為’1’時就是上升沿)進行資料位取樣,資料在第一個時鐘邊沿被鎖存。

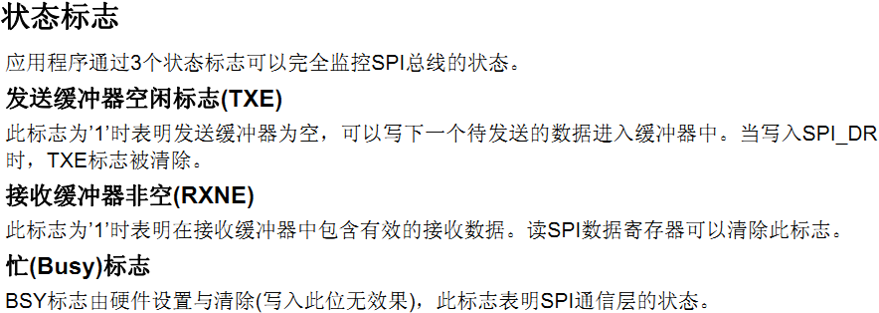

這麼多模式,主要是為了配合外部晶片。