exynos 4412 時鐘配置

阿新 • • 發佈:2019-01-16

/**

******************************************************************************

* @author Maoxiao Hu

* @version V1.0.0

* @date Jan-2015

******************************************************************************

* < COPYRIGHT 2015 ISE of SHANDONG UNIVERSITY >

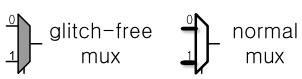

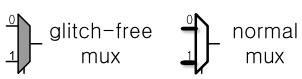

******************************************************************************  左邊深色的:無抖動多路選擇器,無抖動意味著在多路選擇切換的瞬間,下游時鐘就可以穩定下來。需要注意是在切換時要保證上游時鐘已經存在並穩定,不然下游時鐘狀態不確定。

右邊淺色的:有抖動多路選擇器,意味著多路選擇切換後,要經歷一段時間的不穩定時間,但是有穩定後有相應暫存器標誌位標示下游時鐘已經穩定,這類指示暫存器器一般以CLK_MUX_STAT開頭。

—————————————————————————————-

全域性約束條件:

1、無抖動多路選擇器的時鐘源需要存在並且穩定。

2、當某個PLL被設定為關閉狀態,是不可以使用它的輸出訊號的。

—————————————————————————————-

左邊深色的:無抖動多路選擇器,無抖動意味著在多路選擇切換的瞬間,下游時鐘就可以穩定下來。需要注意是在切換時要保證上游時鐘已經存在並穩定,不然下游時鐘狀態不確定。

右邊淺色的:有抖動多路選擇器,意味著多路選擇切換後,要經歷一段時間的不穩定時間,但是有穩定後有相應暫存器標誌位標示下游時鐘已經穩定,這類指示暫存器器一般以CLK_MUX_STAT開頭。

—————————————————————————————-

全域性約束條件:

1、無抖動多路選擇器的時鐘源需要存在並且穩定。

2、當某個PLL被設定為關閉狀態,是不可以使用它的輸出訊號的。

—————————————————————————————-

左邊深色的:無抖動多路選擇器,無抖動意味著在多路選擇切換的瞬間,下游時鐘就可以穩定下來。需要注意是在切換時要保證上游時鐘已經存在並穩定,不然下游時鐘狀態不確定。

右邊淺色的:有抖動多路選擇器,意味著多路選擇切換後,要經歷一段時間的不穩定時間,但是有穩定後有相應暫存器標誌位標示下游時鐘已經穩定,這類指示暫存器器一般以CLK_MUX_STAT開頭。

—————————————————————————————-

全域性約束條件:

1、無抖動多路選擇器的時鐘源需要存在並且穩定。

2、當某個PLL被設定為關閉狀態,是不可以使用它的輸出訊號的。

—————————————————————————————-

左邊深色的:無抖動多路選擇器,無抖動意味著在多路選擇切換的瞬間,下游時鐘就可以穩定下來。需要注意是在切換時要保證上游時鐘已經存在並穩定,不然下游時鐘狀態不確定。

右邊淺色的:有抖動多路選擇器,意味著多路選擇切換後,要經歷一段時間的不穩定時間,但是有穩定後有相應暫存器標誌位標示下游時鐘已經穩定,這類指示暫存器器一般以CLK_MUX_STAT開頭。

—————————————————————————————-

全域性約束條件:

1、無抖動多路選擇器的時鐘源需要存在並且穩定。

2、當某個PLL被設定為關閉狀態,是不可以使用它的輸出訊號的。

—————————————————————————————-一、時鐘之源PLL配置

原因:根據全域性約束條件2,如果PLL關閉那麼不可以使用它的輸出,再根據全域性約束條件1,多路選擇器此時只能選擇外部時鐘!而24M的時鐘直接作為系統的時鐘顯然是不合適的! 4412有4個PLL:APLL, MPLL, EPLL, and VPLL。推薦使用24M外部晶振作為它們的時鐘源。 理論上講,4個PLL均可以在22 ~ 1400MHz之間自由設定,但是手冊強烈推薦的頻率範圍為: /*———————————————*/ APLL & MPLL:200 ~ 1400MHz EPLL:90 ~ 416MHz VPLL:100 ~ 440MHz /*———————————————*/1.0 設定PLL_LOCKTIME

PLL頻率從小變到指定頻率需要一段時間(圖中標紅框的部分雖然不是PLL實際波形但可以參考著理解),當PLL頻率在變化的時候,比如由復位後的初始的400MHz升到1000MHz, 這時,首先把CPU的頻率鎖定,因這此時CPU的頻率是變化的,頻率變化,CPU的狀態就無法確定,所以,此時用 PLL_LOCKTIME 將CPU頻率鎖定一段時間,直到頻率輸出穩定為止。晶片手冊上顯示APLL最大的鎖定時間為100us(Table 60 -9),如果外部晶振是24MHz,100us換算成tick就是2400個tick,所以

APLL_LOCK(Address:0x1004_4000)暫存器該寫入0x960

MPLL_LOCK(Address:0x1004_0008)暫存器該寫入0x190

EPLL_LOCK(Address:0x1003_C010)暫存器該寫入0xBB8

VPLL_LOCK(Address:0x1003_C020)暫存器該寫入0x190。

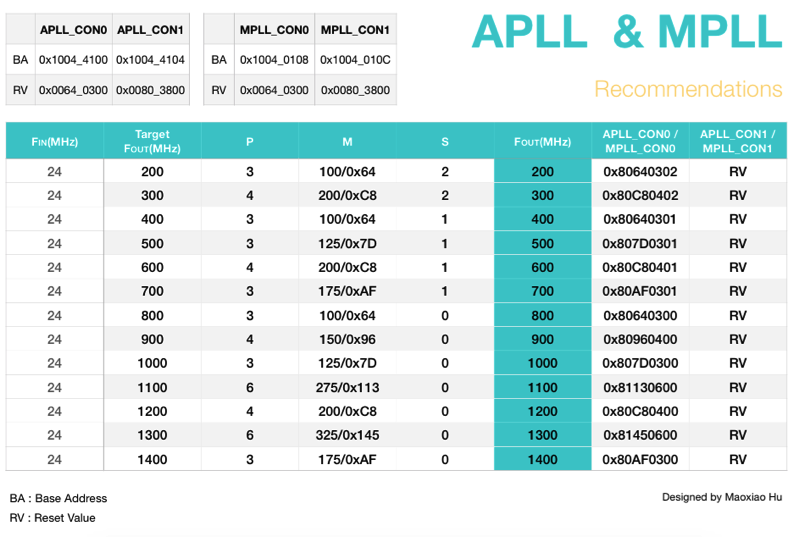

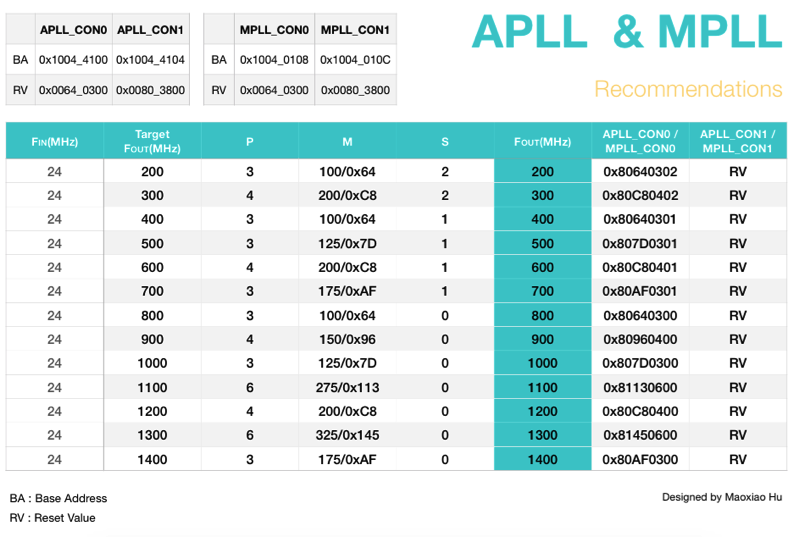

1.1 APLL & MPLL的倍頻值:

設定對應暫存器的 P、M、S 三個值,不同的搭配最終頻率不同,無須自己計算,系統推薦的搭配如下:

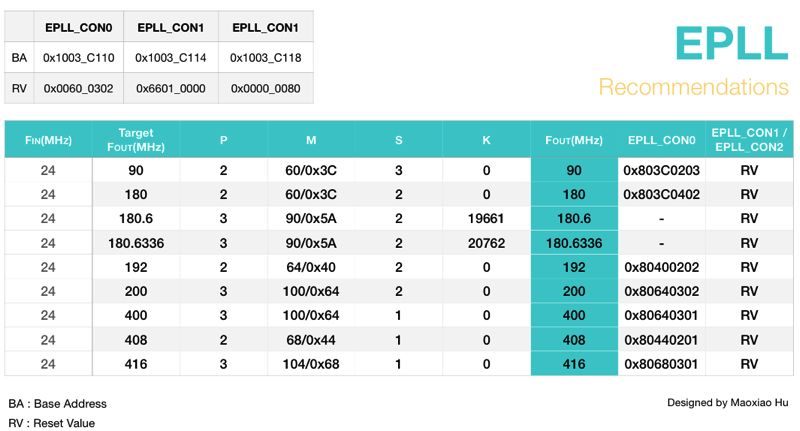

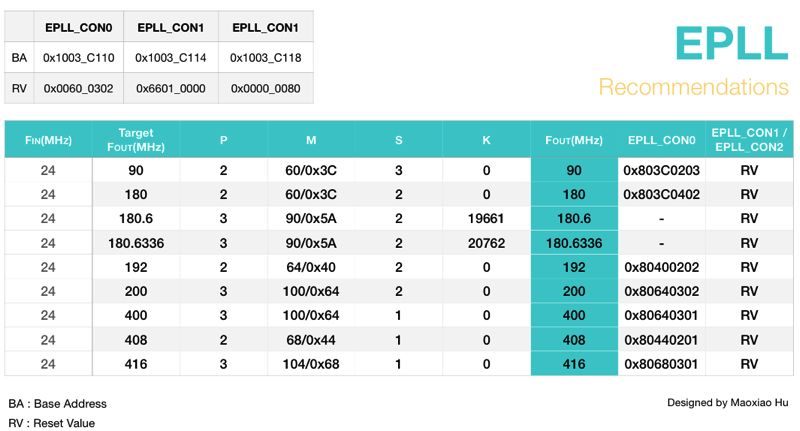

1.2 EPLL的倍頻值:

設定對應暫存器的 P、M、S、K 四個值,不同的搭配最終頻率不同,無須自己計算,系統推薦的搭配如下:

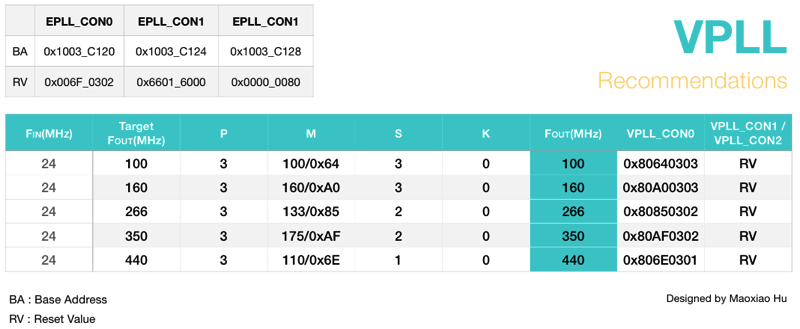

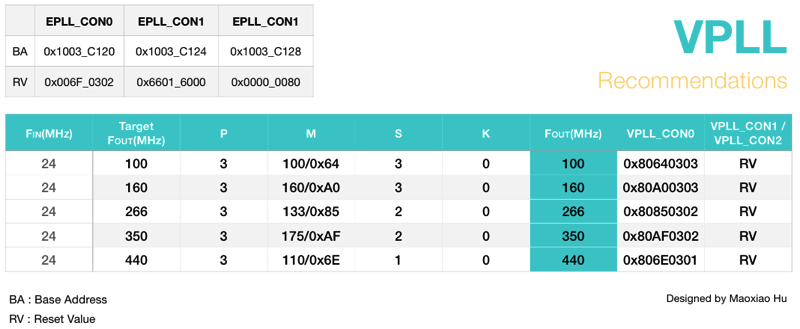

1.3 VPLL的倍頻值

設定對應暫存器的 P、M、S、K 四個值,不同的搭配最終頻率不同,無須自己計算,系統推薦的搭配如下:

1.4 等待PLL穩定

如果PLL輸出穩定了,那麼PLL_CON0的Bit[29]會由0變1。 查詢用匯編實現,以APLL為例: /*———————————————————————*/ wait_pll_lock: ldr r1, [r0, r2] tst r1, #(1<<29) beq wait_pll_lock mov pc, lr ldr r0, =CMU_BASE /* 0x10030000 */ ldr r2, =APLL_CON0_OFFSET /* 0x14100 */ bl wait_pll_lock /*———————————————————————*/ 二、主要模組的初始化順序