ARM CORTEX M系列中ROM TABLE原理分析

最近因為工作需要,在研究CORTEX M系列的MCU內部ROM TABLE工作方式,之前對這個ROM TABLE的理解有些模糊,經過查詢一些文件加上自己的理解,現在比較清晰了,在此總結以下。

目前參考到的文件有以下:

1.ARM® Debug Interface Architecture Specification ADIv5.0 to ADIv5.2

2.ARMv6-M Architecture Reference Manual

3.ARMv7-M Architecture Reference Manual

4.ARMv8-M Architecture Reference Manual(該文件主要針對最新推出的CM23 CM33系列MCU,主要特性是引入了TrustZone)

5.JEDEC STANDARD Standard Manufacturer’s Identification Code

目前參考的晶片是STM32L053系列的一款LQFP64封裝的樣片,具體分析稍後再講,先說一下ROM TABLE的概念,現在網上抄來抄去的概念我就不再重複了,大家想要了解,隨便百度都可以看到,這篇文章我講一下個人的理解。

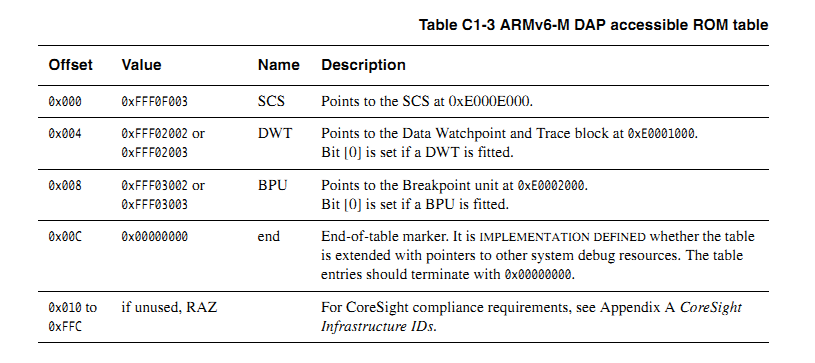

1.首先要明白ROM TABLE之所以叫這個名字,是因為它是一張表,那麼它的表結構是怎樣的呢,看下面的圖:

這裡以ARM V6系列架構的MCU為例,在這個表中,可以清晰的看到ROM TABLE的結構,首先是ROM TABLE中儲存的都是32位的資料,每一個數據的含義如下:

其中[31:12]表示的是地址偏移量,以偏移0x000位置的值為例分析:

地址偏移為:0xFFF0F000,由於當前ROM TABLE所在位置為0xE00FF000,所以可以計算出SCS所在地址為:0xE00FF000+0xFFF0F000=0x1E000E000,最高進位捨棄,那麼就得到了SCS的基址為0xE000E000。該值的bit0和bit1在上面表裡已經寫的很清楚了,就不再囉嗦。看到這裡,可能大家又會問,這個表能看懂了,但是這個表在哪裡該怎麼查到呢?看下面。

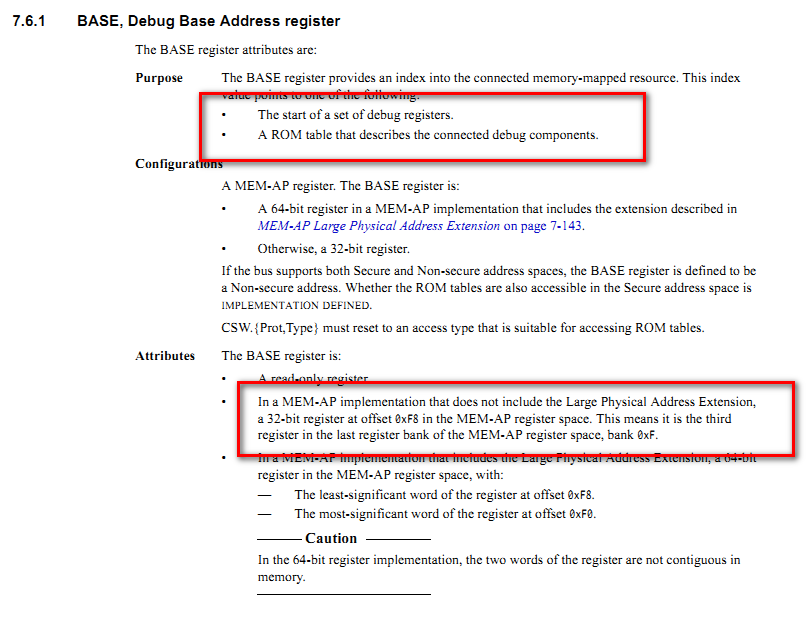

2.ROM TABLE的基址問題。在ARM的每一個系列的架構中,一般都有一個預設的ROM TABLE基址,其實v6m,v7m,v8m的預設基址都是0xE00FF000,但是對於每家晶片廠商都是可以重新定義的,以STM32L053為例,就已經重新定義了ROM TABLE的結構,其中,該基址的值儲存在AP中的0xF8偏移的位置:

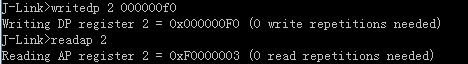

針對該值的讀取,可能需要大傢俱備一些對ARM DEBUG INTERFACE的瞭解,不屬於這篇文章的目的,暫時不展開講,感興趣的可以看我其他兩篇部落格。使用J-LINK讀取該暫存器,如下圖:

這裡可以讀取到上面的DEBUG BASE REGISTER.值為0xF0000003,這個暫存器的結構和bit定義與上面講的ARMv6m的ROM TABLE中的暫存器定義是一致的,這樣就可以確認到SMT32L0的ROM TABLE入口地址為0xF0000000.

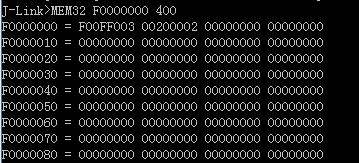

3.確定ROM TABLE入口地址以後,在來看下面這個圖:

看這個圖就很清晰了,ROM TABLE是可能有多個的,所以需要逐條讀取ROM TABLE中的值,直到到達ROM TABLE的最後為止,結束的標誌就是其中的值為0x00000000.

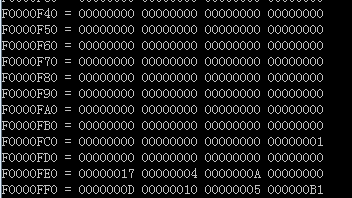

再來看STM32L0的實際內容:截取了開頭和結尾

在這個表中,第一項為0xF00FF003,表明該項為有效項(bit0為1),第二項為0x00200002,表明該項為無效項。再看0xF0000FF4位置

CID的[7:4]表明了當前ROM TABLE的class,該值當前為1,具體含義如下:

1表示當前是一個ROM TABLE,其中儲存的值都是一些偏移量,類似我們寫程式提到的指標,需要在當前表裡繼續查詢,一般查到最低一級的ROM TABLE後,該類別的值就會是0xE,表明是一個IP COMPONENT。

然後就該計算另一個ROM TABLE的入口地址了:0xF0000000+0xF00FF000=0x1E00FF000,是不是很熟悉的地址,這就是預設的ROM TABLE入口地址。

至此,就可以搞清楚ROM TABLE的確認過程,之後每一級的ROM TABLE分析都是一樣的邏輯,如果需要上面提到的文件,可以留下郵箱,有時間我發給大家。