關於上拉與下拉電阻

阿新 • • 發佈:2019-01-31

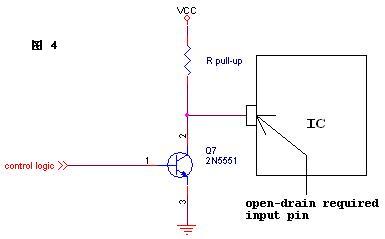

2. 上拉電阻R pull-up的阻值決定了邏輯電平轉換的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

Push-Pull輸出就是一般所說的推輓輸出,在CMOS電路里面應該較CMOS輸出更合適,因為在CMOS裡面的push-pull輸出能力不可能做得雙極那麼大。輸出能力看IC內部輸出極N管P管的面積。和開漏輸出相比,push-pull的高低電平由IC的電源低定,不能簡單的做邏輯操作等。push-pull是現在CMOS電路里面用得最多的輸出級設計方式。

當然open drain也不是沒有代價,這就是輸出的驅動能力很差。輸出的驅動能力很差的說法不準確,驅動能力取決於IC中的末級電晶體功率。OD只是帶來上升沿的延時,因為上升沿是通過外接上拉無源電阻對負載充電的,當電阻選擇小時延時就小、但功耗大,反之延時大功耗小。OPEN DRAIN提供了靈活的輸出方式,但也是有代價的,如果對延時有要求,建議用下降沿輸出。