Quartus ii除錯工具之SignalProbe

下圖是quartusii handbook 給出的6個片上除錯工具,列出了各自的用途。

其中SignalProbe是Quartus ii提供的一個通過外部裝置探測FPGA內部訊號的一個工具,即把FPGA內部需要探測的訊號連線到沒有用到的IO管腳輸出,這樣在外部用示波器等工具就能觀察到該訊號的情況。相比於直接在工程中設定輸出引腳,SignalProbe不會改變原有的設計,只是用了多餘的引腳的來輸出訊號。

SignalProbe使用條件:

(1)有多餘的IO管腳;

(2)目標器件是FPGA或CPLD;

(3)有外部測試裝置,比如邏輯分析儀,示波器。

SignalProbe優點:

(1)編譯時間短;

(2)不改變原有工程的佈局佈線;

(3)不需要JTAG;

(4)即使內部邏輯資源剩餘非常少也可以(此時用其它除錯工具比如signaltapii 等就會導致資源不夠的情況)。

下面介紹下SignalProbe的操作步驟,下面的例子,我通過SignalProbe去觀察內部訊號cnt[0]

1、新建工程,quartusii 13.1 器件EP4CE115F29C8

2、全編譯工程

3、開啟SignalProbe

Tools->SignalProbe Pins

彈出SignalProbe Pins視窗

點選Add…按鈕,彈出新增SignalProbe Pin對話方塊(可以新增多個需要探測的訊號)

4、新增SignalProbe Pin,設定如下圖所示。

Source node name :點選紅框1處的… 按鈕 ,新增需要被探測的節點訊號。我這裡選擇cnt[0]

Pin location: 紅框2處選擇探測的節點訊號需要連線的輸出管腳,選擇PIN_A10

SignalProbe pin name:給SignalProbe管腳取個名字,預設即可

Pipeline registers:設定輸出的訊號是否需要增加流水線暫存器,0表示不需要暫存器

點選紅框3處 OK 按鈕 完成設定。

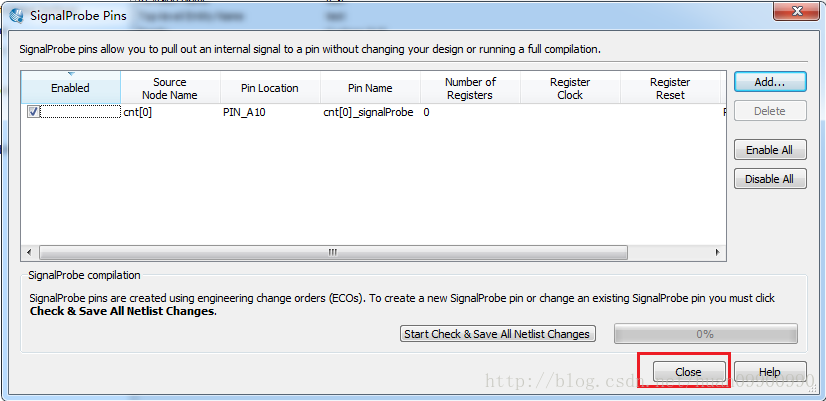

5、點選 Start check 按鈕,生成SignalProbe,當旁邊的進度條為100% 表示成功完成。

6、點選Close 按鈕 退出

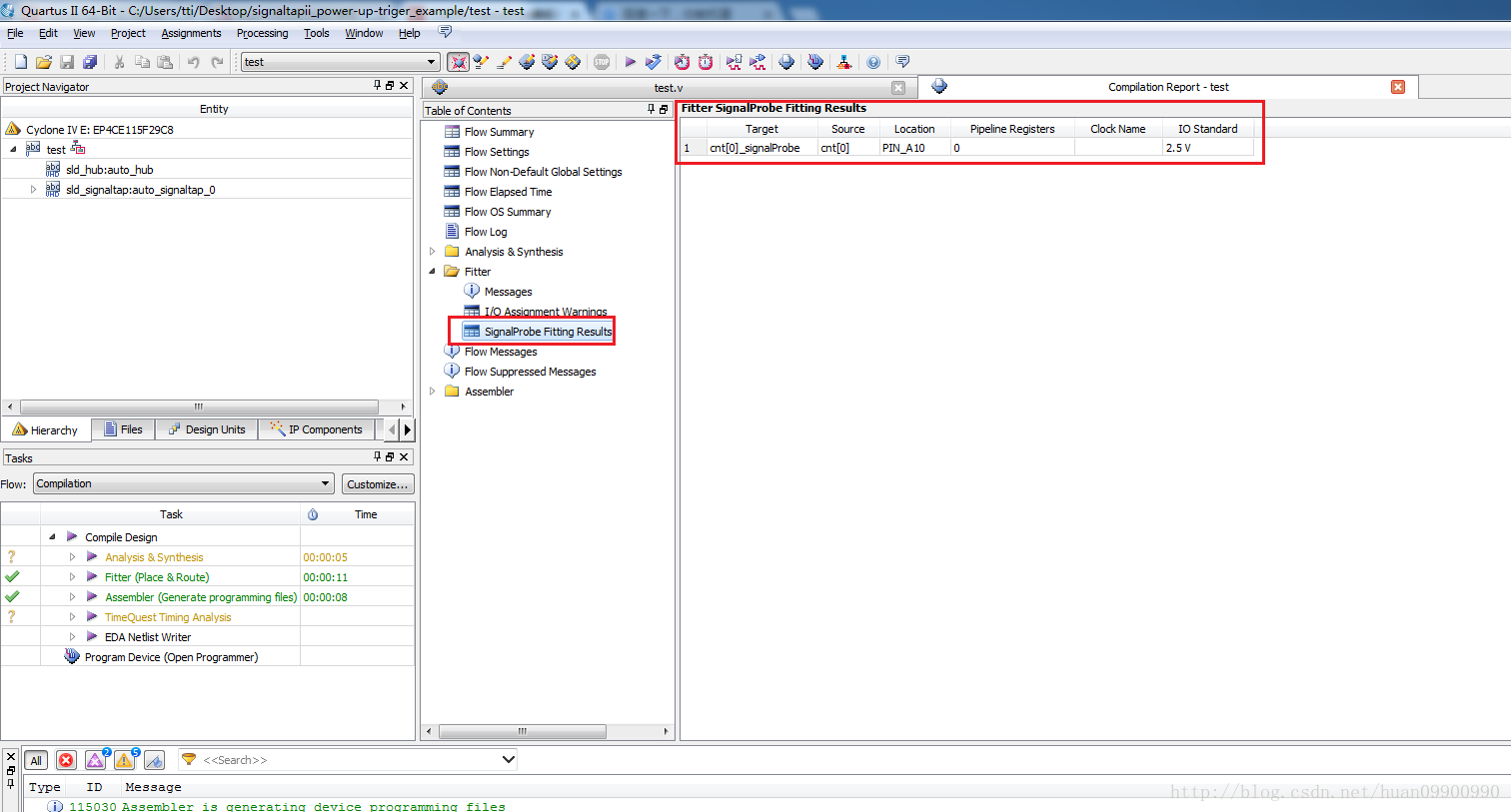

7、在編譯結果的 Fitter->SignalProbe Fitting Results 看見了新增的SignalProbe的資訊

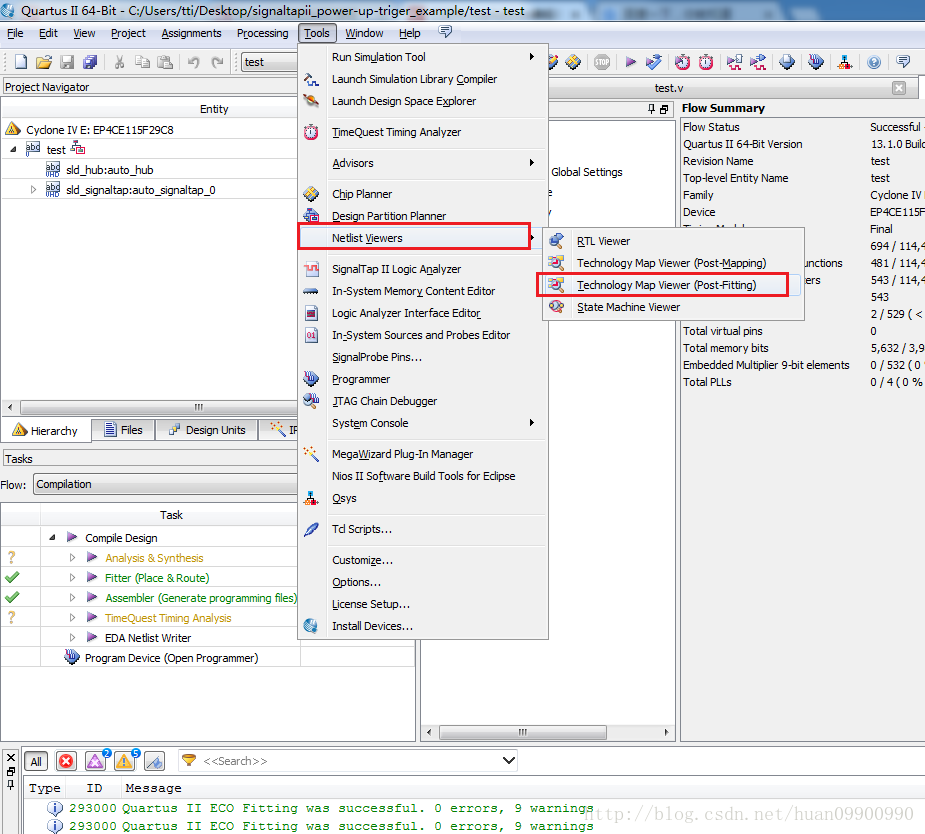

8、檢視 Technology Map Viewer

Tools->Netlist Viewers->Technology Map Viewer(Posting-Fitting)

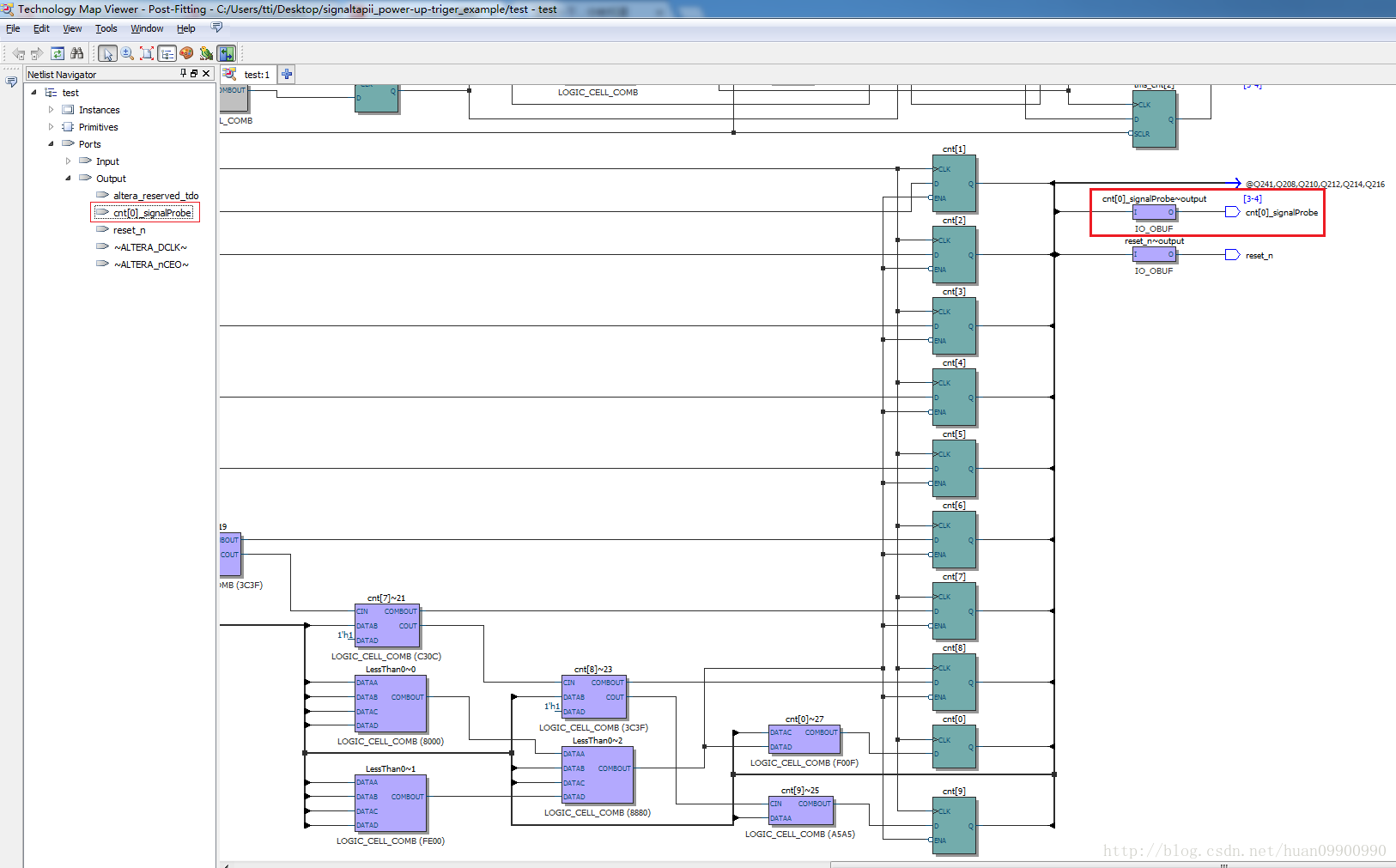

在下圖左邊的test->Ports->Output ->選中cnt[0]_signalProbe 就在右邊的圖裡看見新增的探測管腳了。

9、把.sof 通過JTAG下載到目標器件中,就能通過外部裝置 去探測我們設定的輸出管腳訊號了(PIN_A10)。