組合邏輯LUT和時序邏輯REG

LUT(Look-Up-Table):查詢表。

LUT本質上就是一個RAM。它把資料事先寫入RAM後,

每當輸入一個訊號就等於輸入一個地址進行查表,找出地址對應的內容,然後輸出。

LATCH :就是鎖存器。由電平觸發,非同步控制。在使能訊號有效時latch相當於通路,在使能訊號無效時latch保持輸出狀態。

LUT和LATCH 他們的共同點是:均屬於組合邏輯(和時鐘沒有半點關係)。

不同點是:LUT是FPGA最小單元的組成結構,而LATCH不是。

說道LATCH就不得不提到FF,FF(Flip Flop):觸發器。

那麼DFF就是,眾所周知的D類觸發器。它是邊沿觸發的,歸為時序邏輯。

他和reg又有著什麼關係呢?reg就是由DFF組成的。一個8位的暫存器,就是用了8個同步的D觸發器。

一般一個FPGA最小單元就會包含多個LUT和多個REG,且REG的個數多於LUT。(這個以後再具體分析)

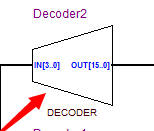

關係都找出來了,我們來做些實驗,看看下列程式碼都能綜合出什麼東西:

實驗1:

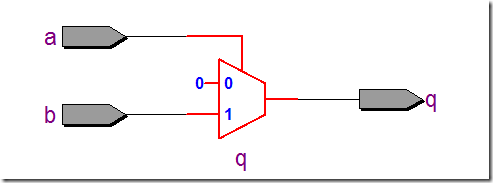

module testlatch ( input a, input b, output reg q ); always @(a or b) if(a == 1'b1) q = b; endmodule

實驗2:

module testlatch ( input a, input b, output reg q ); always @(a or b) if(a == 1'b1) q = b; else q = a; endmodule

實驗3:

module testlatch ( input CLK, input a, input b, output reg q ); always @(posedge CLK) if(a == 1'b1) q = b; endmodule

總結:

1、always (*)或者 assign 綜合出的就是LUT構建的東西,可認為就是LUT。

2、在always (*)的情況下,如果if 或者cace 不完整的話,會綜合出latch,導致不穩定。

3、在always (posedge CLK)的情況下,綜合出的是reg,即使if,或者case不完整,也不會綜合出latch。

4、不要用latch作為模組名,會報錯,這個名字已經被Quartus佔用了。

大家可能會說,並沒有看到LUT,我們知道LUT就是查詢表,去technology Map Viewer,去看看:

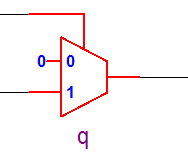

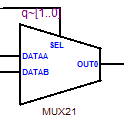

就知道RTL那些 “梯形的選擇器” ,其實就是由LUT構成的!!

梯形選擇器,類似於:

一句話點題:

萬能查表法再加上暫存器就保證了快速運算邏輯,這就是FPGA!

技術討論歡迎加群~~電子技術協會 362584474