FPGA非同步復位同步釋放使用兩級D觸發器的意義

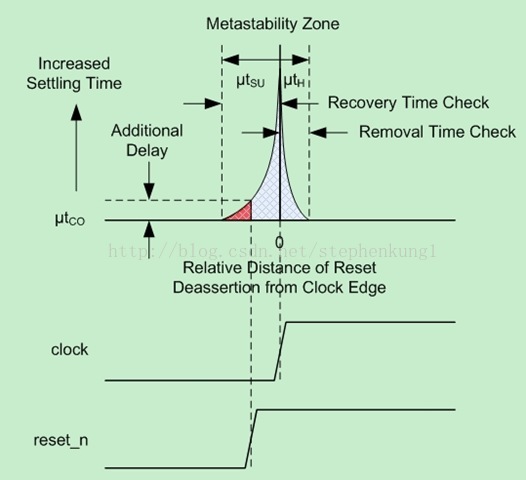

如圖是器件工作時的電壓變化,當reset_n在Recovery Time Check+Removal Time Check時間段內發生變化時會產生一個非高非低的訊號,稱之為亞穩態。如果電路有亞穩態存在會對之後的電路產生無法預測的錯誤,通過比較可得在各模組之間使用非同步電路可以使電路簡單化但會產生亞穩態,在各模組內部使用同步電路以便對電路效能進行測試有利於驗證。因此要在各模組中涉及一個可以有效消除亞穩態的電路。現在比較通用的是非同步復位同步釋放(所謂非同步復位,就是復位訊號可以直接不受時鐘訊號影響,在任意時刻只要是低電平就能復位(假如約定低電平復位),也就是說,復位訊號不需要和時鐘同步。而同步釋放就很有意思了,它的意思是讓復位訊號取消的時候,必須跟時鐘訊號同步,也就是說正好跟時鐘同沿

下面是一個比較通用非同步復位同步釋放的verilog程式碼:

module prac (

clk,

reset_n,

dataa,

datab,

outa,

outb

);

input clk;

input reset_n;

input dataa;

input datab;

output outa;

output outb;

reg reg1;

reg reg2;

reg reg3;

reg reg4;

assign outa = reg1;

assign outb = reg2;

assign rst_n = reg4;

always @ (posedge clk or negedge reset_n) //“非同步復位同步釋放”的復位模組

begin

if (!reset_n)

begin

reg3 <= 1'b0;

reg4 <= 1'b0;

end

else

begin

reg3 <= 1'b1;

reg4 <= reg3;

end

end

always @ (posedge clk or negedge rst_n

begin

if (!rst_n)

begin

reg1 <= 1'b0;

reg2 <= 1'b0;

end

else

begin

reg1 <= dataa;

reg2 <= datab;

end

end

endmodule

綜合後的RTL圖表如下:

這裡的reg1,reg2時域DP實際上是經過reg3,reg4處理過的時域,假設reg3內rese_n與clk產生了亞穩態,由於已知亞穩態產生的電流是一個很小且短暫的訊號那麼當亞穩態的產生電流傳到reg4時因為clk的限制導致傳不到reg1,2,從而達到消除亞穩態的目的(reg4比reg3傳導訊號有一個週期的延遲)或許有人會說如果只加一個觸發器由於clk的限制在reg1,2同樣可以消除亞穩態,為什麼要加兩個?假設亞穩態在傳到reg1,2時正好在clk的上升沿附近那麼此時的亞穩態是沒有辦法消除的,而增加相同時域的D觸發器就是避免此類現象的產生。實際上隨著D觸發器個數的增加亞穩態產生的概率是成平方倍的減少的,根據大量的工作經驗一般在使用兩個觸發器後基本上就能避免亞穩態的產生。

相關推薦

FPGA非同步復位同步釋放使用兩級D觸發器的意義

如圖是器件工作時的電壓變化,當reset_n在Recovery Time Check+Removal Time Check時間段內發生變化時會產生一個非高非低的訊號,稱之為亞穩態。如果電路有亞穩態存在會對之後的電路產生無法預測的錯誤,通過比較可得在各模組之間

FPGA基礎知識11(FPGA非同步復位同步釋放解析)

需求說明:IC設計基礎 內容 :非同步復位,同步釋放 來自 :時間的詩 FPGA開發中,一種最常用的復位技術就是“非同步復位同步釋放”,這個技術比較難以理解,很多資料對其說得並不透徹,沒有講到本質,但是它又很重要,所以對它必須理解,這

FPGA非同步復位同步釋放的詳細解釋

假設rst_async_n撤除時發生在clk上升沿,如果如下電路則可能發生亞穩態事件。 如圖第一個方框內是非同步復位和同步釋放電路。有兩個D觸發器構成。第一級D觸發器的輸入時VCC,第二級觸發器輸出是可以非同步復位,同步釋放後的復位訊號。 電路目的:方式復位訊號撤除時產生亞穩態事件。 所謂非同

FPGA非同步復位同步釋放解析

FPGA開發中,一種最常用的復位技術就是“非同步復位同步釋放”,這個技術比較難以理解,很多資料對其說得並不透徹,沒有講到本質,但是它又很重要,所以對它必須理解,這裡給出我的看法。 講到這個之前,我們要先熟悉recovery time和removal time的概念。如下

非同步復位、同步復位和非同步復位同步釋放的比較

原文地址:http://www.cnblogs.com/yfwblog/p/4793118.htm 簡介 在實際的工程中選擇復位策略之前必須考慮許多設計方面的問題,如使用同步復位或者非同步復位或者非同步復位同步釋放(Asynchronous Reset Synchro

含PLL的lock訊號的非同步復位同步釋放

下圖展示了該結構: 結構分為三部分,分別是PLL的非同步復位同步釋放,PLL模組,和系統的非同步復位同步釋放。 PLL模組由IP核產生,使用非同步復位,當鎖定時候,Locked訊號置位。 非同步復位同步釋放部分當iRstN訊號低電平,

Verilog中同步復位,非同步復位,非同步復位同步釋放

簡介 在實際的工程中選擇復位策略之前必須考慮許多設計方面的問題,如使用同步復位或者非同步復位或者非同步復位同步釋放(Asynchronous Reset Synchronous Release或者Synchronized Asynchronous Reset),以及

FPGA至簡設計法之一:D觸發器、波形、程式碼

在學習verilog之前,我們先學習一下D觸發器以及它的程式碼。 FPGA的設計基礎是數位電路,因此很多同學會認為我們要先學好數位電路之後,才學習FPGA。但是,數位電路教材的內容很多.例如:JK觸發器、RS觸發器、真值表、卡諾圖等。但是,這裡的很多內容其實已經過時了。此外

帶有同步清0、同步置1的D觸發器模組描述及其Testbench測試

1、Verilog描述具有有非同步清0、非同步置1的D觸發器 //同步復位、置位D觸發器模組描述 module D_synctrigger(clk,rst,set,D,Q); input clk,rst,set,D; output Q; reg Q;//暫存器定

FPGA基礎之非同步復位和同步釋放電路的詳細解釋

版權宣告:轉載請註明出處:http://blog.csdn.net/lg2lh https://blog.csdn.net/lg2lh/article/details/8488224 假設rst_async_n撤除時發生在clk上升沿,如果如下電路則可能發生亞穩態事件。

非同步復位,同步釋放的理解

非同步復位,同步釋放的理解 文章轉自: https://blog.csdn.net/u011729865/article/details/49281713 什麼情況下復位訊號需要做非同步復位同步釋放處理 非同步復位同步釋放原理 利用前面兩級

FPGA之同步復位與非同步復位(1)

正常情況下,clk的上升沿c更新為b,b更新為a。一旦進入復位,b,c都清零;但是我們不能確定復位訊號rst_n會在什麼時候結束。如果結束於b_reg0和c_reg0的{launch edge –stup,launch edge+hold}時間只外,那麼一切都會正常。但如果恰恰相反,會出現什麼情況呢? rst

FPGA之同步復位與非同步復位(2)

為了避免純粹的同步復位和純粹非同步復位的問題,可以使用一種叫做同步化的非同步復位,我們稱其為第三類復位。這種復位完全結合了非同步復位和同步復位的優勢,我們知道非同步復位的優勢是不參與資料路徑,所以不影響資料路徑速度,而復位幾乎是瞬間起作用;而同步復位的優勢是百分百地同步時

復位最佳方式:非同步復位,同步釋放

最近在FPGA討論群裡放入一段程式碼讓精英分析一下可行性,結果被鄙視了,並且引起了精英們的大討論 ,總結一下: 起因是我在一個工程中混雜使用同步復位,非同步復位; 非同步: always @(posedge clk or negedge rst_n )

非同步復位和同步釋放電路的詳細解釋

1、首先給出非同步復位訊號亞穩態的原因: 復位結束也就是釋放的時刻恰在時鐘上升沿的建立時間和保持時間之間時無法決定現在的復位狀態是1還是0,造成亞穩態。 下面是具體解釋: 在帶有復位端的D觸發器中,當reset訊號“復位”有效時,它可以直接驅動最後一級的與非門,

verilog非同步復位,同步釋放

<div id="article_content" class="article_content clearfix csdn-tracking-statistics" data-pid="blog" data-mod="popu_307" data-dsm="post

為什麼要非同步復位,同步釋放

一個簡單的非同步復位的例子 1 module test 2 ( 3 input clk, 4 input rst_n, 5 input data_in, 6 output reg out 7 ); 8 alw

【Verilog】 同步復位和非同步復位比較 async vs. sync

同步復位 sync 非同步復位 async 特點 復位訊號只有在時鐘上升沿到來時才能有效。 無論時鐘沿是否到來,只要復位訊號有效,就進行復位。

verilog同步復位和非同步復位

1、阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在程序語句(initial和always)中,當前的賦值語句阻斷了其後的語句,也就是說後面的語句必須等到當前的賦值語句執行完畢才能執行。而且阻塞賦值可以看成是一步完成的,即:計算等號右邊的值並同時賦給左邊變數。例如: 當執行“x=next_x;”時,x會

同步復位和非同步復位的對比

復位分為同步復位和非同步復位。 同步復位的優點: 1.抗干擾性高,可以剔除復位訊號中週期短於時鐘週期的毛刺。 2.有利於靜態時序分析工具的分析。 3.有利於基於週期的模擬工具的模擬。 同步復位的缺點: