S3C2440系統時鐘

++++++++++++++++++++++++++++++++++++++++++

本文系本站原創,歡迎轉載! 轉載請註明出處:

MINI2440開發板在沒有開啟時鐘前,整個開發板全靠一個12MHz的晶振提供頻率來執行,也就是說CPU,記憶體,UART等需要用到時鐘頻率的硬體都工作12MHz下,而S3C2440A可以正常工作在400MHz下,兩者速度相差可想而知,就好比牛車和動車。如果CPU工作在12MHz頻率下,開發板的使用效率非常低,所有依賴系統時鐘工作的硬體,其工作效率也很低,比如,我們電腦裡面經常提到的超頻,超頻就是讓CPU工作在更高的頻率下,讓電腦運算速度更快,雖然頻率是越高越好,但是由於硬體特性決定了任何一個裝置都不可能無止境的超頻,電腦超頻時要考慮到

lFCLK:400MHz

lHCLK:100MHz

lPCLK:50MHz

既然如此,那麼怎樣讓CPU工作在400MHz,讓牛車速度提高到動車的速度呢?

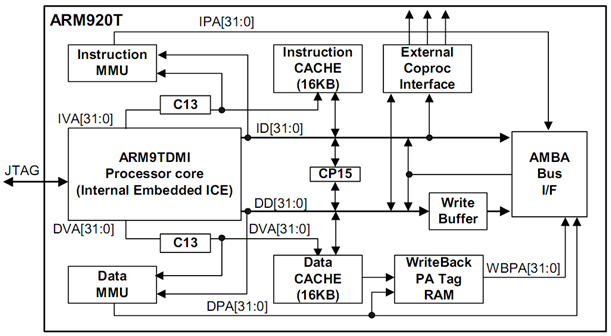

在對系統時鐘進行提速之前,讓我們先來了解下S3C2440上的工作時鐘頻率,FCLK,HCLK,PCLK,其中FCLK主要為ARM920T核心提供工作頻率,如圖2-44所示:

圖2-44ARM920T核心結構

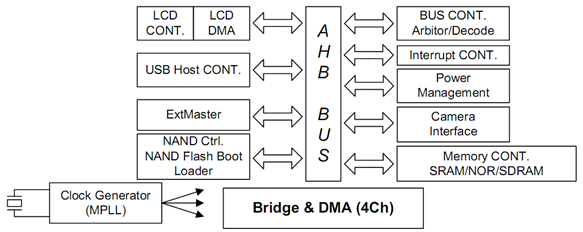

HCLK主要為S3C2440

AHB匯流排(Advanced High performance Bus

圖2-45 S3C2440 AHB總線上掛接硬體

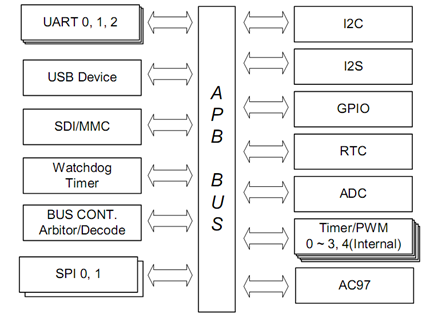

PCLK主要為APB匯流排提供工作頻率,由圖2-46所示,APB匯流排主要掛接UART串列埠,Watchdog等硬體控制器。

圖2-46 S3C2440 APB匯流排掛接硬體

也就是說,對於一些需要時鐘工作的硬體,如果切斷其時鐘源,就不會再工作,從而達到降低功耗的目的,這也是便攜嵌入式裝置裡的一個特點。

時鐘源:為了減少外界環境對開發板電磁干擾,降低製作成本,通常開發板的外部晶振時鐘頻率都很低,MINI2440開發板由

S3C2440裡有兩個PLL:MPLL和UPLL,MPLL用來產生FCLK,HCLK,PCLK的高頻工作時鐘,UPLL用來為USB提供工作頻率。

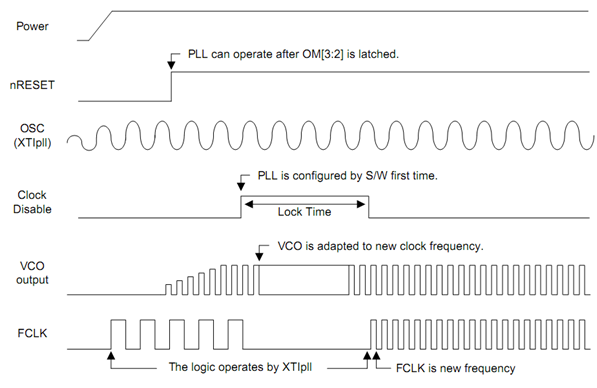

圖2-47系統時鐘初始化時序

開發板上電後,晶振OSC開始提供晶振時鐘,由於系統剛剛上電,電壓訊號等都還不穩定,這時復位訊號(nRESET)拉低,這時MPLL雖然預設啟動,但是如果不向MPLLCON中寫入值,那麼外部晶振則直接作為系統時鐘FCLK,過幾毫秒後,復位訊號上拉,CPU開始取指執行,這時可以通過程式碼設定啟動MPLL,MPLL啟動需要一定鎖定時間(LockTime),這是因為MPLL輸出頻率還沒有穩定,在這期間FCLK都停止輸出,CPU停止工作,過了LockTime後時鐘穩定輸出,CPU工作在新設定的頻率下,這時可以通過設定FCLK,HCLK和PCLK三者的頻率比例來產生不同總線上需要的不同頻率,下面詳細介紹開啟MPLL的過程:

l設定LockTime變頻鎖定時間

l設定FCLK與晶振輸入頻率(Fin)的倍數

l設定FCLK,HCLK,PCLK三者之間的比例

LockTime變頻鎖定時間由LOCKTIME暫存器(見下表)來設定,由於變頻後開發板所有依賴時鐘工作的硬體都需要一小段調整時間,該時間計數通過設定LOCKTIME暫存器[31:16]來設定UPLL(USB時鐘鎖相環)調整時間,通過設定LOCKTIME暫存器 [15:0]設定MPLL調整時間,這兩個調整時間數值一般用其預設值即可。

表2-8變頻鎖定時間暫存器(LOCKTIME)

|

暫存器名 |

地址 |

是否讀寫 |

描述 |

復位預設值 |

|

LOCKTIME |

0x4C000000 |

R/W |

變頻鎖定時間暫存器 |

0xFFFFFFFF |

|

LOCKTIME |

位 |

描述 |

初始值 |

|

U_TIME |

[31:16] |

UPLL對UCLK的鎖定時間值 (U_TIME:300us) |

0xFFFF |

|

M_TIME |

[15:0] |

MPLL對於FCLK,HCLK,PCLK的鎖定時間值(M_TIME:300us) |

0xFFFF |

FCLK與Fin的倍數通過MPLLCON暫存器設定,三者之前有以下關係:

MPLL(FCLK) = (2*m*Fin)/(p*2^s)

其中:m = MDIV + 8, p = PDIV + 2, s = SDIV

當設定完MPLL之後,就會自動進入LockTime變頻鎖定期間,LockTime之後,MPLL輸出穩定時鐘頻率。

表2-9 MPLL配置暫存器(MPLLCON)

|

暫存器名 |

地址 |

是否讀寫 |

描述 |

復位預設值 |

|

MPLLCON |

0x4C000004 |

R/W |

MPLL配置暫存器 |

0x00096030 |

|

MPLLCON |

位 |

描述 |

初始值 |

|

MDIV |

[19:12] |

主分頻器控制位 |

0x96 |

|

PDIV |

[9:4] |

預分頻器控制位 |

0x03 |

|

SDIV |

[1:0] |

後分頻器控制位 |

0x0 |

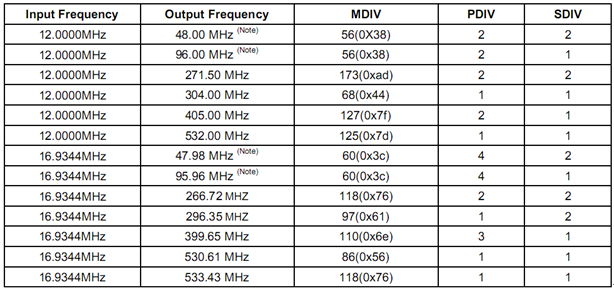

通過上述演算法比較難以找到合適的PLL值,下表給出了官方推薦的一些MPLL參考設定:

表2-10 官方推薦MPLL

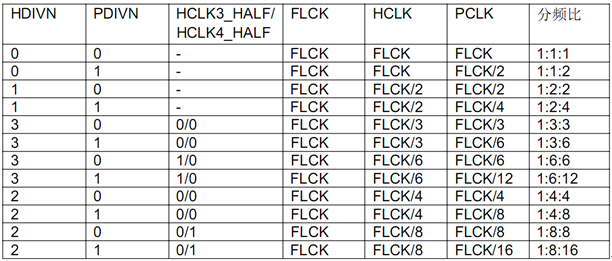

FCLK,HCLK,PCLK三者之間的比例通過CLKDIVN暫存器進行設定,S3C2440時鐘設定時,還要額外設定CAMDIVN暫存器,如下表,HCLK4_HALF,HCLK3_HALF分別與CAMDIVN[9:8]對應,下表列出了各種時鐘比例:

表2-11 FCLK HCLK PCLK設定比例

如果HDIV設定為非0,CPU的匯流排模式要進行改變,預設情況下FCLK = HCLK,CPU工作在fast bus mode快速匯流排模式下,HDIV設定為非0後, FCLK與HCLK不再相等,要將CPU改為asynchronous bus mod非同步匯流排模式,可以通過下面的嵌入彙編程式碼實現:

__asm{

mrc p15, 0, r1, c1, c0, 0 /* 讀取CP15 C1暫存器 */

orr r1, r1, #0xc0000000 /* 設定CPU匯流排模式 */

mcr p15, 0, r1, c1, c0, 0 /* 寫回CP15 C1暫存器 */

}

關於mrc與mcr指令,請檢視MMU與記憶體保護的實現章節。

表2-12時鐘分頻器控制暫存器(CLKDIVN)

|

暫存器名 |

地址 |

是否讀寫 |

描述 |

復位預設值 |

|

CLKDIVN |

0x4C000014 |

R/W |

時鐘分頻器控制暫存器 |

0x00000000 |

|

CLKDIVN |

位 |

描述 |

初始值 |

|

DIV_UPLL |

[3] |

UCLK選擇暫存器(UCLK必須對USB提供48MHz) 0:UCLK=UPLL clock 1:UCLK=UPLL clock/2 |

0 |

|

HDIVN |

[2:1] |

00:HCLK = FCLK/1 01:HCLK = FCLK/2 10:HCLK = FCLK/4,當CAMIVN[9]=0 HCLK = FCLK/8,當CAMIVN[9]=1 11: HCLK = FCLK/3,當CAMIVN[8]=0 HCLK = FCLK/6,當CAMIVN[8]=1 |

0 |

|

PDIVN |

[0] |