FPGA源同步輸出時序約束(一)

下文主要介紹源同步輸出時,輸出時鐘的幾種產生方式以及相應的時鐘約束指令

源同步輸出的訊號有時鐘和資料訊號,輸出時鐘是由fpga產生的,對於輸出時鐘有多種產生方式,例如:

1、通過fpga的鎖相環產生輸出時鐘;

2、通過fpga的ALTDDIO IP核產生輸出時鐘;

3、通過狀態機控制產生輸出時鐘;

4、將驅動資料的時鐘直接輸出。

通過產生時鐘直接作為輸出時鐘 和用一個時鐘去驅動ALTDDIO IP核 產生輸出時鐘 這兩種是比較常用的方式。在fpga裡驅動資料輸出用的時鐘和 用來驅動ALTDDIO IP核 的時鐘 可以是由相同的鎖相環產生的,也可以是由不同的鎖相環產生的。具體要看你輸出的訊號型別

以下情況可以用同一個鎖相環:

(1)中心或邊沿對齊的SDR輸出;

(2)邊沿對齊的DDR輸出。

以下情況應該用不同的鎖相環:

(1)中心對齊的DDR輸出;

(2)一個時鐘直接作為驅動外部器件的時鐘(這樣可以補償時鐘和資料間的不同延遲);

(3)輸出時鐘和資料中心或邊沿對齊(比如時鐘和資料延遲50°,這樣的話就只能用鎖相環去生成對應的延遲);

(4)精確除錯時鐘和資料間的相位關係

下面是幾種常用的時鐘輸出方式及時鐘約束命令:

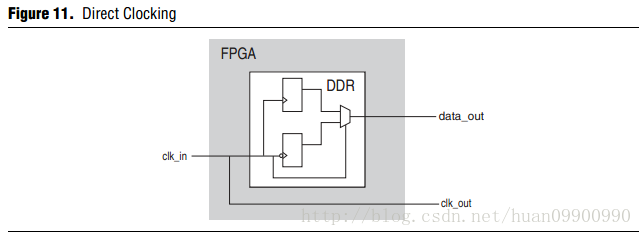

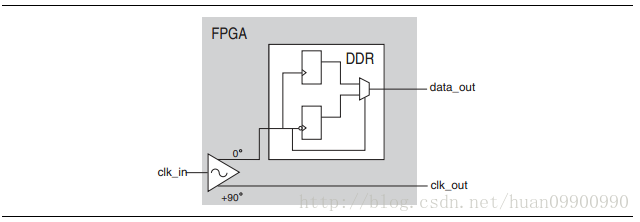

1、輸入時鐘直接輸出:

輸入fpga的時鐘直接用來作為輸出的時鐘和傳送資料的時鐘

對輸入fpga的時鐘和輸出時鐘做約束,命令如下:

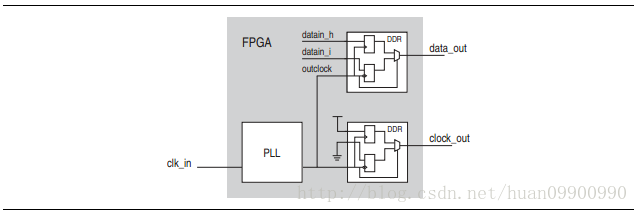

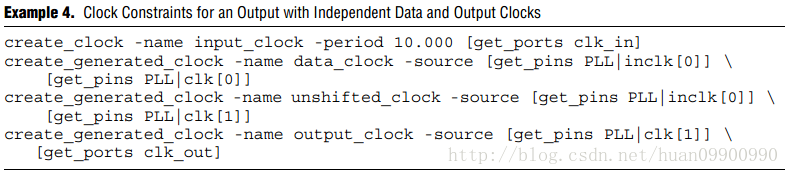

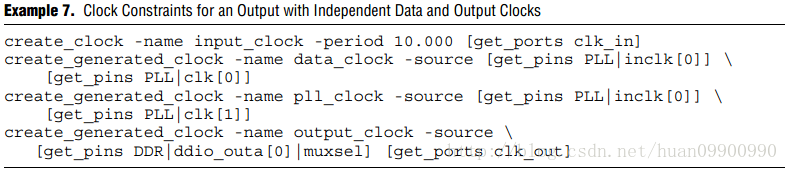

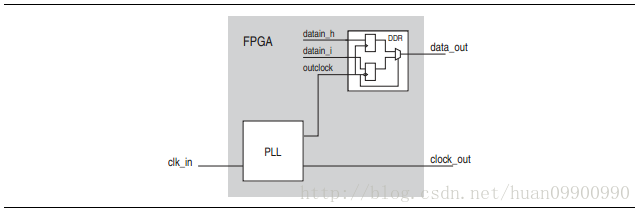

2、用鎖相環來產生兩個獨立的時鐘:輸出時鐘和資料時鐘。

輸出時鐘和資料邊沿對齊。

此時需與約束的時鐘有:輸入fpga時鐘clk_in,通過鎖相環生成的兩個時鐘,以及輸出fpga的時鐘clk_out

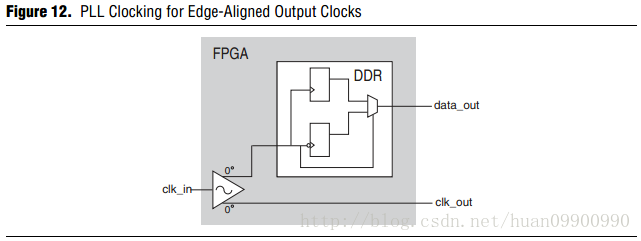

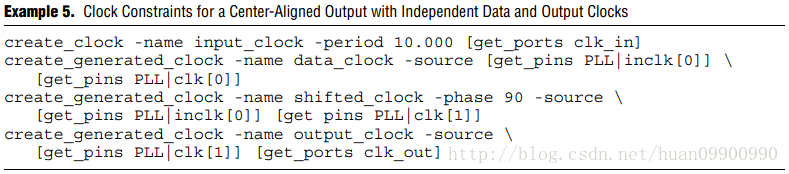

3、DDR輸出資料與時鐘中心對齊

此時輸出的時鐘相對於輸出資料有一個90°的相位偏移,用PLL去產生一個相對於資料有90°偏移的時鐘。

此時約束輸出時鐘有一個90°的相位偏移

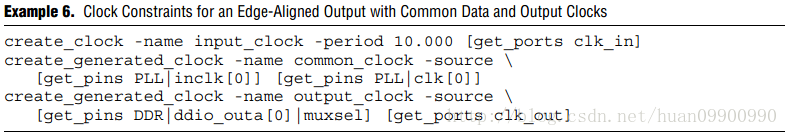

4、DDR輸出時,輸出時鐘和資料時鐘共用一個時鐘,輸出時鐘通過例化的ALTDDIO IP核輸出

約束指令如下:

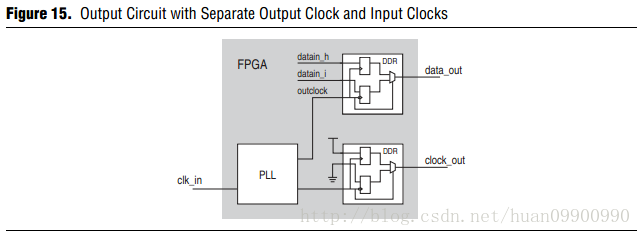

5、同一鎖相環產生驅動ALTDDIO 模組時鐘和資料時鐘

PLL輸出的兩個埠 一個輸出時鐘傳送到外部器件, 一個輸出時鐘用來發送資料到外部器件

約束指令如下:

6、同一鎖相環產生輸出到外部的時鐘和驅動資料傳送的時鐘

約束指令如下: