kinetis時鐘模組MCG詳解

MCG模組詳解

一、MCG模組簡介

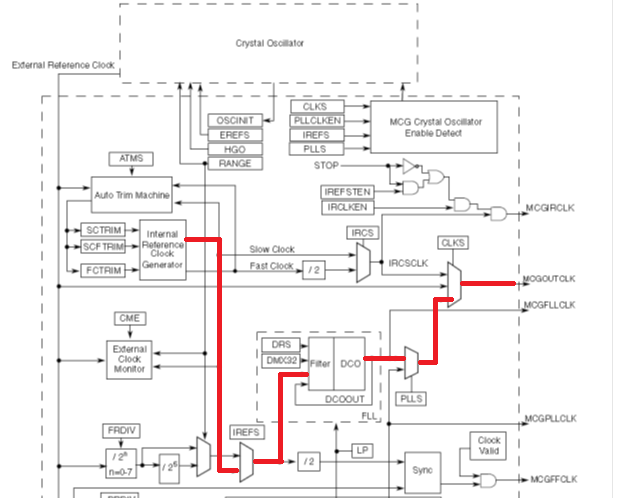

MCG成為多用途時鐘訊號發生器,該模組為MCU和晶片內部各個模組提供時鐘訊號。MCG模組通過對輸入的參考時鐘進行分頻和倍頻處理,可以輸出各種頻率的時鐘訊號,並達到超頻執行的目的。輸入的參考時鐘可以來自內部也可以來自外部時鐘或外部晶振。輸入的參考時鐘一般經過分頻後進入FLL(鎖頻環)或PLL(鎖相環)進行倍頻處理,當然也可以不通過FLL或PLL,而直接輸出給各個模組。一般情況下,我們會選擇外部晶振的參考時鐘,分頻後由PLL倍頻的方法來達到超頻執行的目的。

MCG模組框圖如圖1.1所示。

圖1.1 MCG模組框圖

MCG的核心是一個FLL(鎖頻環)和一個PLL(鎖相環)。FLL和PLL都可以對輸入的參考時鐘倍頻並鎖定後輸出,輸出的時鐘在SIM模組的控制下提供給CPU和各個模組。鎖頻環FLL的核心是一個DCO(數字控制振盪器),鎖相環PLL的核心是一個VCO(電壓控制振盪器)。如圖1.2所示。

注意:MCG模組可輸出多個時鐘,比如MCGFFCLK、MCGPLLCLK、MCGOUTCLK等,詳見圖1.1。這些時鐘可以為其它模組提供更多的時鐘選擇。在這些時鐘中,最主要的是MCGOUTCLK。這個時鐘是核心時鐘、匯流排時鐘、FLASH時鐘的時鐘來源。我們要實現PLL超頻最終得到的也是MCGOUTCLK。

圖1.2 MCG模組

不同的參考時鐘,以及不同的對參考時鐘的處理方式的組合,使得MCG模組有9種不同的工作模式。9種模式及相互之間的轉換如圖1.3所示。

圖1.3 MCG模組的工作模式及相互轉換

這9種模式我們未必都用到,一般情況下,我們都會使用PEE模式,PEE模式是選擇外部晶振經過PLL倍頻後輸出時鐘,可以達到較高的時鐘頻率。而上電覆位後,MCG工作在FEI模式下。我們必須通過設定相關的暫存器,實現FEI到FBE的轉換,再由FBE轉換到PBE,最後再轉換到PEE。下面我們就介紹一下我們用到的幾種模式及在轉換過程中用到的暫存器。

二、相關暫存器

1. MCG控制暫存器1(MCG_C1)

|

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Read |

CLKS |

FRDIV |

IREFS |

IRCLKEN |

IREFSTEN |

|||

|

Write |

||||||||

|

Reset |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

圖1.4 MCG_C1暫存器

CLKS:時鐘源選擇。該位用於選擇MCG的輸出時鐘MCGOUTCLK從何而來。在MCG的模式轉換過程中,每一步都牽涉到CLKS的設定。注意,每次改變CLKS,輸出的時鐘並不是馬上發生變化,而是有一個過程,必需查詢相關的標誌位以確保轉換完成才能進行下一步設定,需查詢的相關標誌位在MCG_S暫存器中,有關該暫存器的內容稍後介紹。

圖1.5 CLKS選擇輸出時鐘

CLKS選擇時鐘如表1.1所示

|

CLKS |

描述 |

|

00 |

選擇PLL或FLL輸出 |

|

01 |

選擇內部參考時鐘 |

|

10 |

選擇外部參考時鐘 |

|

11 |

保留,預設為00 |

表1.1CLKS選擇輸出時鐘

FRDIV:鎖頻環FLL外部參考分頻。當FLL的輸入參考時鐘來自外部晶振時,可通過設定FRDIV對這個來自晶振的參考時鐘分頻。分頻後的時鐘可以提供給FLL再倍頻,並且這個時鐘也可以提供給MCGFFCLK輸出。對於有些模組,比如FTM,MCGFFCLK也是可供選擇的一個時鐘選項。FRDIV的分頻係數和外部晶振的頻率範圍有關,頻率範圍在MCG_C2暫存器中的RANGE設定。

RANGE=0,分頻比=2^FRDIV(FRDIV<=7),如果外部晶振RANGE!=0,則分頻比=2^(FRDIV+5)。

注意:分頻後提供給FLL倍頻的參考時鐘不得超過32K。

IREFS:FLL參考時鐘源選擇。FLL對輸入的參考時鐘倍頻,而這個參考時鐘可以來自晶片自帶的內部慢速參考時鐘,速率為32k,也可以來自外部晶振經由FRDIV設定的分頻比分頻後的時鐘。選擇哪一個輸入到FLL由IREFS設定。

IREFS=0:選擇外部時鐘;

IREFS=1: 選擇內部慢速參考時鐘源。

注意,上電覆位時,IREFS預設為1,即FLL對32K內部慢速時鐘倍頻後輸出。

IRCLKEN、IREFSTEN:前面提到,MCG模組有多個時鐘輸出,其中一個就是MCGIRCLK,這個時鐘來自於晶片內部自帶的參考時鐘,這個時鐘也可以提供給某些模組作為時鐘選項。IRCLKEN和IREFSTEN就是和這個時鐘有關。如圖1.6所示。如需要這個時鐘,可設定IRCLKEN=1,如希望在停止模式下,該時鐘也可以使用,則可設定IREFSTEN=1。在超頻過程中,這兩位可暫時忽略。

圖1.6 MCGIRCLK輸出設定

2. MCG控制暫存器2(MCG_C2)

圖1.7 MCG_C2暫存器

RANGE:晶振頻率範圍選擇,用於為使用的外部晶振選擇頻率範圍,具體如表1.2所示

|

RANGE |

描述 |

|

00 |

為晶振選擇低頻範圍1K~32K |

|

01 |

為晶振選擇高頻範3M~8M |

|

1X |

為晶振選擇甚高頻範圍8M~32M |

表1.2 RANGE選擇

注意:一般情況下,如果使用32K晶振,則可選擇RANGE=00,如晶振頻率為3~32MHz,則可選擇RANGE=01,如果使用更高頻率的晶振,則可選擇RANGE=1X。

HGO:高增益振盪器選擇

HGO=0:設定晶振為低功耗操作;

HGO=1:設定晶振為高增益操作。

EREFS:外部參考選擇。來自外部的時鐘訊號可以是外部直接輸入的時鐘脈衝,或來自晶體振盪器,可通過EREFS選擇。

EREFS=0:外部參考時鐘;

EREFS=1:外部振盪器。

注意:一般情況下,我們使用都是外部晶振,該位置1即可。

LP:低功耗選擇,用於選擇在bypass等模式下,FLL和PLL是否工作,主要出於省電考慮,超頻過程中,該位可暫不考慮,預設即可。

IRCS:內部參考時鐘選擇。如果我們選擇把晶片自帶的內部時鐘作為MCGOUTCLK輸出,即設定MCG_C1暫存器中的CLKS=01,則有兩個選擇,一個是32K的慢速時鐘,一個是2M的快速時鐘,由IRCS選擇。在PLL超頻過程中,該位可忽略。

IRCS=0:選擇慢速內部參考時鐘;

IRCS=1:選擇快速內部參考時鐘。

3. MCG控制暫存器5(MCG_C5)

圖1.8 MCG_C5暫存器

PLLCLKEN:PLL時鐘使能。MCGPLLCLK也是MCG模組輸出的一個時鐘選項。如果要使能這個時鐘輸出,則設定PLLCKEN=1即可。PLLCLKEN和我們要超頻輸出的MCGOUTCLK無關,在PLL超頻過程中可忽略。如果使用MCGPLLCLK的話,需要注意,置位PLLCLKEN之前,PRDIV需要設定合適的分頻係數以產生2~4M的PLL參考時鐘,置位PLLCLKEN將使能外部振盪器。每次置位PLLCLKEN使能PLL時鐘,並且外部振盪器作為參考時鐘,都需要檢查OSCINIT位。

PLLSTEN:設定stop模式下,PLL是否使能。PLL超頻過程中,該位可忽略。

PRDIV:PLL外部參考時鐘分頻。我們選擇外部晶振作為參考時鐘輸入到PLL時,需要先分頻到2~4MHz的範圍內才可以由PLL倍頻後輸出。PRDIV就是設定對外部時鐘的分頻係數。

分頻係數=PRDIV+1,注意PRDIV<=24。

注意:通過設定PRDIV,結果頻率應在2M~4M範圍內,當PLL使能,即將PLLCLKEN置1後,在鎖相環PLL未鎖定頻率之前,不可改變PRDIV的值。

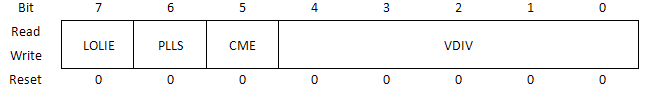

4. MCG控制暫存器6(MCG_C6)

圖1.9 MCG_C6暫存器

LOLIE:當時鍾失去鎖定時,是否發生中斷請求。

LOLIE=0:禁止中斷請求;

LOLIE=1:允許中斷請求。

PLLS:PLL選擇,選擇PLL還是FLL作為MCG的時鐘源。當CLKS[1:0]=00時,我們可以選擇MCGOUTCLK來自PLL或者FLL。到底是PLL還是FLL則由PLLS指定。

PLLS=0:選擇FLL;

PLLS=1:選擇PLL,設定PLLS之前,需要設定合適的PRDIV以產生2~4M的參考時鐘。

CME:時鐘監控使能,設定當失去外部時鐘時,是否產生中斷。

VDIV:PLL壓控振盪器倍頻係數,VDIV決定參考時鐘的倍數。當我們最終選擇PLL倍頻後輸出到MCGOUTCLK時,需要設定VDIV得到我們需要的時鐘頻率。

倍數=VDIV+24,且VDIV<=31。

注意:PLL最大55倍頻,參考時鐘最大4MHz,也就是PLL超頻最高到220MHz。

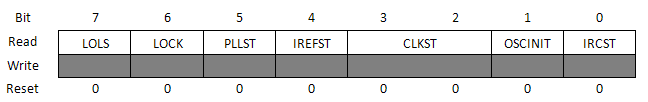

5. MCG狀態暫存器(MCG_S)

這個暫存器中包含反映MCG狀態的標誌位,供程式查詢。在MCG的模式轉換過程中,我們必須查詢該暫存器中的某些標誌位以確保轉換完成。

1.10 MCG_S暫存器

LOLS:該位反映鎖相環的鎖定狀態,失鎖時置 1,寫1清除,該位置1時,由MCG_CR6中的LOLIE決定是否產生中斷。

LOCK:該位置1表示鎖相環已經鎖定。在鎖定過程中,MGC的PLL時鐘被禁止輸出,直到LOCK置位。LOCK置位後,任何改變PRDIV或VDIV的操作都會清除LOCK位直到再次鎖定頻率。

PLLST:該位指示,PLLS的時鐘源是來自FLL時鐘還是PLL時鐘。當我們改變PLLS在PLL和FLL時鐘之間切換時,時鐘輸出的變化需要查詢該位以確保切換完成。

PLLST=0:FLL時鐘;

PLLST=1:PLL時鐘。

IREFST:FLL內部參考時鐘狀態。當我們改變IREF,對FLL的參考時鐘的來源切換時,需要查詢該位以確保切換完成才可進行下一步。

IREFST=0:FLL參考時鐘來自外部;

IREFST=1:FLL參考時鐘來自內部。

CLKST:指示當前的時鐘模式。當我們改變CLKS,改變MCGOUTCLK的時鐘來源時,需要查詢該位以確保切換完成才可進行下一步。

CLKST=00:選擇FLL輸出;

CLKST=01:選擇內部參考時鐘;

CLKST=10:選擇外部參考時鐘;

CLKST=11:選擇PLL輸出。

OSCINT:晶振初始化狀態,該位置1表示晶振完成初始化。

IRCST:內部參考時鐘狀態。如改變IRCS,則須查詢該位,該位和PLL超頻無關。

IRCST=0:選擇慢速內部時鐘,32K;

IRCST=1:選擇快速內部時鐘,2M。

MCG模組和PLL超頻有關的暫存器都已經列出來,還有些暫存器和PLL超頻無關,不做詳細介紹,如想進一步瞭解可參考資料手冊,K10P100M100SF2RM.pdf第24章。

模式轉換

如圖1.3所示,我們必須通過設定相關的暫存器,實現FEI到FBE的轉換,再由FBE轉換到PBE,最後再轉換到PEE。

1. FEI轉換到FBE

FEI模式下,時鐘的產生如圖1.11所示。FEI是系統復位後MCG預設的工作模式,輸出的時鐘MCGOUTCLK來自FLL。FLL的參考時鐘來自內部32K慢速時鐘,FLL倍頻後大約20MHz。

圖1.11 FEI模式下時鐘產生流程

FBE模式下,時鐘的產生如圖1.12所示。在FBE模式下,MCGOUTCLK來自外部參考時鐘,此時,FLL仍正常工作,但是FLL的參考時鐘輸入從內部慢速時鐘切換到外部時鐘。此時FLL產生的時鐘並不輸出。

圖1.12 FBE模式下時鐘產生流程

從FEI到FBE的轉換,主要改變的是MCGOUTCLK的來源從FLL切換到外部晶振,即MCG_C1暫存器的CLKS從00切換到10。同時FLL的參考時鐘也從內部32K慢速時鐘切換到晶振分頻後的時鐘,即MCG_C2暫存器中RANGE、HGO和EREFS都需要設定,而且MCG_C1暫存器中的FRDIV也需要合理設定以保證外部晶振分頻後得到不大於32KHz的參考時鐘提供給FLL。

以4MHz外部晶振為例,首先設定MCG_C2暫存器,程式碼如下:

MCG_C2 = MCG_C2_RANGE(1) | MCG_C2_HGO_MASK | MCG_C2_EREFS_MASK;使用4MHz晶振,RANGE設定為1;HGO置1,選擇高增益;EREFS置1,選擇外部晶振。在這段程式碼中,大量採用系統自帶的巨集定義,具體和查詢標頭檔案MK10X256VMD100.h。使用系統自帶的巨集定義可防止自己計算二進位制出錯,當然,也可以不使用,巨集定義,而直接定義:

MCG_C2=0X1C;接下來設定,MCG_C1暫存器,程式碼如下:

MCG_C1 = MCG_C1_CLKS(2) | MCG_C1_FRDIV(3);CLKS設為10,選擇外部參考時鐘輸出到MCGOUTCLK;FRDIV置為3,對4MHz晶振256分頻。注意分頻後的時鐘只需要小於32KHz即可,由於FBE只是過渡狀態,所以不必詳細計算。同樣,上面的程式碼我們也使用了系統自帶的巨集定義。

當設定完畢後,需查詢MCG_S中的幾個狀態位以確保狀態切換完成,才能進行後面的操作,查詢狀態位的程式碼如下:

while (!(MCG_S & MCG_S_OSCINIT_MASK)){} //等待鎖相環初始化結束

while (MCG_S & MCG_S_IREFST_MASK){} //等待時鐘切換到外部參考時鐘

while (((MCG_S & MCG_S_CLKST_MASK) >> MCG_S_CLKST_SHIFT)!= 0x2){} //等待MCGOUTCLK切換到外部時鐘輸出2. FBE切換到PBE

PBE模式下,MCGOUTCLK輸出時鐘不變,仍然是外部晶振直接輸出,所以MCG_C1中的CLKS不必改變。也就是PBE下的時鐘產生和圖1.2是一樣的。但是,在這一步,我們開始啟用PLL工作,並計算好我們需要超頻的倍率。在PBE模式下,PLL雖然已正常工作,PLL的時鐘並不輸出。在這一步,我們只要設定MCG_C5和MCG_C6兩個暫存器。

MCG_C5 = MCG_C5_PRDIV(1);//分頻在2~4MHz之間,分頻後頻率2MHz

MCG_C6 = MCG_C6_PLLS_MASK |MCG_C6_VDIV(26); //選擇PLL,倍頻50倍這裡我們需要設定好MCGOUTCLK提供給系統核心、匯流排和FLASH的時鐘分頻,通過SIM模組的SIM_CLKDIV1來設定,由MCGOUTCLK提供給幾個主要模組的時鐘分頻比,分別是CORE、BUS、FLEXBUS、FLASH。注意FLASH模組不可超過25MHz,否則出錯。

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0)| SIM_CLKDIV1_OUTDIV2(1)

| SIM_CLKDIV1_OUTDIV3(1) |SIM_CLKDIV1_OUTDIV4(3);

//MCG=PLL, core = MCG, bus = MCG/3,FlexBus = MCG/3, Flash clock= MCG/8如按以上分頻設定,當最終轉換到FEE模式後,則系統核心頻率為100MHz,BUS和FLEXBUS都為50MHz,FLASH為25MHz。

設定完畢後,需查詢標誌位以確保轉換完成。程式碼如下:

while (!(MCG_S &MCG_S_PLLST_MASK)){}; // 等待切換到PLL

while (!(MCG_S &MCG_S_LOCK_MASK)){}; //等待PLL鎖定頻率3. PBE切換到PEE

在上面完成後,PLL輸出的時鐘已經準備完畢,只需要最後通過設定MCG_C1中的CLKS,把MCGOUTCLK的來源從外部晶振切換到PLL時鐘即可。程式碼如下:

MCG_C1 &= ~MCG_C1_CLKS_MASK;//CLKS=00,PLL輸出

while (((MCG_S & MCG_S_CLKST_MASK)>> MCG_S_CLKST_SHIFT) != 0x3){};//等待切換完畢。