【DSP開發】序列 RapidIO: 高效能嵌入式互連技術

摘要

序列RapidIO針對高效能嵌入式系統晶片間和板間互連而設計,它將是未來十幾年中嵌入式系統互連的最佳選擇。

本文比較RapidIO和傳統互連技術的優點;介紹RapidIO協議架構,包格式,互連拓撲結構以及序列RapidIO物理層規範。介紹序列RapidIO在無線基礎設施方面的應用。

RapidIO 與傳統嵌入互連方式的比較

隨著高效能嵌入式系統的不斷髮展,晶片間及板間互連對頻寬、成本、靈活性及可靠性的要求越來越高,傳統的互連方式,如處理器匯流排、PCI匯流排和乙太網,都難以滿足新的需求 。

處理器匯流排主要用作外部儲存器介面,如德州儀器(TI) C6000系列DSP的外部儲存器介面,可支援外接同步SDRAM、SBSRAM及FIFO,也可支援非同步SRAM、FLASH等。外部儲存器介面也可用作與板內FPGA或ASIC晶片互連,這種情況下,FPGA或ASIC模擬一個DSP支援的儲存器介面,DSP則把FPGA或ASIC當作儲存器來訪問。這類同步介面頻寬可達10Gbps,如德州儀器TMS320C6455 DSP的DDR2介面最大頻寬為17.066Gbps,SBSRAM介面最大頻寬為8.533Gbps。然而,這種介面也存在一些侷限性:

- 介面管腳多,硬體設計困難。常見的DDR2介面有70~80個管腳;

- 只能用於板內互連,無法用於板間互連;

- 不是點對點的對等互連,DSP始終是主裝置,其它器件只能做從裝置。

PCI是廣泛用於計算機內器件互連的技術。傳統PCI技術也取樣類似於上述儲存器介面的並行匯流排方式,如TMS320C6455 DSP的PCI介面,有32bits資料匯流排,最高時鐘速度為66MHz,共有42個管腳。最新的序列PCI Express技術採用與序列RapidIO(SRIO, Serial RapidIO)類似的物理層傳輸技術,使得頻寬達到10Gbps左右。但由於其主要的應用仍是計算機,而且為了相容傳統PCI技術,使得它在嵌入式裝置方面的應用具有一定的侷限性,如不支援點對點對等通訊等。

眾所周知,乙太網是使用最廣泛的區域網互連技術,它也被擴充套件應用到嵌入式裝置互連,但它的侷限性也是顯而易見的:

- 不支援硬體糾錯,軟體協議棧開銷較大;

- 打包效率低,有效傳輸頻寬因此而減小;

- 只支援訊息傳輸模式,不支援對對端裝置的直接儲存器訪問(DMA, Direct Memory Access)。

針對嵌入式系統的需求以及傳統互連方式的侷限性,RapidIO標準按如下目標被制定:

- 針對嵌入式系統機框內高速互連應用而設計。

- 簡化協議及流控機制,限制軟體複雜度,使得糾錯重傳機制乃至整個協議棧易於用硬體實現。

- 提高打包效率,減小傳輸時延。

- 減少管腳,降低成本。

- 簡化交換晶片的實現,避免交換晶片中的包型別解析。

- 分層協議結構,支援多種傳輸模式,支援多種物理層技術,靈活且易於擴充套件。

圖1展示了RapidIO互連在嵌入式系統中的應用。

圖1 RapidIO在嵌入式系統中的應用

表1總結比較了的三種頻寬能達到10Gbps的互連技術:乙太網,PCI Express和序列RapidIO,從中可以看出序列RapidIO是最適合高效能嵌入式系統互連的技術。

表1 10G級互連技術比較

| 軟體實現TCP/IP 協議棧的乙太網 | 4x PCI Express | 4x SRIO | 備註 | |

| 軟體開銷 | 高 | 中 | 低 | SRIO 協議棧簡單,一般都由硬體實現,軟體開銷很小 |

| 硬體糾錯重傳 | 不支援 | 支援 | 支援 | |

| 傳輸模式 | 訊息 | DMA | DMA,訊息 | |

| 拓撲結構 | 任意 | PCI樹 | 任意 | SRIO支援直接點對點或通過交換器件實現的各種拓撲結構 |

| 直接點對點對等互連 | 支援 | 不支援 | 支援 | SRIO互連雙方可對等的發起傳輸。 |

| 傳輸距離 | 長 | 中 | 中 | SRIO針對嵌入式裝置內部互連,傳輸距離一般小於1米 |

| 資料包最大有效載荷長度 | 1500位元組 | 4096位元組 | 256位元組 | 嵌入式通訊系統對實時性要求高,SRIO小包傳輸可減少傳輸時延 |

| 打包效率 (以傳輸256位元組資料為例) | 79% (TCP包) | 82% | 92~94% | 打包效率是有效載荷長度與總包長的比率。SRIO支援多種高效包格式。 |

序列RapidIO協議

RapidIO行業協會成立於2000年,其宗旨是為嵌入式系統開發可靠的,高效能,基於包交換的互連技術。RapidIO協議的簡要發展歷史是:

- 2001年初,最初的標準被髮布

- 2002年6月,1.2版標準釋出

- 2005年6月,1.3版標註釋出

序列RapidIO是物理層採用序列差分模擬訊號傳輸的RapidIO標準。SRIO 1.x 標準支援的訊號速度為1.25GHz、2.5GHz、3.125GHz;正在制定的RapidIO 2.0標準將支援5GHz、6.25GHz.

目前,幾乎所有的嵌入式系統晶片及裝置供應商都加入了RapidIO行業協會。德州儀器(TI) 2001年加入該組織,2003年成為領導委員會成員。2005年底,德州儀器(TI)推出第一個整合SRIO(Serial RapidIO)的DSP,後來又陸續推出共5款支援SRIO的DSP,這使得RapidIO的應用全面啟動。

RapidIO協議結構及包格式

為了滿足靈活性和可擴充套件性的要求,RapidIO協議分為三層:邏輯層、傳輸層和物理層。圖2說明了RapidIO協議的分層結構。

圖2 RapidIO協議分層結構

邏輯層定義了操作協議; 傳輸層定義了包交換、路由和定址機制;物理層定義了電氣特性、鏈路控制和糾錯重傳等。

象乙太網一樣,RapidIO也是基於包交換的互連技術。如圖3所示,RapidIO包由包頭、可選的載荷資料和16bits CRC校驗組成。包頭的長度因為包型別不同可能是十幾到二十幾個位元組。每包的載荷資料長度不超過256位元組,這有利於減少傳輸時延,簡化硬體實現。

圖3 RapidIO包格式

上述包格式定義兼顧了包效率及組包/解包的簡單性。RapidIO交換器件僅需解析前後16bits,以及源/目地器件ID,這簡化了交換器件的實現。

邏輯層協議

邏輯層定義了操作協議和相應的包格式。RapidIO支援的邏輯層業務主要是:直接IO/DMA (Direct IO/Direct Memory Access)和訊息傳遞(Message Passing)。

直接IO/DMA模式是最簡單實用的傳輸方式,其前提是主裝置知道被訪問端的儲存器對映。在這種模式下,主裝置可以直接讀寫從裝置的儲存器。直接IO/DMA在被訪問端的功能往往完全由硬體實現,所以被訪問的器件不會有任何軟體負擔。從功能上講,這一特點和德州儀器DSP的傳統的主機介面(HPI, Host Port Interface)類似。但和HPI口相比,SRIO(Serial RapidIO)頻寬大,管腳少,傳輸方式更靈活。

對上層應用來說,發起直接IO/DMA傳輸主要需提供以下引數:目地器件ID、資料長度、資料在目地器件儲存器中的地址。

直接IO/DMA模式又可進一步分為以下幾種傳輸格式:

- NWRITE: 寫操作,不要求接收端響應。

- NWRITE_R: 帶響應的NWRITE(NWRITE with Response),要求接收端響應。

- SWRITE:流寫(Stream Write),資料長度必須是8位元組的整數倍,不要求接收端響應。

- NREAD: 讀操作。

SWRITE是最高效的傳輸格式;帶響應的寫操作或讀操作效率則較低,一般只能達到不帶響應的傳輸的效率的一半。

訊息傳遞(Message Passing)模式則類似於乙太網的傳輸方式,它不要求主裝置知道被訪問裝置的儲存器狀況。資料在被訪問裝置中的位置則由郵箱號(類似於乙太網協議中的埠號)確定。從裝置根據接收到的包的郵箱號把資料儲存到對應的緩衝區,這一過程往往無法完全由硬體實現,而需要軟體協助,所以會帶來一些軟體負擔。

對上層應用來說,發起訊息傳遞主要需提供以下引數:目地器件ID、資料長度、郵箱號。

表2比較了直接IO/DMA和訊息傳遞模式。

表2 直接IO/DMA和訊息傳遞的對比

| 直接IO/DMA | 訊息傳遞 | |

| 主機可直接訪問從機儲存器? | 可以 | 不可以 |

| 主機需要知道從機儲存器對映? | 需要 | 不需要 |

| 資料定址方式 | 儲存器地址 | 郵箱號 |

| 支援的資料訪問方式 | 讀/寫 | 寫 |

| 從機軟體負擔 | 無 | 有 |

傳輸層協議

RapidIO是基於包交換的互連技術,傳輸層定義了包交換的路由和定址機制。

RapidIO網路主要由兩種器件,終端器件(End Point)和交換器件(Switch)組成。終端器件是資料包的源或目的地,不同的終端器件以器件ID來區分。RapidIO支援8 bits 或 16 bits器件ID,因此一個RapidIO網路最多可容納256或65536個終端器件。與乙太網類似,RapidIO也支援廣播或組播,每個終端器件除了獨有的器件ID外,還可配置廣播或組播ID。交換器件根據包的目地器件ID進行包的轉發,交換器件本身沒有器件ID。

RapidIO的互連拓撲結構非常靈活,除了通過交換器件外,兩個終端器件也可直接互連。以德州儀器(TI)的TMS320C6455 DSP為例,它有4個3.125G的SRIO口,它可支援的拓撲結構如圖4所示。

圖4 RapidIO支援靈活多樣的拓撲結構

物理層協議

RapidIO 1.x 協議定義了以下兩種物理層介面標準:

- 8/16 並行LVDS協議

- 1x/4x 序列協議 (SRIO)

並行RapidIO由於訊號線較多(40~76)難以得到廣泛的應用,而1x/4x序列RapidIO僅4或16個訊號線,逐漸成為主流,所以本文僅介紹序列RapidIO。

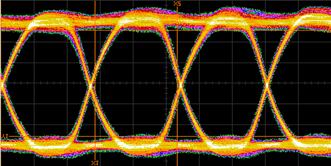

序列RapidIO基於現在已廣泛用於背板互連的SerDes(Serialize Deserialize)技術,它採用差分交流耦合訊號。差分交流耦合訊號具有抗干擾強、速率高、傳輸距離較遠等優點。差分交流耦合訊號的質量不是由傳統的時序引數來衡量,而是通過眼圖來衡量,眼圖中的“眼睛”張得越開則訊號質量越好。圖5是一個典型的序列RapidIO訊號的眼圖。

圖5 序列RapidIO訊號眼圖

差分訊號的強弱由一對訊號線的電壓差值表示,序列RapidIO協議規定訊號峰-峰值的範圍是200mV-2000mV。訊號幅度越大,則傳輸距離越遠,RapidIO協議按訊號傳輸距離定義兩種傳輸指標:

- 短距離傳輸(Short Run),<=50釐米,主要用於板內互連,推薦的傳送端訊號峰-峰值為500mV-1000mV

- 長距離傳輸(Long Run),>50釐米,主要用於板間或背板互連,推薦的傳送端訊號峰-峰值為800mV-1600mV

為了支援全雙工傳輸,序列RapidIO收發訊號是獨立的,所以每一個序列RapidIO口由4根訊號線組成。標準的1x/4x 序列RapidIO介面,支援四個口,共16根訊號線。這四個口可被用作獨立的介面傳輸不同的資料;也可合併在一起當作一個介面使用,以提高單一介面的吞吐量。

德州儀器TMS320C6455 DSP上集成了標準的1x/4x序列RapidIO介面,如圖6所示。

圖6德州儀器TMS320C6455 DSP 1x/4x 序列RapidIO介面框圖

傳送時,邏輯層和傳輸層將組好的包經過CRC編碼後被送到物理層的FIFO中,“8b/10b編碼”模組將每8bit資料編碼成10bits資料,“並/串轉換”模組將10bits並行資料轉換成序列bits,傳送模組把數字bit轉換成差分交流耦合訊號在訊號線上傳送出去。這裡的8b/10編碼的主要作用是:

- 保證訊號有足夠的跳變,以便於接收方恢復時鐘。序列RapidIO沒有專門的時鐘訊號線,接收端靠資料訊號的跳變恢復時鐘。所以需要把訊號跳變少的8bits資料(如全0或全1)編碼成有一定跳變的10bits資料。另外,也使得總體資料中0和1的個數均衡,以消除直流分量,保證交流耦合特性;

- 8b/10編碼可擴大符號空間,以承載帶內控制符號。10bits能表示1024個符號,其中256個表示有效的8bits資料,剩下的符號中的幾十個被用作控制符號。控制符號可被用作包分隔符,響應標誌,或用於鏈路初始化,鏈路控制等功能;

- 8b/10編碼能實現一定的檢錯功能。1024個符號中,除了256個有效資料符號和幾十個控制符號外,其它符號都是非法的,接收方收到非法符號則表示鏈路傳輸出錯。

接收的過程則正好相反,首先接收方需要根據資料訊號的跳變恢復出時鐘,用這個時鐘取樣序列訊號,將序列訊號轉換為10bits的並行訊號,再按8b/10b編碼規則解碼得到8bits資料,最後做CRC校驗並送上層處理。

資料被正確的接收時,接收端會發送一個ACK響應包給傳送端;如果資料不正確(CRC錯或非法的10bits符號),則會送NACK包,要求傳送方重傳。這種重傳糾錯的功能由物理層完成,而物理層功能往往由硬體實現,所以不需要軟體干預。

序列RapidIO支援的訊號速率有三種:1.25GHz,2.5GHz,3.125GHz。但由於8b/10b編碼,其有效資料速率分別為:1Gbps, 2Gbps, 2.5Gbps。 4個1x埠或一個4x埠支援的最高速率為10Gbps。

序列RapidIO在無線基礎設施上的應用

無線基礎設施如基站、媒體閘道器等,是典型的高效能嵌入式通訊系統,它們對互連的頻寬、時延、複雜度、靈活性、可靠性都有非常高的要求。而序列RapidIO正是滿足這些要求的最佳選擇。

以無線基站為例,在SRIO出現之前,無線基站的基帶處理的典型框圖如圖7所示。

圖7 傳統無線基站基帶處理框圖

在傳統的基站中,DSP與ASIC或FPGA之間的互連一般用外部儲存器介面EMIF(External Memory Interface);DSP之間或DSP與主機之間一般用HPI(Host Port Interface)或PCI互連。它們的主要缺點是:頻寬小;訊號線多;主從模式介面,不支援對等傳輸。另外,DSP不能直接進行背板傳輸。

使用SRIO(Serial RapidIO)則可有效的解決這些問題,大大提高無線基站的互連效能。圖8顯示了一種無線基站基帶互連框圖。在這裡,SRIO實現了大部分器件之間的互連,甚至可支援DSP進行直接背板傳輸。

圖8 SRIO提高無線基站互連效能

通過SRIO交換器件互連可以進一步提高基帶處理的靈活性,圖9顯示了一種基帶SRIO交換互連的框圖。這種互連有利於實現先進的基帶處理資源池架構,資料可被送到任何一個通過SRIO交換器互連的處理器中,從而達到各個處理器的負載均衡,更加有效的利用系統的整體處理能力。

圖9 SRIO交換為無線基站基帶處理提供更大的靈活性

綜上所述,對嵌入式系統尤其是無線基礎設施,序列RapidIO是最佳的互連技術。高達10Gbps的頻寬、低時延和低軟體複雜度滿足了飛速發展的通訊技術對效能的苛刻需求;序列差分模擬訊號技術滿足了系統對管腳數量的限制,及對背板傳輸的需求;靈活的點對點對等互連、交換互連,和可選的1.25G/2.5G/3.125G三種速度能滿足多種不同應用的需求。

隨著序列RapidIO技術的發展成熟,以及越來越多的廠商的支援,序列RapidIO技術必將成為高效能嵌入式互連的主流技術。

相關推薦

【DSP開發】序列 RapidIO: 高效能嵌入式互連技術

作者: 德州儀器技術應用工程師 馮華亮/ Brighton Feng/ [email protected] 摘要 序列RapidIO針對高效能嵌入式系統晶片間和板間互連而設計,它將是未來十幾年中嵌入式系統互連的最佳選擇。 本文比較RapidIO和傳統互連技術的優點;介紹RapidIO協議架構,包格式

【DSP開發】TI SYS/BIOS的 建立工程例項

SYS/BIOS是一個可擴充套件的實時核心(或者說是作業系統),其提供了許多模組化的APIs(應用程式介面),支援搶佔式多執行緒,硬體抽象,實時分析和配置工具,其設計目的是為了最大限度地減少對記憶體和CPU的要求。其擁有很多實時嵌入式作業系統的功能,如任務的排程,任務間的同步和通訊,記憶體管理

【DSP開發】C6678的中斷控制器

分兩層,一層是每個core內部的中斷控制器,這個叫interrupt controller,簡寫intc;一層是整個晶片的,屬於晶片級的,在每個core的外面,這個叫chip-level interrupt controller,縮寫CIC。 分兩層其實兩層功能也不同

【DSP開發】TMS320C66x DSP SPI Nor Flash的程式燒寫

經過一段時間的研究終於把TMS320C6657單核和雙核的SPI Nor Flash的程式燒寫調通了。工具都是前輩的工作,有需要的可以留下郵箱,我有空可以發。 原理參考錢豐的《TI c66x 系列DSP 多核BOOT 的研究》論文。 通過Nor flash 燒寫載入程

【ARM-Linux開發】【DSP開發】AM5728介紹

AM5728 Sitara Processors 1.介紹 1.1AM572x概述 AM572x是高效能,Sitara器件、以28nm技術整合: 結構設計主要考慮嵌入式應用,包括工業通訊,人機介面(HMI),自動化控制,其它

【移動開發】關於一對一視訊聊天直播技術(七):直播雲 SDK 效能測試模

本篇是《一對一視訊直播技術詳解》系列的最後一篇直播雲 SDK 效能測試模型,SDK 的效能對最終 App 的影響非常大。SDK 版本迭代快速,每次釋出前都要進行系統的測試,測試要有比較一致的行為,要有效能模型作為理論基礎,對 SDK 的效能做量化評估。本文就是來探討影響 SDK 效能的指標並建立相應的效能模型

【BZOJ1283/3550】序列/[ONTAK2010]Vacation 最大費用流

元素 set 字符串表 選擇 stream des namespace mil cst 【BZOJ1283】序列 Description 給出一個長度為 的正整數序列Ci,求一個子序列,使得原序列中任意長度為 的子串中被選出的元素不超過K(K,M<=100) 個,

【遊戲開發】淺談遊戲開發中常見的設計原則

依賴關系 unity 說過 srp des log gof https 類繼承 俗話說得好:“設計模式,常讀常新~”。的確,每讀一遍設計模式都會有些新的體會和收獲。馬三不才,才讀了兩遍設計模式(還有一遍是在學校學的),屬於菜鳥級別的。這次準備把閱

【Web開發】Mean web開發 01-Express實現MVC模式開發

http scripts send javascrip 模板引擎 指令 開發環境 depend filter 簡介 Mean是JavaScript的全棧開發框架。更多介紹 用Express實現MVC模式開發是Mean Web全棧開發中的一部分。 Express 是一個基於

【Android開發】之Fragment與Acitvity通信

對象 p s ets roi mit blog () open findview 上一篇我們講到與Fragment有關的經常使用函數,既然Fragment被稱為是“小Activity”。如今我們來講一下Fragment怎樣與Acitivity通信。

【Android開發】找樂,一個笑話App的制作過程記錄

override pbo rdm data root 恰恰 功能 sql htm 緣起 想做一個笑話App的原因是由於在知乎上看過一個帖子。做Android能夠有哪些數據能夠練手,裏面推薦了幾個數據開放平臺。在這些平臺中無一不是有公共的笑話接口,當時心

【遊戲開發】Excel表格批量轉換成CSV的小工具

作用 span all 腳本開發 class lob 索引 之前 並保存 一、前言 在工作的過程中,我們有時可能會面臨將Excel表格轉換成CSV格式文件的需求。這尤其在遊戲開發中體現的最為明顯,策劃的數據文檔大多是一些Excel表格,且不說這些表格在遊戲中讀取的速度

【設計開發】 Linux C文件創建Open函數

include == code pan lin his class trunc types.h #include <sys/types.h> #include <sys/stat.h> #include <fcntl.h>

【敏捷開發】經驗構件庫-Java版(exp-libs)

完整原文(含原始碼):http://exp-blog.com/2018/09/22/pid-2382/ (轉載請註明出處,僅供分享學習,嚴禁用於商業用途) 環境 簡介 此構件庫為本人多年程式設計總結提煉而成,把常用的功能模組作為原子API

【VS開發】Visual Studio 2015 無法解析的外部的符號 __vsnwprintf_s

IDE:Visual Studio 2015 作業系統:win 10 問題: 編譯的時候可能會遇到 ERROR LNK2019:無法解析的外部的符號 __vsnwprintf_s,或者是_sscanf,_sscanf_s等等一系列形如這樣的函式 疑

【VS開發】/FORCE(強制檔案輸出)

/FORCE:[MULTIPLE|UNRESOLVED] 備註 即使引用了符號但未定義或多次定義符號,/FORCE 選項也通知連結器建立有效的 .exe

【VS開發】VS編譯時提示"已經在 LIBCMT.lib(new.obj) 中定義uafxcw.lib"解決辦法

錯誤 1 error LNK2005: "void * __cdecl operator new(unsigned int)" ( [email protected]@Z )

【移動開發】關於一對一視訊交友直播(五)延遲優化

6 月底釋出了一個針對視訊直播的實時流網路 LiveNet 和完整的直播雲解決方案,很多開發者對這個網路和解決方案的細節和使用場景非常感興趣。 結合實時流網路 LiveNet 和直播雲解決方案的實踐,我們用一系列文章,更系統化地介紹當下大熱的視訊直播各環節的關鍵技術,幫助視訊直播創業者們更全面、深入地瞭解視

【移動開發】關於一對一視訊交友技術原始碼(六)現代播放器原理

在上一篇延遲優化中,我們分享了不少簡單實用的調優技巧。本篇是《一對一視訊直播技術詳解》系列之六:現代播放器原理。 近年來,多平臺適配需求的增長導致了流媒體自適應位元速率播放的興起,這迫使 Web 和移動開發者們必須重新思考視訊技術的相關邏輯。首先,巨頭們分分發布了 HLS、HDS 和 Smooth Stre

【Qt開發】QThread中的互斥、讀寫鎖、訊號量、條件變數

在gemfield的《從pthread到QThread》一文中我們瞭解了執行緒的基本使用,但是有一大部分的內容當時說要放到這片文章裡討論,那就是執行緒的同步問題。關於這個問題,gemfield在《從進 程到執行緒》中有一個比喻,有必要重新放在下面溫習下: ***************