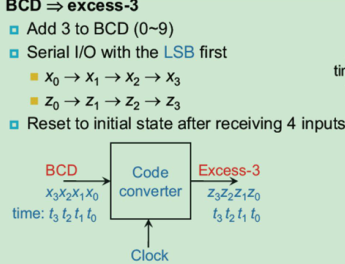

8421BCD轉餘3碼Verilog HDL的設計(1)

近期閱讀Verilog HDL高階數字設計(第二版)中,遇到了序列位元流BCD碼轉餘3碼轉換器的設計,比較獨特的是:

(1)該轉換器的輸入為1位序列位元流,輸出也為1位序列位元流。

BCD碼與餘三碼的轉換關係如下:

8421BCD碼=餘3碼+0011

| 10進位制 | 8421BCD碼 | 餘3碼 | 10進位制 | 8421BCD碼 | 餘3碼 |

| 0 | 0000 | 0011 | 8 | 1000 | 1011 |

| 1 | 0001 | 0100 | 9 | 1001 | 1100 |

| 2 | 0010 | 0101 | 10 | 1010 | 1101 |

| 3 | 0011 | 0110 | 11 | 1011 | 1110 |

| 4 | 0100 | 0111 | 12 | 1100 | 1111 |

| 5 | 0101 | 1000 | 13 | 1101 | 10000 |

| 6 | 0110 | 1001 | 14 | 1110 | 10001 |

| 7 | 0111 | 1010 | 15 | 1111 | 10010 |

由表1可知,當8421BCD碼為13、14、15時候,餘三碼已經超出了4位二進位制能表示的範圍(無符號數0~15),因此本次中暫不考慮。

轉換器的輸入為1位序列位元流,輸出為1位相應餘三碼的序列位元流,設計思路如下:

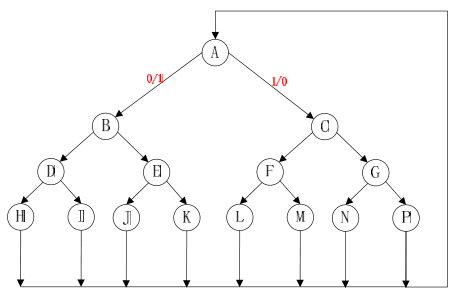

圖1 狀態轉換示意圖

設BCD碼輸入位元流Bin在t0,t1,t2,t3的輸入分別為t0t1t2t3,設餘三碼輸出位元流Bout在t0,t1,t2,t3時刻的輸出分別為T0T1T2T3

假設轉換器的初始狀態為狀態A:

(1)在狀態A下,t0時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入B狀態;當bin輸入1時,進入C狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

A狀態(t0時刻,Bin=0),Bout=1 |

A狀態(t0時刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:B | t3t2t1t0 | T3T2T1T0 | 下一個狀態:C |

| 0000 | 0011 | 0001 | 0010 | ||

| 0010 | 0101 | 0011 | 0110 | ||

| 0100 | 0111 | 0101 | 1000 | ||

| 0110 | 1001 | 0111 | 1010 | ||

| 1000 | 1011 | 1001 | 1100 | ||

| 1010 | 1101 | 1011 | 1110 | ||

| 1100 | 1111 | 1101 | (1)0000 | ||

(2)在B狀態,t1時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入D狀態;當bin輸入1時,進入E狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

B狀態(t1時刻,Bin=0),Bout=1 |

B狀態(t1時刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:D | t3t2t1t0 | T3T2T1T0 | 下一個狀態:E |

| 0000 | 0011 | 0010 | 0101 | ||

| 0100 | 0111 | 0110 | 1001 | ||

| 1000 | 1011 | 1010 | 1101 | ||

| 1100 | 1111 | 1110 | (1)0001 | ||

(3)在D狀態,t2時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入H狀態;當bin輸入1時,進入I狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

D狀態(t2時刻,Bin=0),Bout=0 |

E狀態(t2時刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:H | t3t2t1t0 | T3T2T1T0 | 下一個狀態:I |

| 0000 | 0011 | 0100 | 0111 | ||

| 1000 | 1011 | 1100 | 1111 | ||

(4)在H狀態,t3時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入A狀態;當bin輸入1時,進入A狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

H狀態(t3時刻,Bin=0),Bout=0 |

H狀態(t3時刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:A | t3t2t1t0 | T3T2T1T0 | 下一個狀態:A |

| 0000 | 0011 | 1000 | 1011 | ||

(5)在I狀態,t3時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入A狀態;當bin輸入1時,進入A狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

I狀態(t3時刻,Bin=0),Bout=0 |

I狀態(t3時刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:A | t3t2t1t0 | T3T2T1T0 | 下一個狀態:A |

| 0100 | 0111 | 1100 | 1111 | ||

(6)在E狀態,t2時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入J狀態;當bin輸入1時,進入K狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

E狀態(t2時刻,Bin=0),Bout=1 |

E狀態(t2時刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:J | t3t2t1t0 | T3T2T1T0 | 下一個狀態:K |

| 0010 | 0101 | 0110 | 1001 | ||

| 1010 | 1101 | 1110 | (1)0001 | ||

(7)在J狀態,t3時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入A狀態;當bin輸入1時,進入A狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

J狀態(t3時刻,Bin=0),Bout=0 |

J狀態(t3時刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:A | t3t2t1t0 | T3T2T1T0 | 下一個狀態:A |

| 0010 | 0101 | 1010 | 1101 | ||

(8)在K狀態,t3時刻Bin輸入的值可能為0或者1:當bin輸入0時,進入A狀態;當bin輸入1時,進入A狀態

位元流Bin二進位制為t3t2t1t0的可能性如下:

|

K狀態(t3時刻,Bin=0),Bout=1 |

K狀態(t3時刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一個狀態:A | t3t2t1t0 | T3T2T1T0 | 下一個狀態:A |

| 0110 | 1001 | 1110 | (1)0001 | ||

未完待續。